Xilinx Uio Example . In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. Make sure that the irq is registered: Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. For information on how to do this, see the axi_gpio product guide from xilinx. I think that would be simpler than defining your own kernel. To test, make sure that the uio is probed: Note that it will also be up to you to properly reset. You should see that the uio0 is listed here. By exploring all the uio name in sysfs, one can map uio device with correct pl core.

from blog.idv-tech.com

Make sure that the irq is registered: Note that it will also be up to you to properly reset. To test, make sure that the uio is probed: For information on how to do this, see the axi_gpio product guide from xilinx. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. You should see that the uio0 is listed here. I think that would be simpler than defining your own kernel. By exploring all the uio name in sysfs, one can map uio device with correct pl core. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few.

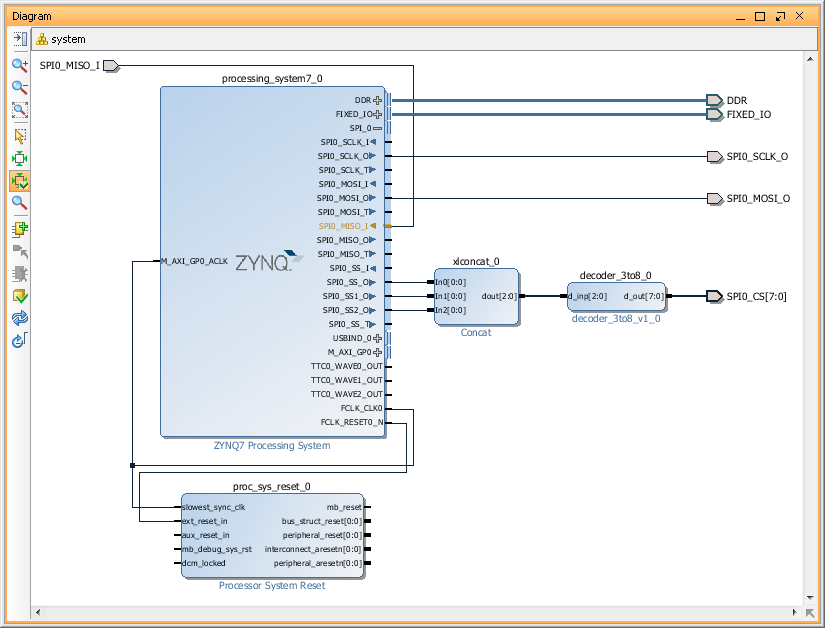

Howto create and package IP using Xilinx Vivado 2014.1 d9 Tech Blog

Xilinx Uio Example Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. I think that would be simpler than defining your own kernel. You should see that the uio0 is listed here. By exploring all the uio name in sysfs, one can map uio device with correct pl core. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. Note that it will also be up to you to properly reset. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. To test, make sure that the uio is probed: Make sure that the irq is registered: For information on how to do this, see the axi_gpio product guide from xilinx.

From www.raypcb.com

How to design Xilinx Versal and its essential architecture RAYPCB Xilinx Uio Example In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. Make sure that the irq is registered: I think that would be simpler than defining your own kernel. You should see that the uio0 is listed here. For information on how to do this, see the axi_gpio product guide. Xilinx Uio Example.

From www.prnewswire.com

Xilinx Unveils Disruptive Integration and Architectural Breakthrough Xilinx Uio Example You should see that the uio0 is listed here. For information on how to do this, see the axi_gpio product guide from xilinx. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. Note that it will also be up to you to properly reset. To test, make sure that the uio is probed:. Xilinx Uio Example.

From xilinx.github.io

Xilinx Design Constraints FPGA Design with Vivado Xilinx Uio Example By exploring all the uio name in sysfs, one can map uio device with correct pl core. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. I've been investigating the different options. Xilinx Uio Example.

From fpga.eetrend.com

Xilinx 7系列FPGA架构之SelectIO结构(一) FPGA 开发圈 Xilinx Uio Example For information on how to do this, see the axi_gpio product guide from xilinx. To test, make sure that the uio is probed: You should see that the uio0 is listed here. I think that would be simpler than defining your own kernel. Note that it will also be up to you to properly reset. Make sure that the irq. Xilinx Uio Example.

From fpga.eetrend.com

Xilinx 7系列FPGA架构之SelectIO结构(一) FPGA 开发圈 Xilinx Uio Example By exploring all the uio name in sysfs, one can map uio device with correct pl core. You should see that the uio0 is listed here. To test, make sure that the uio is probed: I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. Using gpios, timers, and. Xilinx Uio Example.

From fpgasite.blogspot.com

Xilinx AXI Stream tutorial Part 1 Xilinx Uio Example You should see that the uio0 is listed here. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. For information on how to do this, see the axi_gpio product guide from xilinx. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some.. Xilinx Uio Example.

From allaboutfpga.com

Working with Xilinx ISE Software Xilinx Uio Example To test, make sure that the uio is probed: In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. For information on how to do this, see the axi_gpio product guide from xilinx. I've been investigating the different options for interacting with the pl from the ps running linux. Xilinx Uio Example.

From www.techway.com

Robust and lasting solution Design confidently with our Xilinx Kintex Xilinx Uio Example By exploring all the uio name in sysfs, one can map uio device with correct pl core. You should see that the uio0 is listed here. For information on how to do this, see the axi_gpio product guide from xilinx. Note that it will also be up to you to properly reset. I've been investigating the different options for interacting. Xilinx Uio Example.

From painlessdev.blogspot.com

PainlessDev Petalinux From Scratch (Xilinx MPSoC ZCU102) Create UIO Xilinx Uio Example By exploring all the uio name in sysfs, one can map uio device with correct pl core. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. To test, make sure that the uio is probed: Make sure that the irq is registered: You should see that the uio0. Xilinx Uio Example.

From blog.idv-tech.com

Howto create and package IP using Xilinx Vivado 2014.1 d9 Tech Blog Xilinx Uio Example I think that would be simpler than defining your own kernel. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. Make sure that the irq is registered: For information on how to do this, see the axi_gpio product guide from xilinx. Using gpios, timers, and interrupts¶ the zynq®. Xilinx Uio Example.

From xilinx.github.io

Xilinx Design Constraints FPGA Design with Vivado Xilinx Uio Example For information on how to do this, see the axi_gpio product guide from xilinx. Note that it will also be up to you to properly reset. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. I think that would be simpler than defining your own kernel. You should. Xilinx Uio Example.

From mushiming.com

ZYNQ中的UIO驱动和中断程序学习【XilinxPetalinux学习】 穆世明博客 Xilinx Uio Example In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. Note that it will also be up to you to properly reset. You should see that the uio0 is listed here. To test, make sure that the uio is probed: I think that would be simpler than defining your. Xilinx Uio Example.

From www.researchgate.net

6 Basic Architecture of a Xilinx FPGA Download Scientific Diagram Xilinx Uio Example By exploring all the uio name in sysfs, one can map uio device with correct pl core. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. Note that it will also be up to you to properly reset. To test, make sure that the uio is probed: You. Xilinx Uio Example.

From www.youtube.com

Easy Tutorial on FPGA Coding by Using Vivado, Verilog, and Xilinx Xilinx Uio Example Make sure that the irq is registered: Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. To test, make sure that the uio is probed: Note that it will also be up to you to properly reset. For information on how to do this, see the axi_gpio product guide from xilinx. I've been. Xilinx Uio Example.

From www.researchgate.net

Xilinx system generator design steps Download Scientific Diagram Xilinx Uio Example You should see that the uio0 is listed here. Note that it will also be up to you to properly reset. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. By exploring all the uio name in sysfs, one can map uio device with correct pl core. To. Xilinx Uio Example.

From blog.csdn.net

Xilinx7系列器件的IO逻辑资源(一)_xilinx ioCSDN博客 Xilinx Uio Example Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. You should see that the uio0 is listed here. Note that it will also be up to you to properly reset. To test, make sure that the uio is probed: Make sure that the irq is registered: By exploring all the uio name in. Xilinx Uio Example.

From conduant.com

Xilinx® Aurora Recording With StreamStor® Conduant Corporation Xilinx Uio Example By exploring all the uio name in sysfs, one can map uio device with correct pl core. I think that would be simpler than defining your own kernel. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. Note that it will also be up to you to properly reset. You should see that. Xilinx Uio Example.

From www.embedded.com

Xilinx boosts RFSoC performance with digitalfrontend hard IP for 5G Xilinx Uio Example In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. To test, make sure that the uio is probed: For information on how to do this, see the axi_gpio product guide from xilinx. I've been investigating the different options for interacting with the pl from the ps running linux. Xilinx Uio Example.

From www.xilinx.com

Design Entry & Implementation Xilinx Uio Example Note that it will also be up to you to properly reset. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. To test, make sure that the uio is probed: I've been investigating the different options for interacting with the pl from the ps running linux and have. Xilinx Uio Example.

From www.researchgate.net

The internal structure of the Xilinx XC4000 FPGA architecture devices Xilinx Uio Example I think that would be simpler than defining your own kernel. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. Make sure that the irq is registered: Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. To test, make sure that. Xilinx Uio Example.

From device.report

MICROCHIP Xilinx Spartan 6 Example Conversion User Guide Xilinx Uio Example To test, make sure that the uio is probed: For information on how to do this, see the axi_gpio product guide from xilinx. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. You should see that the uio0 is listed here. Make sure that the irq is registered:. Xilinx Uio Example.

From www.entegra.co.uk

Xilinx® Zynq® UltraScale+ MPSoC Module Entegra Xilinx Uio Example In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. By exploring all the uio name in sysfs, one can map uio device with correct pl core. You should see that the uio0 is listed here. To test, make sure that the uio is probed: For information on how. Xilinx Uio Example.

From www.cs.ucr.edu

Xilinx Intro Xilinx Uio Example For information on how to do this, see the axi_gpio product guide from xilinx. I think that would be simpler than defining your own kernel. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. You should see that the uio0 is listed here. To test, make sure that. Xilinx Uio Example.

From www.youtube.com

Simulation procedure of Verilog Code in Xilinx YouTube Xilinx Uio Example For information on how to do this, see the axi_gpio product guide from xilinx. I think that would be simpler than defining your own kernel. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. Note that it will also be up to you to properly reset. In this blog, i will showcase a. Xilinx Uio Example.

From www.slideserve.com

PPT LAB 3 Finite State Machines On Xilinx PowerPoint Presentation Xilinx Uio Example In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. To test, make sure that the uio is probed: I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. For information on how to do this, see the. Xilinx Uio Example.

From www.youtube.com

Xilinx ISE adding User Constraint File and creating a bit file for FPGA Xilinx Uio Example For information on how to do this, see the axi_gpio product guide from xilinx. Make sure that the irq is registered: In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. Note that it will also be up to you to properly reset. I think that would be simpler. Xilinx Uio Example.

From zhuanlan.zhihu.com

xilinx:Linux 下,通过 UIO 监控 PL 给到 PS 的中断 知乎 Xilinx Uio Example Note that it will also be up to you to properly reset. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. You should see that the uio0 is listed here. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. I've been. Xilinx Uio Example.

From www.cs.ucr.edu

Xilinx Intro Xilinx Uio Example I think that would be simpler than defining your own kernel. By exploring all the uio name in sysfs, one can map uio device with correct pl core. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. Make sure that the irq is registered: In this blog, i will showcase a simple led. Xilinx Uio Example.

From www.researchgate.net

Functional block diagram of the MPSoC Xilinx Zynq Ultrascale+ EG Xilinx Uio Example You should see that the uio0 is listed here. Note that it will also be up to you to properly reset. To test, make sure that the uio is probed: By exploring all the uio name in sysfs, one can map uio device with correct pl core. For information on how to do this, see the axi_gpio product guide from. Xilinx Uio Example.

From www.slideshare.net

Xilinx lca and altera flex Xilinx Uio Example I think that would be simpler than defining your own kernel. To test, make sure that the uio is probed: Make sure that the irq is registered: For information on how to do this, see the axi_gpio product guide from xilinx. By exploring all the uio name in sysfs, one can map uio device with correct pl core. Using gpios,. Xilinx Uio Example.

From www.youtube.com

Tutorial 2 How to create testbench and simulate design in Xilinx Vivado Xilinx Uio Example You should see that the uio0 is listed here. Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. By exploring all the uio name in sysfs, one can map uio device with correct pl core. I've been investigating the different options for interacting with the pl from the ps running linux and have. Xilinx Uio Example.

From www.youtube.com

Xilinx Vivado 基礎操作 Xilinx Vivado Basic Flow YouTube Xilinx Uio Example I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device. Make sure that the irq is registered: You should see that the uio0 is listed here. Using gpios,. Xilinx Uio Example.

From www.youtube.com

Xilinx ISE Verilog Tutorial 02: Simple Test Bench YouTube Xilinx Uio Example Make sure that the irq is registered: You should see that the uio0 is listed here. For information on how to do this, see the axi_gpio product guide from xilinx. To test, make sure that the uio is probed: In this blog, i will showcase a simple led toggling application run on a linux kernel on a zynq® ultrascale™ device.. Xilinx Uio Example.

From www.youtube.com

Xilinx (Verilog) Tutorial for beginners YouTube Xilinx Uio Example Using gpios, timers, and interrupts¶ the zynq® ultrascale+™ mpsoc zcu102 evaluation board comes with a few. I've been investigating the different options for interacting with the pl from the ps running linux and have been having some. I think that would be simpler than defining your own kernel. For information on how to do this, see the axi_gpio product guide. Xilinx Uio Example.

From xilinx.github.io

Xilinx Design Constraints FPGA Design with Vivado Xilinx Uio Example I think that would be simpler than defining your own kernel. Make sure that the irq is registered: By exploring all the uio name in sysfs, one can map uio device with correct pl core. Note that it will also be up to you to properly reset. I've been investigating the different options for interacting with the pl from the. Xilinx Uio Example.