Digital Phase Locked Loop Verilog Code . Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Historically pll’s were analog components. The design includes a systemverilog testbench demonstrating a full. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The pll comprises three blocks each of which is implemented with a. The topology used a vco,. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal.

from eureka.patsnap.com

Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The pll comprises three blocks each of which is implemented with a. The design includes a systemverilog testbench demonstrating a full. Historically pll’s were analog components. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,.

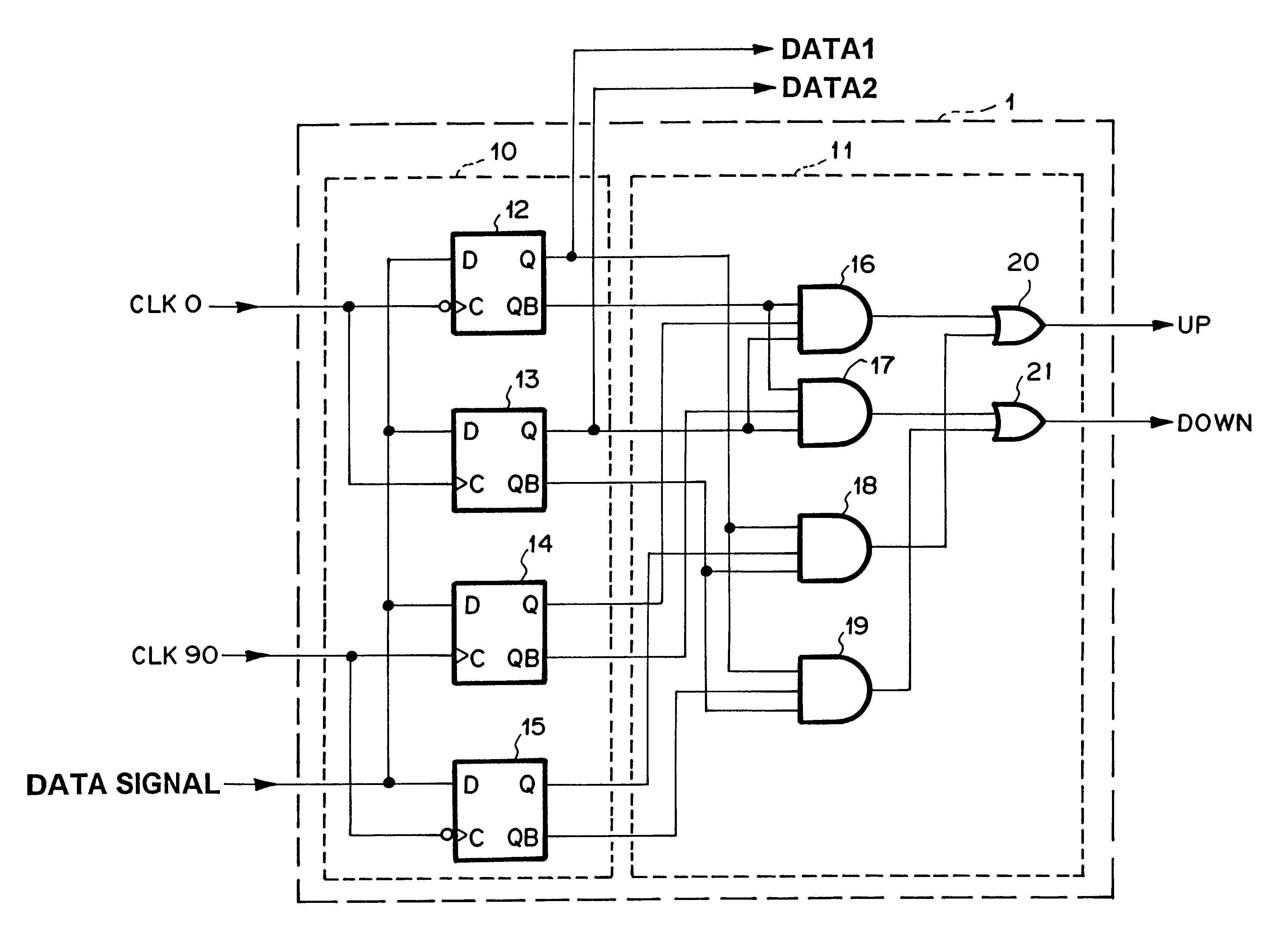

Two phase digital phase locked loop circuit Eureka Patsnap

Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. The topology used a vco,. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal.

From zhuanlan.zhihu.com

Chapter 19 Digital PhaseLocked Loops 知乎 Digital Phase Locked Loop Verilog Code Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The pll comprises three blocks each of which is implemented. Digital Phase Locked Loop Verilog Code.

From www.mathworks.com

Modeling and Simulating an AllDigital Phase Locked Loop MATLAB Digital Phase Locked Loop Verilog Code The design includes a systemverilog testbench demonstrating a full. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Phase locked loops are a control system that generates an. Digital Phase Locked Loop Verilog Code.

From www.slideshare.net

All Digital Phase Lock Loop 03 12 09 Digital Phase Locked Loop Verilog Code The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The topology used a vco,. Phase locked loops are a control system that generates an output signal whose. Digital Phase Locked Loop Verilog Code.

From www.youtube.com

Phase Locked Loop Tutorial the basics of PLLs YouTube Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Phase locked loops are a control system that generates an output signal whose phase. Digital Phase Locked Loop Verilog Code.

From www.youtube.com

VelTech University_Design Of All Digital Phase Locked Loop As A Digital Phase Locked Loop Verilog Code Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The pll comprises three blocks each of which is implemented with a. The design includes a systemverilog testbench demonstrating a full. Historically pll’s were. Digital Phase Locked Loop Verilog Code.

From www.researchgate.net

Block diagram of All Digital Phase Locked Loop CORDIC can be used in Digital Phase Locked Loop Verilog Code Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the. Digital Phase Locked Loop Verilog Code.

From www.mdpi.com

Electronics Free FullText Design and Emulation of AllDigital Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The pll comprises three blocks each of which is implemented with a. The topology used a vco,. Historically pll’s were analog components. Phase locked loops are a control system that generates an output signal whose. Digital Phase Locked Loop Verilog Code.

From www.scribd.com

Lecture 070 Digital Phase Lock Loops (DPLL) Digital Phase Locked Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The pll comprises three blocks each of which is implemented with a. The topology used a vco,. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The design. Digital Phase Locked Loop Verilog Code.

From dokumen.tips

(PPT) ADPLLAllDigitalPhaseLockedLoopCircuits.ppt DOKUMEN.TIPS Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The design includes a systemverilog testbench demonstrating a full. The topology used a vco,. Throughout the series, we will examine how an fpga works as well as. Digital Phase Locked Loop Verilog Code.

From www.semanticscholar.org

Verilog Design of AllDigital PhaseLocked Loop with TwoCycle Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. The topology used a vco,. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Historically pll’s. Digital Phase Locked Loop Verilog Code.

From www.mdpi.com

Electronics Free FullText Design and Emulation of AllDigital Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks. Digital Phase Locked Loop Verilog Code.

From www.mdpi.com

Electronics Free FullText Design and Emulation of AllDigital Digital Phase Locked Loop Verilog Code Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of. Digital Phase Locked Loop Verilog Code.

From www.academia.edu

(PDF) Modeling PhaseLocked Loops Using Verilog Jeffrey Meyer Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The pll comprises three blocks each of which is implemented. Digital Phase Locked Loop Verilog Code.

From studylib.net

Tutorial on Digital PhaseLocked Loops Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Historically pll’s were analog components. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Is there any straight forward way to implement an all. Digital Phase Locked Loop Verilog Code.

From www.mdpi.com

Electronics Free FullText Design and Emulation of AllDigital Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The topology used a vco,. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The design includes a systemverilog testbench demonstrating a full.. Digital Phase Locked Loop Verilog Code.

From www.yumpu.com

Design of All Digital Phase Locked Loop in VHDL Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. The design includes a systemverilog testbench demonstrating a full. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,. Is there any straight forward way to implement an all digital phase lock in. Digital Phase Locked Loop Verilog Code.

From eureka.patsnap.com

Threephase digital phaselocked loop and phase lock method Eureka Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The design includes a systemverilog testbench demonstrating a full. The topology used a vco,. Is there any straight forward way to implement an all digital phase lock in. Digital Phase Locked Loop Verilog Code.

From eureka.patsnap.com

Two phase digital phase locked loop circuit Eureka Patsnap Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. The topology used a vco,. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The design includes a systemverilog testbench demonstrating a full. Historically pll’s were analog components. Throughout the series, we will examine how an fpga works as well as. Digital Phase Locked Loop Verilog Code.

From www.analog.com

PhaseLocked Loop (PLL) Fundamentals Analog Devices Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The design includes a systemverilog testbench demonstrating a full. The topology used a vco,. Historically pll’s were analog components. Phase locked loops are a control system that generates an output signal whose. Digital Phase Locked Loop Verilog Code.

From blog.csdn.net

Chapter 19 Digital PhaseLocked Loops_锁相环pull in range和pull out range Digital Phase Locked Loop Verilog Code The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,. Is there any straight forward way to implement an. Digital Phase Locked Loop Verilog Code.

From eureka.patsnap.com

Digital phase locked loop and operating method of digital phase locked Digital Phase Locked Loop Verilog Code The topology used a vco,. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Historically pll’s were analog components. The design includes a systemverilog. Digital Phase Locked Loop Verilog Code.

From www.semanticscholar.org

Verilog Design of AllDigital PhaseLocked Loop with TwoCycle Digital Phase Locked Loop Verilog Code The topology used a vco,. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Historically pll’s were analog components. Throughout the series, we will examine how an fpga works as well as demonstrate. Digital Phase Locked Loop Verilog Code.

From github.com

GitHub Ghanshu03101997/ImplementationofDigitalPhaseLockedLoop Digital Phase Locked Loop Verilog Code The topology used a vco,. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Historically pll’s were analog components. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The pll comprises three blocks. Digital Phase Locked Loop Verilog Code.

From fr.slideshare.net

Fpga implementation of power efficient all digital phase locked loop Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Historically pll’s were analog components. The design includes a systemverilog testbench demonstrating a full. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Is. Digital Phase Locked Loop Verilog Code.

From www.slideshare.net

Digital Phase Locked Loop Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The design includes a systemverilog testbench demonstrating a full. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using. Digital Phase Locked Loop Verilog Code.

From www.researchgate.net

(PDF) FPGA Based Digital Phase Locked Loop using VHDL Coding Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The topology used a vco,. The design includes a systemverilog testbench demonstrating a full. Is there any straight forward way to implement an. Digital Phase Locked Loop Verilog Code.

From www.mdpi.com

Electronics Free FullText Design and Emulation of AllDigital Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,. The design includes a systemverilog testbench demonstrating a full. The. Digital Phase Locked Loop Verilog Code.

From zhuanlan.zhihu.com

Chapter 19 Digital PhaseLocked Loops 知乎 Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Phase locked loops are a control system that generates. Digital Phase Locked Loop Verilog Code.

From enlightensolarpower.com

How a digital phase locked loop works PV on Grid Solar Power Technology Digital Phase Locked Loop Verilog Code The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. Throughout the series, we will examine how. Digital Phase Locked Loop Verilog Code.

From www.researchgate.net

Alldigital phaselocked loop, used to lock the DPWM switching Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The topology used a vco,. The design includes a systemverilog. Digital Phase Locked Loop Verilog Code.

From www.youtube.com

Digital Phase Locked Loop + Python Testing YouTube Digital Phase Locked Loop Verilog Code Phase locked loops are a control system that generates an output signal whose phase is related to the input signal. The pll comprises three blocks each of which is implemented with a. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The topology used a vco,. Historically pll’s were analog components. The design. Digital Phase Locked Loop Verilog Code.

From eureka.patsnap.com

Method for digital phaselocked loop and burr elimination Eureka Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. The topology used a vco,. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Phase locked loops are a control system that generates. Digital Phase Locked Loop Verilog Code.

From www.semanticscholar.org

[PDF] Improved Phase Detection for Digital Phaselocked Loops Digital Phase Locked Loop Verilog Code Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The topology used a vco,. The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Phase locked loops are. Digital Phase Locked Loop Verilog Code.

From www.researchgate.net

(PDF) ALL Digital PhaseLocked Loop (ADPLL) A Survey Digital Phase Locked Loop Verilog Code The design includes a systemverilog testbench demonstrating a full. The pll comprises three blocks each of which is implemented with a. Historically pll’s were analog components. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. The topology used a vco,. Phase locked loops are. Digital Phase Locked Loop Verilog Code.

From www.scribd.com

Digital PhaseLocked Loop (DPLL) (Xilinx) PDF Detector (Radio Digital Phase Locked Loop Verilog Code Historically pll’s were analog components. The pll comprises three blocks each of which is implemented with a. Throughout the series, we will examine how an fpga works as well as demonstrate the basic building blocks of implementing digital circuits using the verilog. Is there any straight forward way to implement an all digital phase lock in synthesizable verilog? The topology. Digital Phase Locked Loop Verilog Code.