Hardware Accelerator Design Verification . Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design.

from soclabs.org

Thus, this paper proposes chiselverify, an. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major.

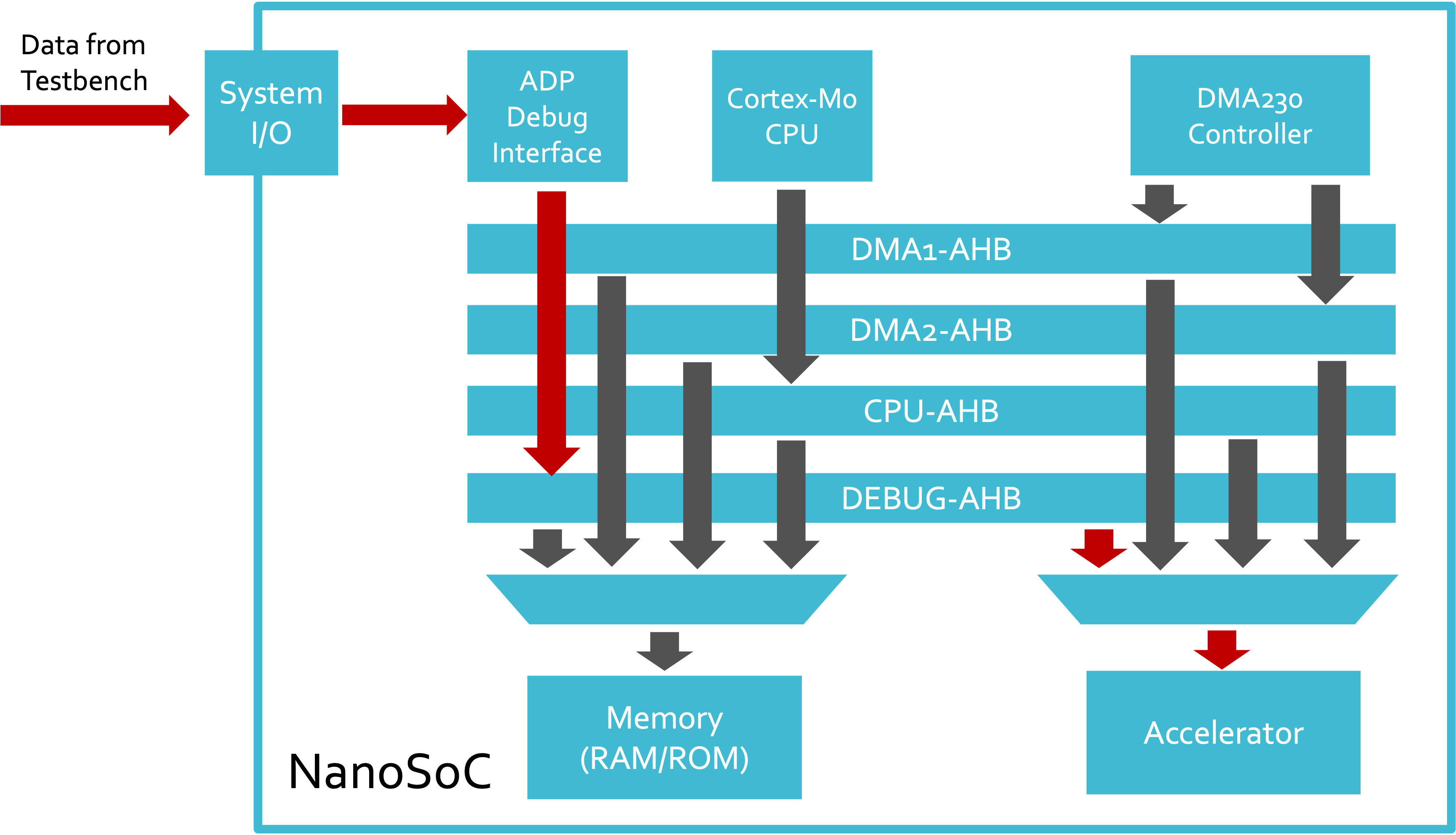

Basic System Accelerator Integration Verification SoC Labs

Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Accelerator verification lacks decades of rich experience unlike processor verification. Thus, this paper proposes chiselverify, an.

From www.researchgate.net

Multiprocessor based SVM Hardware Accelerator architecture for Hardware Accelerator Design Verification Thus, this paper proposes chiselverify, an. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware accelerators (has) significantly improve performance in. Hardware Accelerator Design Verification.

From www.researchgate.net

sDTW hardware accelerator design for HARU. Download Scientific Diagram Hardware Accelerator Design Verification Thus, this paper proposes chiselverify, an. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Since this already enables agile hardware design, we instead. Hardware Accelerator Design Verification.

From www.youtube.com

Hardware accelerator 2.0 overview for automotive mmWave sensors YouTube Hardware Accelerator Design Verification Accelerator verification lacks decades of rich experience unlike processor verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification,. Hardware Accelerator Design Verification.

From www.achronix.com

When, Why, and How Should You Use Embedded FPGA Technology for Hardware Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Accelerator verification lacks decades of rich experience unlike processor verification. Thus, this paper proposes chiselverify, an. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera and is used. Hardware Accelerator Design Verification.

From www.researchgate.net

Architecture of hardware accelerator Download Scientific Diagram Hardware Accelerator Design Verification Accelerator verification lacks decades of rich experience unlike processor verification. Thus, this paper proposes chiselverify, an. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for. Hardware Accelerator Design Verification.

From www.researchgate.net

(PDF) A ScriptBased CycleTrue Verification Framework to SpeedUp Hardware Accelerator Design Verification Thus, this paper proposes chiselverify, an. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Accelerator. Hardware Accelerator Design Verification.

From docslib.org

A Review on Hardware Accelerator Design and Implementation of CORDIC Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design, we instead focus our attention on the. Hardware Accelerator Design Verification.

From www.researchgate.net

Depthwise separable architecture hardware accelerator [24] (Reprinted Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification. Hardware Accelerator Design Verification.

From towardsdatascience.com

Hardware Accelerators for Neural Networks by Federico Peccia Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification.. Hardware Accelerator Design Verification.

From soclabs.org

Basic System Accelerator Integration Verification SoC Labs Hardware Accelerator Design Verification Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for. Hardware Accelerator Design Verification.

From github.com

GitHub 8krisv/CNNACCELERATOR Hardware accelerator for convolutional Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Thus, this paper proposes chiselverify, an. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Accelerator verification lacks. Hardware Accelerator Design Verification.

From www.slideserve.com

PPT Hardware Accelerator PowerPoint Presentation, free download ID Hardware Accelerator Design Verification In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware accelerators (has) significantly improve performance in. Hardware Accelerator Design Verification.

From www.academia.edu

(PDF) Review on Image Encryption/Decryption using AES Algorithm for Hardware Accelerator Design Verification Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Thus, this paper proposes chiselverify, an. Accelerator verification lacks decades of rich experience unlike processor verification. In this paper, we introduce an effective framework for. Hardware Accelerator Design Verification.

From www.researchgate.net

Hardware Accelerator Architecture Diagram. Download Scientific Diagram Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. Hardware verification. Hardware Accelerator Design Verification.

From www.mdpi.com

Sensors Free FullText Efficient Hardware Accelerator Design of Non Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. Accelerator. Hardware Accelerator Design Verification.

From www.researchgate.net

Proposed Hardware Accelerator Design (a) a Single Neuron and (b) The Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Thus, this paper proposes chiselverify, an. Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper, we introduce an effective framework for verifying hardware. Hardware Accelerator Design Verification.

From astaroa.com

hardwareacceleratordesign Astaroa Hardware Accelerator Design Verification Thus, this paper proposes chiselverify, an. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design,. Hardware Accelerator Design Verification.

From www.researchgate.net

(PDF) Hardware Accelerator Design for Video Segmentation with Multi Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. In this paper,. Hardware Accelerator Design Verification.

From soclabs.org

Basic System Accelerator Integration Verification SoC Labs Hardware Accelerator Design Verification In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design, we instead focus our attention on. Hardware Accelerator Design Verification.

From www.mdpi.com

Electronics Free FullText High Level Design of a Flexible PCA Hardware Accelerator Design Verification Thus, this paper proposes chiselverify, an. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera. Hardware Accelerator Design Verification.

From www.researchgate.net

(PDF) Scaling Up Hardware Accelerator Verification using AQED with Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Accelerator verification lacks decades of rich experience unlike. Hardware Accelerator Design Verification.

From www.youtube.com

FPGA + PCIe Hardware Accelerator Design Walkthrough (DDR3, M.2 Hardware Accelerator Design Verification Thus, this paper proposes chiselverify, an. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design, we instead. Hardware Accelerator Design Verification.

From www.researchgate.net

BNN hardware accelerator architecture [24]. (Reprinted with permission Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Accelerator verification lacks. Hardware Accelerator Design Verification.

From www.researchgate.net

Modes of operation of the hardware accelerator Download Scientific Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Thus, this paper proposes chiselverify, an. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Hardware. Hardware Accelerator Design Verification.

From www.researchgate.net

Hardware accelerator architecture. Download Scientific Diagram Hardware Accelerator Design Verification Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware accelerators (has) significantly improve performance in specific computational tasks. Hardware Accelerator Design Verification.

From www.technospot.net

How to Turn On Hardware Acceleration in Windows Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera. Hardware Accelerator Design Verification.

From www.intechopen.com

Hardware Accelerator Design for Machine Learning IntechOpen Hardware Accelerator Design Verification In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Accelerator verification lacks decades of rich experience. Hardware Accelerator Design Verification.

From www.slideserve.com

PPT Hardware Acceleration PowerPoint Presentation, free download ID Hardware Accelerator Design Verification Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Accelerator verification lacks decades of rich experience unlike processor verification. In this paper, we introduce an effective framework for verifying. Hardware Accelerator Design Verification.

From www.mdpi.com

Sensors Free FullText Efficient Hardware Accelerator Design of Non Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. Hardware verification. Hardware Accelerator Design Verification.

From www.semanticscholar.org

Figure 2 from Hardware accelerator implementation on FPGA for video Hardware Accelerator Design Verification Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Thus, this paper proposes chiselverify, an. Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper,. Hardware Accelerator Design Verification.

From www.researchgate.net

Structure of the hardware accelerator [38] Download Scientific Diagram Hardware Accelerator Design Verification Accelerator verification lacks decades of rich experience unlike processor verification. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. Since this already enables agile hardware design, we instead focus our attention on. Hardware Accelerator Design Verification.

From soclabs.org

Accelerator Design Flow SoC Labs Hardware Accelerator Design Verification Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor design. In this paper,. Hardware Accelerator Design Verification.

From soclabs.org

Basic System Accelerator Integration Verification SoC Labs Hardware Accelerator Design Verification Accelerator verification lacks decades of rich experience unlike processor verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Thus, this paper proposes chiselverify, an. Hardware accelerators (has) significantly improve performance in specific computational. Hardware Accelerator Design Verification.

From www.intechopen.com

Hardware Accelerator Design for Machine Learning IntechOpen Hardware Accelerator Design Verification Accelerator verification lacks decades of rich experience unlike processor verification. Hardware accelerators (has) significantly improve performance in specific computational tasks and often lack detailed specification, posing major. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Hardware verification language, pss is defined by accellera and is used to model verification intent in semiconductor. Hardware Accelerator Design Verification.

From semiwiki.com

LoadManaging Verification Hardware Acceleration in the Cloud SemiWiki Hardware Accelerator Design Verification In this paper, we introduce an effective framework for verifying hardware accelerators using formal verification, addressing the distinct verification. Since this already enables agile hardware design, we instead focus our attention on the verification flow. Thus, this paper proposes chiselverify, an. Accelerator verification lacks decades of rich experience unlike processor verification. Hardware accelerators (has) significantly improve performance in specific computational. Hardware Accelerator Design Verification.