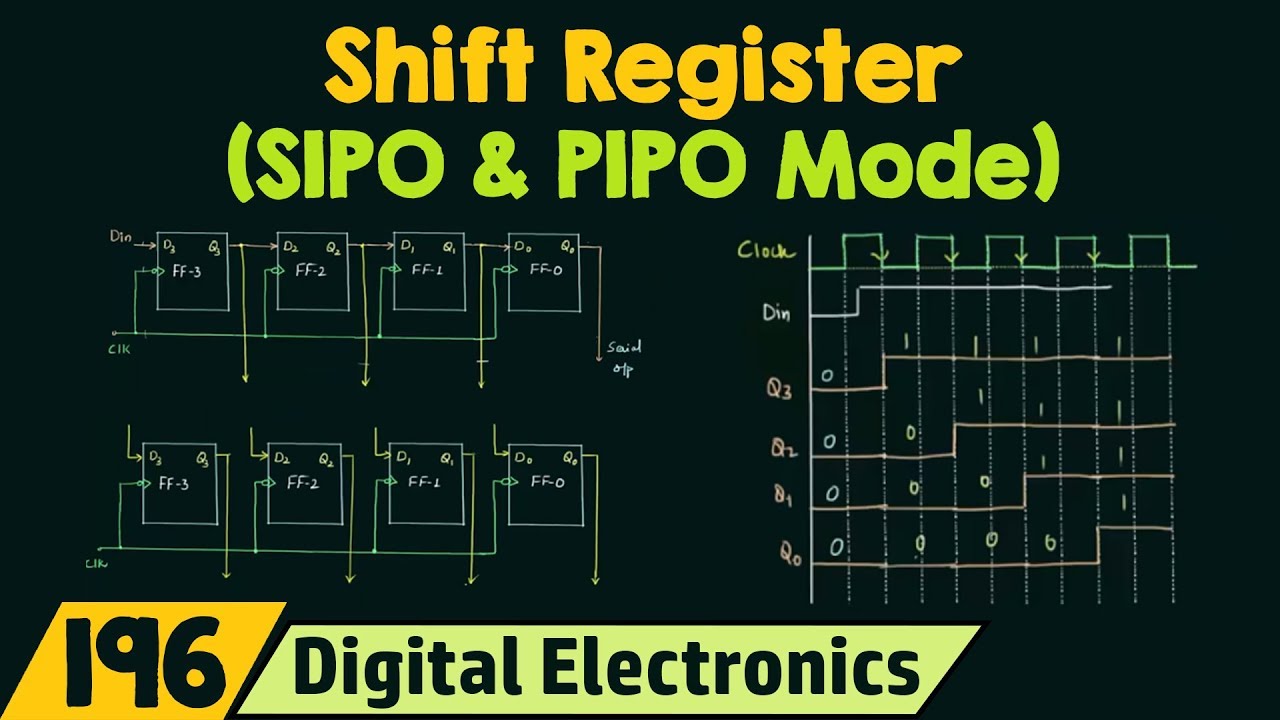

Shift Register Timing Diagram . They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register. Here we are using positive edge clock input. Shift registers are sequential logic circuits, capable of storage and transfer of data. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: The pipo shift register timing diagram is shown below. If we use a positive edge clk pulse, at that time the transition can take. They will store a bit of data for each register. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below.

from wiringengineeberhart.z13.web.core.windows.net

If we use a positive edge clk pulse, at that time the transition can take. They will store a bit of data for each register. Here we are using positive edge clock input. Shift registers are sequential logic circuits, capable of storage and transfer of data. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: The pipo shift register timing diagram is shown below. They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register.

7495 Shift Register Circuit Diagram

Shift Register Timing Diagram They will store a bit of data for each register. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. The pipo shift register timing diagram is shown below. A timing signal that controls the shifting operation in the shift register. They are made up of flip flops which are connected in such a way that the output of one flip. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: Shift registers are sequential logic circuits, capable of storage and transfer of data. If we use a positive edge clk pulse, at that time the transition can take. They will store a bit of data for each register. Here we are using positive edge clock input.

From www.slideserve.com

PPT Registers and Counters PowerPoint Presentation, free download Shift Register Timing Diagram Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register. Shift registers are sequential logic circuits, capable. Shift Register Timing Diagram.

From robhosking.com

11+ Shift Register Timing Diagram Robhosking Diagram Shift Register Timing Diagram The pipo shift register timing diagram is shown below. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are. Shift Register Timing Diagram.

From electronics.stackexchange.com

digital logic Understand the timing of Shift Register Electrical Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. If we use a positive edge clk pulse, at that time the transition can take. Shift registers are sequential logic circuits, capable of storage and transfer of data. A timing signal that controls the shifting operation in the shift register.. Shift Register Timing Diagram.

From www.cse.psu.edu

CMPEN 297B Homework 7 Shift Register Timing Diagram A timing signal that controls the shifting operation in the shift register. Here we are using positive edge clock input. They will store a bit of data for each register. Shift registers are sequential logic circuits, capable of storage and transfer of data. The pipo shift register timing diagram is shown below. By serial format we mean that the data. Shift Register Timing Diagram.

From www.electroniclinic.com

Shift Register Shift Right and Shift Left Registers with circuit diagram Shift Register Timing Diagram If we use a positive edge clk pulse, at that time the transition can take. Here we are using positive edge clock input. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. Shift registers are sequential. Shift Register Timing Diagram.

From protostack.com.au

Introduction to 74HC595 shift register Controlling 16 LEDs Protostack Shift Register Timing Diagram If we use a positive edge clk pulse, at that time the transition can take. Shift registers are sequential logic circuits, capable of storage and transfer of data. The pipo shift register timing diagram is shown below. They are made up of flip flops which are connected in such a way that the output of one flip. Generally, shift registers. Shift Register Timing Diagram.

From robhosking.com

15 Parallel In Serial Out Shift Register Timing Diagram Robhosking Shift Register Timing Diagram They will store a bit of data for each register. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. A timing signal that controls the shifting operation in the shift register. Shift registers are sequential logic. Shift Register Timing Diagram.

From www.electroniclinic.com

Different Types of Shift Registers In Digital Electronics Shift Register Timing Diagram By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. They will store a bit of data for each register. They are made up of flip flops which are connected in such a way that the output. Shift Register Timing Diagram.

From manuallibraryoutpoint.z21.web.core.windows.net

Design A 4bit Siso Shift Register Shift Register Timing Diagram Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: If we use a positive edge clk pulse, at that time the transition can take. Shift registers are sequential logic circuits, capable of storage and transfer of data. Here we are using positive edge clock input. They will store. Shift Register Timing Diagram.

From www.electroniclinic.com

Shift Register Shift Right and Shift Left Registers with circuit diagram Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. If we use a positive edge clk. Shift Register Timing Diagram.

From protostack.com.au

Introduction to 74HC595 shift register Controlling 16 LEDs Protostack Shift Register Timing Diagram They will store a bit of data for each register. A timing signal that controls the shifting operation in the shift register. They are made up of flip flops which are connected in such a way that the output of one flip. The pipo shift register timing diagram is shown below. Generally, shift registers operate in one of four different. Shift Register Timing Diagram.

From www.geeksforgeeks.org

Parallel In Parallel Out (PIPO) Shift Register Shift Register Timing Diagram A timing signal that controls the shifting operation in the shift register. They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out”. Shift Register Timing Diagram.

From electricalfundablog.com

Shift Registers Modes of Operation, Types, How it Works, Applications Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. If we use a positive edge clk pulse, at that time the transition can take. Shift registers are sequential logic circuits, capable of storage and transfer of data. Generally, shift registers operate in one of four different modes with the. Shift Register Timing Diagram.

From mydiagram.online

[DIAGRAM] Logic Diagram Of Universal Shift Register Shift Register Timing Diagram They will store a bit of data for each register. If we use a positive edge clk pulse, at that time the transition can take. The pipo shift register timing diagram is shown below. They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the. Shift Register Timing Diagram.

From electronicscoach.com

What is a Shift Register? Definition, Operation and Applications of Shift Register Timing Diagram A timing signal that controls the shifting operation in the shift register. They are made up of flip flops which are connected in such a way that the output of one flip. The pipo shift register timing diagram is shown below. Shift registers are sequential logic circuits, capable of storage and transfer of data. If we use a positive edge. Shift Register Timing Diagram.

From www.electroniclinic.com

Shift Register Shift Right and Shift Left Registers with circuit diagram Shift Register Timing Diagram Here we are using positive edge clock input. If we use a positive edge clk pulse, at that time the transition can take. They are made up of flip flops which are connected in such a way that the output of one flip. They will store a bit of data for each register. By serial format we mean that the. Shift Register Timing Diagram.

From robhosking.com

11+ Shift Register Timing Diagram Robhosking Diagram Shift Register Timing Diagram A timing signal that controls the shifting operation in the shift register. They will store a bit of data for each register. The pipo shift register timing diagram is shown below. They are made up of flip flops which are connected in such a way that the output of one flip. Shift registers are sequential logic circuits, capable of storage. Shift Register Timing Diagram.

From www.numerade.com

SOLVED Example 27.3 Universal Shift Register Timing Diagram The block Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. If we use a positive edge clk. Shift Register Timing Diagram.

From electronics.stackexchange.com

Output setting time for shift register (74HC595) Electrical Shift Register Timing Diagram The pipo shift register timing diagram is shown below. Shift registers are sequential logic circuits, capable of storage and transfer of data. They will store a bit of data for each register. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out”. Shift Register Timing Diagram.

From www.build-electronic-circuits.com

Beginner's Guide to the Shift Register in Digital Electronics Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register. The pipo shift register timing diagram is shown below. They will store a bit of data for each register. By serial format we mean that the data bits. Shift Register Timing Diagram.

From copyprogramming.com

Vhdl 4bit Shift register with flip flop Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register. Shift registers are sequential logic circuits, capable of storage and transfer of data. They will store a bit of data for each register. Generally, shift registers operate in. Shift Register Timing Diagram.

From www.coursehero.com

[Solved] 4bit shift register below. complete the timing diagram Shift Register Timing Diagram If we use a positive edge clk pulse, at that time the transition can take. Here we are using positive edge clock input. They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are presented sequentially in time on a single. Shift Register Timing Diagram.

From www.chegg.com

Solved 4. (Timing Diagram for a Shift Register) Consider the Shift Register Timing Diagram By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. Here we are using positive edge clock input. The pipo shift register timing diagram is shown below. Shift registers are sequential logic circuits, capable of storage and. Shift Register Timing Diagram.

From www.javatpoint.com

Shift Registers in Digital Electronics Javatpoint Shift Register Timing Diagram They will store a bit of data for each register. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. If we use a positive edge clk pulse, at that time the transition can take. A timing. Shift Register Timing Diagram.

From www.youtube.com

Parallel In Serial Out Shift Registers YouTube Shift Register Timing Diagram The pipo shift register timing diagram is shown below. A timing signal that controls the shifting operation in the shift register. They are made up of flip flops which are connected in such a way that the output of one flip. If we use a positive edge clk pulse, at that time the transition can take. Shift registers are sequential. Shift Register Timing Diagram.

From mungfali.com

Timing Diagram Of Siso Shift Register Shift Register Timing Diagram Shift registers are sequential logic circuits, capable of storage and transfer of data. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the. Shift Register Timing Diagram.

From robhosking.com

11+ Shift Register Timing Diagram Robhosking Diagram Shift Register Timing Diagram The pipo shift register timing diagram is shown below. Shift registers are sequential logic circuits, capable of storage and transfer of data. They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register. Here we are using positive edge. Shift Register Timing Diagram.

From www.allaboutcircuits.com

Shift Registers Serialin, Parallelout (SIPO) Conversion Shift Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. A timing signal that controls the shifting. Shift Register Timing Diagram.

From wiringengineeberhart.z13.web.core.windows.net

7495 Shift Register Circuit Diagram Shift Register Timing Diagram They are made up of flip flops which are connected in such a way that the output of one flip. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: Shift registers are sequential logic circuits, capable of storage and transfer of data. The pipo shift register timing diagram. Shift Register Timing Diagram.

From robhosking.com

15 Parallel In Serial Out Shift Register Timing Diagram Robhosking Shift Register Timing Diagram A timing signal that controls the shifting operation in the shift register. They will store a bit of data for each register. They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are presented sequentially in time on a single wire. Shift Register Timing Diagram.

From mungfali.com

Shift Register Timing Diagram Shift Register Timing Diagram Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: They are made up of flip flops which are connected in such a way that the output of one flip. A timing signal that controls the shifting operation in the shift register. Here we are using positive edge clock. Shift Register Timing Diagram.

From openelectronicsproject.blogspot.com

Open Electronics Project 74HC165 Shift Register and your Arduino UNO Shift Register Timing Diagram If we use a positive edge clk pulse, at that time the transition can take. They will store a bit of data for each register. Here we are using positive edge clock input. Generally, shift registers operate in one of four different modes with the basic movement of data through a shift register being: Shift registers are sequential logic circuits,. Shift Register Timing Diagram.

From www.youtube.com

Serial In Parallel Out Shift Registers YouTube Shift Register Timing Diagram Shift registers are sequential logic circuits, capable of storage and transfer of data. The pipo shift register timing diagram is shown below. Here we are using positive edge clock input. They are made up of flip flops which are connected in such a way that the output of one flip. By serial format we mean that the data bits are. Shift Register Timing Diagram.

From www.slideserve.com

PPT Shift Registers and Shift Register Counters PowerPoint Shift Register Timing Diagram If we use a positive edge clk pulse, at that time the transition can take. The pipo shift register timing diagram is shown below. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. A timing signal. Shift Register Timing Diagram.

From afdammingcoschematic.z14.web.core.windows.net

Siso And Sipo Shift Register Shift Register Timing Diagram If we use a positive edge clk pulse, at that time the transition can take. By serial format we mean that the data bits are presented sequentially in time on a single wire or circuit as in the case of the “data out” on the block diagram below. Generally, shift registers operate in one of four different modes with the. Shift Register Timing Diagram.