Ring Oscillator Jitter Simulation . analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. recently, there has been some work on modeling jitter and phase noise in ring oscillators. low jitter vco design examples in this chapter we will examine two design examples.

from www.slideserve.com

low jitter vco design examples in this chapter we will examine two design examples. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there has been some work on modeling jitter and phase noise in ring oscillators.

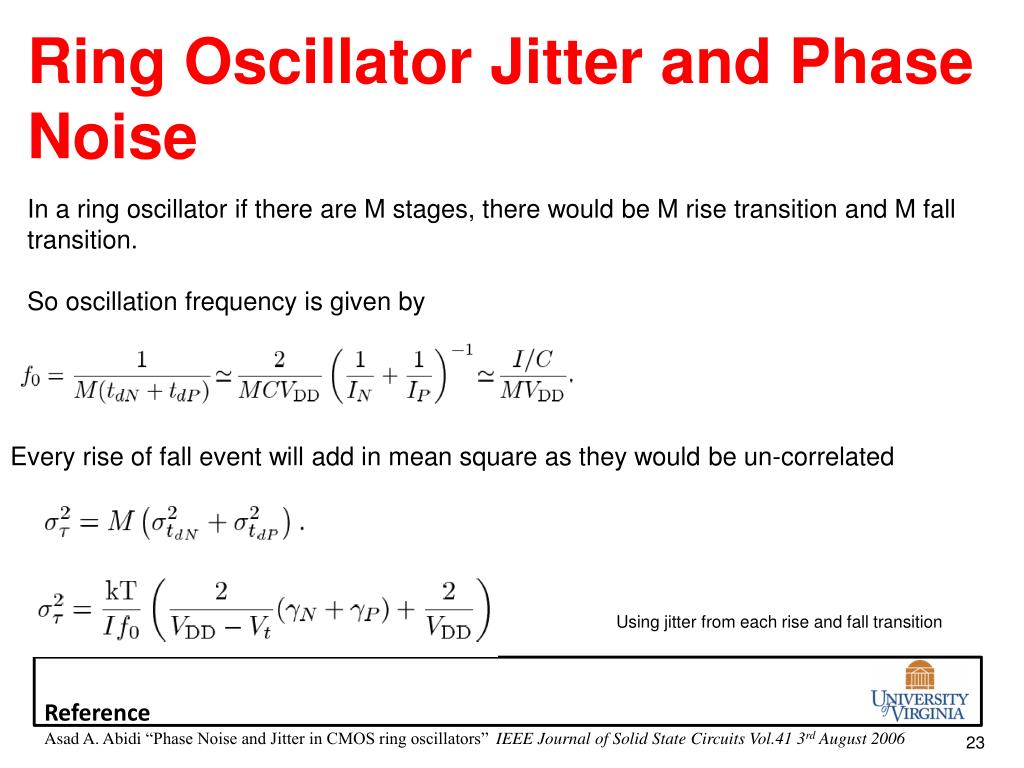

PPT Phase Noise and Jitter in Oscillator PowerPoint Presentation

Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. low jitter vco design examples in this chapter we will examine two design examples. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. recently, there has been some work on modeling jitter and phase noise in ring oscillators. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and.

From www.semanticscholar.org

Figure 1 from A Sub100 fsJitter 8.16GHz RingOscillatorBased Power Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there has been some work on modeling jitter and phase noise in ring oscillators. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from Simulation of random jitter in ring oscillators with Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and.. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 5 from Phase Noise and Jitter in CMOS Ring Oscillators Ring Oscillator Jitter Simulation recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from A LowJitter RingOscillator PhaseLocked Loop Using Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay.. Ring Oscillator Jitter Simulation.

From www.researchgate.net

Block diagram of Nstage ring oscillator with kstage subfeedback loops Ring Oscillator Jitter Simulation in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and.. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from LowJitter PhaseLocked Loop With Ring Voltage Controlled Ring Oscillator Jitter Simulation recently, there has been some work on modeling jitter and phase noise in ring oscillators. low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and. Ring Oscillator Jitter Simulation.

From www.youtube.com

Frequency Boost Jitter Reduction for Voltage Controlled Ring Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there has been some work on modeling jitter and phase noise in ring oscillators. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. low jitter vco design examples in. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 8 from Phase Noise and Jitter in CMOS Ring Oscillators Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. low jitter vco design examples in this chapter we will examine two design examples. The jitter gure of. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

A 0.4 psRMSJitter 13 GHz RingOscillator PLL Using PhaseNoise Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. recently, there has been some work on modeling jitter and phase noise in ring oscillators. low. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from Jitter and phase noise in ring oscillators Semantic Scholar Ring Oscillator Jitter Simulation in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay.. Ring Oscillator Jitter Simulation.

From www.researchgate.net

(PDF) Simulation of random jitter in ring oscillators with SPICE Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

[PDF] Jitter and phase noise in ring oscillators Semantic Scholar Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there has been some work on modeling jitter and phase noise in ring oscillators. low jitter vco design examples in. Ring Oscillator Jitter Simulation.

From www.youtube.com

FrequencyBoost Jitter Reduction for VoltageControlled Ring Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there. Ring Oscillator Jitter Simulation.

From www.slideserve.com

PPT Phase Noise and Jitter in Oscillator PowerPoint Presentation Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due. Ring Oscillator Jitter Simulation.

From www.slideserve.com

PPT Oscillators PowerPoint Presentation, free download ID5594930 Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. low jitter vco design examples in this chapter we will examine two design examples. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. in this paper, we have simulated the. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

[PDF] Jitter and phase noise in ring oscillators Semantic Scholar Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

A LowJitter RingOscillator PhaseLocked Loop Using Feedforward Noise Ring Oscillator Jitter Simulation recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential. Ring Oscillator Jitter Simulation.

From deepai.org

On Entropy and Bit Patterns of Ring Oscillator Jitter DeepAI Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due. Ring Oscillator Jitter Simulation.

From www.nxfee.com

FrequencyBoost Jitter Reduction for VoltageControlled Ring Oscillators Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k,. Ring Oscillator Jitter Simulation.

From www.researchgate.net

General structure of ring oscillator Download Scientific Diagram Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from An investigation of timing jitter in bipolar ECL ring Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. analysis shows. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from Timing jitter in a 1.35GHz singleended ring oscillator Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. low jitter vco design examples in this chapter we will examine two design examples. recently, there has. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 11 from Phase Noise and Jitter in CMOS Ring Oscillators Ring Oscillator Jitter Simulation recently, there has been some work on modeling jitter and phase noise in ring oscillators. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. low jitter. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

[PDF] Jitter and phase noise in ring oscillators Semantic Scholar Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there has been some work on modeling jitter and phase noise in ring oscillators. low jitter vco design examples in this chapter we will examine two design examples. analysis shows that in differential ring oscillators, white noise. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 5 from Jitter Optimization Using the Body Bias in Digital CMOS Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. recently, there has been some work on modeling jitter and phase noise in ring oscillators. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

A LowJitter RingOscillator PhaseLocked Loop Using Feedforward Noise Ring Oscillator Jitter Simulation in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay.. Ring Oscillator Jitter Simulation.

From circuitgenerator.com

LTspice tutorial Design and simulation of CMOS ring oscillator Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

A 2.5GHz phaseswitching PLL using a supply controlled 2delaystage Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

A LowJitter RingOscillator PhaseLocked Loop Using Feedforward Noise Ring Oscillator Jitter Simulation The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. low jitter vco design examples in this chapter we will examine two design examples. recently, there has been some work on modeling jitter and phase noise in ring oscillators. analysis shows that in differential ring oscillators, white noise. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 3 from Ieee 2004 Custom Integrated Circuits Conference an Ring Oscillator Jitter Simulation recently, there has been some work on modeling jitter and phase noise in ring oscillators. low jitter vco design examples in this chapter we will examine two design examples. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. analysis shows that in differential. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from A CalibrationFree RingOscillator PLL With Gain Tracking Ring Oscillator Jitter Simulation recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. low. Ring Oscillator Jitter Simulation.

From www.semanticscholar.org

Figure 1 from A 7.6 mW, 414 fs RMSJitter 10 GHz PhaseLocked Loop for Ring Oscillator Jitter Simulation analysis shows that in differential ring oscillators, white noise in the differential pairs dominates the jitter and. recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure. Ring Oscillator Jitter Simulation.

From community.cadence.com

Setting up a jitter simulation for Ring Oscillator Custom IC Design Ring Oscillator Jitter Simulation in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. low jitter vco design examples in this chapter we will examine two design examples. analysis shows. Ring Oscillator Jitter Simulation.

From web02.gonzaga.edu

ring oscillator design, layout and simulation Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. recently, there has been some work on modeling jitter and phase noise in ring oscillators. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. analysis shows that in differential. Ring Oscillator Jitter Simulation.

From www.researchgate.net

Jitterpower and frequencypower tradeoffs in a ring oscillator Ring Oscillator Jitter Simulation low jitter vco design examples in this chapter we will examine two design examples. The jitter gure of merit k, developed in chapters 5 and 6, is applied to characterize jitter in delay. in this paper, we have simulated the timing jitter due to device noise in a nine stage cmos differential ring oscillator and. recently, there. Ring Oscillator Jitter Simulation.