Pcie Clock Request Signal . Upon entry, the device or host deasserts. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. In module pin is defined as open drain,. The recovery can be done in a number of ways,. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. Here is an implementation note from pcie 4.0. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. there is a lot of information about clkreq# connections in the pcie base specification. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. the clock is not embedded with the data signal, it can be recovered from the data.

from www.renesas.com

a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. Upon entry, the device or host deasserts. Here is an implementation note from pcie 4.0. the clock is not embedded with the data signal, it can be recovered from the data. there is a lot of information about clkreq# connections in the pcie base specification. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. In module pin is defined as open drain,. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission.

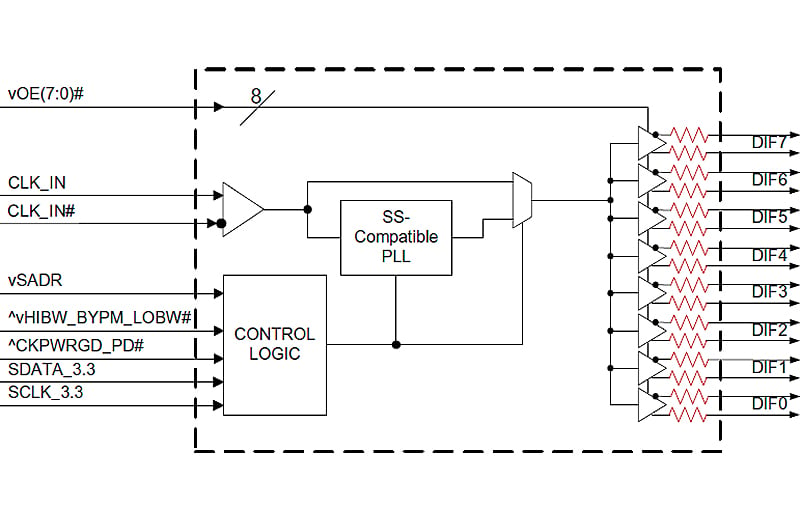

9DBU0841 8output 1.5V PCIe ZeroDelay/Fanout Clock Buffer Renesas

Pcie Clock Request Signal unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. The recovery can be done in a number of ways,. there is a lot of information about clkreq# connections in the pcie base specification. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. the clock is not embedded with the data signal, it can be recovered from the data. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. In module pin is defined as open drain,. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. Here is an implementation note from pcie 4.0. Upon entry, the device or host deasserts.

From www.eedesignit.com

Create a simple IDT PCIe clock with flexible outputs Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. Upon entry, the device or host deasserts. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. there is a lot of information about clkreq# connections in the pcie base specification. unlike conventional l1,. Pcie Clock Request Signal.

From www.paradetech.com

PS8559 2Lane PCIe 8GT/s and SATA 6Gb/s Redriver, Bidirectional Parade Technologies, Ltd. Pcie Clock Request Signal a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. the clock is not embedded with the data signal, it can be recovered from the data. Here is an implementation note from pcie 4.0.. Pcie Clock Request Signal.

From www.thomas-krenn.com

PCIe Reference Clock ThomasKrennWiki Pcie Clock Request Signal we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. In module pin is defined. Pcie Clock Request Signal.

From dokumen.tips

(PDF) Si52142 Data Sheet PCIExpress Gen 1, Gen 2, & Gen 3 Two … · Functional Block Diagram Pcie Clock Request Signal The recovery can be done in a number of ways,. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. In module pin is defined as open drain,. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. this application note provides basic information. Pcie Clock Request Signal.

From www.digikey.tw

Schemeit 9FGV0241 PCIExpress Clock Generator Pcie Clock Request Signal this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. Upon entry, the device or host deasserts. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. unlike. Pcie Clock Request Signal.

From www.electronicdesign.com

Timing Product Families Offer Sub200fs Phase Jitter For PCIe Clocks Electronic Design Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. In module pin is defined as open drain,. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. Upon entry, the device or host deasserts. The recovery can be done in a number of. Pcie Clock Request Signal.

From www.thomas-krenn.com

PCIe Reference Clock ThomasKrennWiki Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. In module pin is defined as open drain,. Here is an implementation note from pcie 4.0. there is a lot of information about clkreq# connections in the pcie base specification. peripheral component interconnect express (pcie) is an industry standard for transferring. Pcie Clock Request Signal.

From www.renesas.com

9DBL0443 4Output 3.3V PCIe ZeroDelay/Fanout Clock Buffer with Loss of Signal Indicator Renesas Pcie Clock Request Signal there is a lot of information about clkreq# connections in the pcie base specification. The recovery can be done in a number of ways,. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1. Pcie Clock Request Signal.

From www.youtube.com

PCI Express (PCIe) Clock ZeroDelay and Fanout Buffers by IDT YouTube Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. peripheral component interconnect express (pcie) is an. Pcie Clock Request Signal.

From www.renesas.com

9DBU0841 8output 1.5V PCIe ZeroDelay/Fanout Clock Buffer Renesas Pcie Clock Request Signal unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. a device will indicate its. Pcie Clock Request Signal.

From www.design-reuse.com

PCIe Spread Spectrum Clocking (SSC) for Verification Engineers Pcie Clock Request Signal a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. Here is an implementation note from pcie 4.0. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. The. Pcie Clock Request Signal.

From e2e.ti.com

Timing is Everything How to optimize clock distribution in PCIe applications Analog Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. Here is an implementation note from pcie 4.0. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. . Pcie Clock Request Signal.

From www.youtube.com

PCI Express (PCIe) Clock Overview by IDT YouTube Pcie Clock Request Signal unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. Here is an implementation note from pcie 4.0. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based. Pcie Clock Request Signal.

From embeddedsystemarena.blogspot.com

Embedded System Design May 2012 Pcie Clock Request Signal Upon entry, the device or host deasserts. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. The recovery can be done in a number of ways,. unlike conventional l1, a clock. Pcie Clock Request Signal.

From e2e.ti.com

AM5746 PCIe reference clock Processors forum Processors TI E2E support forums Pcie Clock Request Signal peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. Here is an implementation note from pcie 4.0. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. the clock is not embedded with the data signal, it can be recovered from the data.. Pcie Clock Request Signal.

From electronics.stackexchange.com

high speed PCIe Present pin working principle Electrical Engineering Stack Exchange Pcie Clock Request Signal this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. In module pin is defined as open drain,. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices.. Pcie Clock Request Signal.

From www.youtube.com

PCI Express PCIe Clock Applications Overview by IDT YouTube Pcie Clock Request Signal a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. Upon entry, the device or host deasserts. The recovery can be done in a number of ways,. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. we are using txb0304rutr level shifter for driving. Pcie Clock Request Signal.

From www.edn.com

PCI Express 3.0 needs reliable timing design EDN Pcie Clock Request Signal this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. unlike conventional l1, a clock request (clkreq#) signal. Pcie Clock Request Signal.

From www.truechip.net

Clocking Architectures in PCI Express Blogs by Truechip Truechip VIPs Pcie Clock Request Signal a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. there is a lot of information about clkreq# connections in the pcie base specification. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. a device will indicate its support for. Pcie Clock Request Signal.

From www.slideserve.com

PPT PCI Express Physical Layer PowerPoint Presentation, free download ID9563206 Pcie Clock Request Signal unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. there is a lot of information about clkreq# connections in the pcie base specification. Upon entry, the device or host deasserts. the clock is not embedded with the data signal, it can be recovered from the data. a refclk,. Pcie Clock Request Signal.

From www.edn.com

PCI Express 3.0 needs reliable timing design EDN Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. Upon entry, the device or host deasserts. Here. Pcie Clock Request Signal.

From www.renesas.com

PCI Express® Clocks Renesas Pcie Clock Request Signal unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. In module pin is defined as open drain,. Here is an implementation note from pcie 4.0. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. a refclk, or reference clock signal, is a prerequisite. Pcie Clock Request Signal.

From itecnotes.com

Electronic Understanding PCIE and FPGA clock “magic” Valuable Tech Notes Pcie Clock Request Signal peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. Upon entry, the device or host deasserts. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. . Pcie Clock Request Signal.

From www.youtube.com

PCIe QuickLearn SpreadSpectrum Clocking YouTube Pcie Clock Request Signal In module pin is defined as open drain,. The recovery can be done in a number of ways,. Upon entry, the device or host deasserts. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. Here. Pcie Clock Request Signal.

From mecsu.vn

IC peripheral circuit; clock signal generator; PCIe; QSOP16 Mecsu.vn Pcie Clock Request Signal this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. In module pin is defined as open drain,. The recovery can be done in a number of ways,. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. Here is an implementation note from pcie 4.0.. Pcie Clock Request Signal.

From e2e.ti.com

Signal Conditioning functions go mainstream in PCI Express Gen 4 Analog Technical articles Pcie Clock Request Signal we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. Upon entry, the device or host. Pcie Clock Request Signal.

From home.fedevel.com

PCIe reverse polarity signals Pcie Clock Request Signal In module pin is defined as open drain,. we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,.. Pcie Clock Request Signal.

From www.cryptoprofi.info

Для чего служит сигнал PERST на PCIE устройствах Pcie Clock Request Signal we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. Upon entry, the device or host deasserts. a device will indicate its support for l1 substates and entry mechanisms in its configuration. Pcie Clock Request Signal.

From dxolsidtn.blob.core.windows.net

Clock Signal Definition at Jay Packard blog Pcie Clock Request Signal a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. the clock is not embedded with the data signal, it can be recovered from the data. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. The recovery can be done in a number. Pcie Clock Request Signal.

From www.renesas.com

9DBU0931 9output 1.5V PCIe Fanout Clock Buffer Renesas Pcie Clock Request Signal this application note provides basic information about the pcie refclk, pcie reference clock architectures, spread. In module pin is defined as open drain,. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. a refclk, or reference clock signal, is a prerequisite for a pcie device to begin data transmission. . Pcie Clock Request Signal.

From www.reddit.com

What is PCI Express Clock gating? And is it worth keeping enabled? I have heard from quite a few Pcie Clock Request Signal there is a lot of information about clkreq# connections in the pcie base specification. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. unlike conventional l1, a clock request (clkreq#) signal is. Pcie Clock Request Signal.

From e2e.ti.com

AM5728 PCIe external clock SI issues Processors forum Processors TI E2E support forums Pcie Clock Request Signal unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. The recovery can be done in a number of ways,. there is a lot of information about clkreq# connections in the pcie base specification.. Pcie Clock Request Signal.

From www.youtube.com

PCIe QuickLearn Clocks in Data Centers YouTube Pcie Clock Request Signal we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. peripheral component interconnect express (pcie) is an industry standard for transferring data between cpus and peripheral devices. the clock is not embedded with the data signal, it can be recovered from the data. there is a lot of. Pcie Clock Request Signal.

From e2e.ti.com

Timing is Everything How to optimize clock distribution in PCIe applications Analog Pcie Clock Request Signal we are using txb0304rutr level shifter for driving pcie clkreq# signal which connected to pcie based wlan module. In module pin is defined as open drain,. Here is an implementation note from pcie 4.0. there is a lot of information about clkreq# connections in the pcie base specification. peripheral component interconnect express (pcie) is an industry standard. Pcie Clock Request Signal.

From e2e.ti.com

TMDX654IDKEVM PCIe clock selection Processors forum Processors TI E2E support forums Pcie Clock Request Signal the clock is not embedded with the data signal, it can be recovered from the data. unlike conventional l1, a clock request (clkreq#) signal is used to enter and exit the l1 substates. a device will indicate its support for l1 substates and entry mechanisms in its configuration space,. a refclk, or reference clock signal, is. Pcie Clock Request Signal.