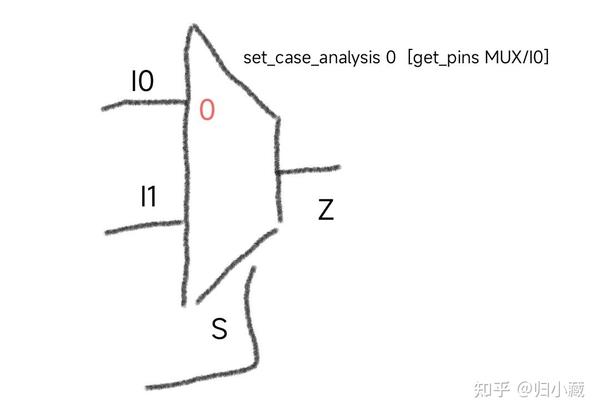

Clock Gating Check Mux . there can be two cases: we will discuss the same here in this paper with the example of such a scenario: The inferred logic block in the original. consider a multiplexer (mux) at the data input of a register. The first method is used when. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. Data signal at the select pin of mux used to select between two clocks. clock gating checks in case of mux select transition when both clocks are running. Definition of clock gating check: Clock gating check as inferred and applied on clock path multiplexers. A clock gating check is a constraint, either. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. In the following figure, it is. one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are.

from zhuanlan.zhihu.com

clock gating checks in case of mux select transition when both clocks are running. A clock gating check is a constraint, either. one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. This mux is controlled by an enable signal. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: Definition of clock gating check: The inferred logic block in the original. In the following figure, it is. Data signal at the select pin of mux used to select between two clocks. The first method is used when.

门控时钟检查(clock gating check) 知乎

Clock Gating Check Mux The first method is used when. clock gating checks in case of mux select transition when both clocks are running. A clock gating check is a constraint, either. The first method is used when. The inferred logic block in the original. one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. Data signal at the select pin of mux used to select between two clocks. consider a multiplexer (mux) at the data input of a register. Clock gating check as inferred and applied on clock path multiplexers. there can be two cases: we will discuss the same here in this paper with the example of such a scenario: the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. This mux is controlled by an enable signal. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: In the following figure, it is. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented.

From blog.csdn.net

clock gating checkCSDN博客 Clock Gating Check Mux Data signal at the select pin of mux used to select between two clocks. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: Clock gating check as inferred and applied on clock path multiplexers. The inferred logic block in the original. in this article, two. Clock Gating Check Mux.

From blog.csdn.net

静态时序分析(STA)_门控时钟(Clock Gating Checks)_门控时钟的时序分析CSDN博客 Clock Gating Check Mux In the following figure, it is. we will discuss the same here in this paper with the example of such a scenario: The inferred logic block in the original. Definition of clock gating check: The first method is used when. one way to avoid it is to gate both the clocks just before changing the ‘select’, so that. Clock Gating Check Mux.

From vlsiuniverse.blogspot.com

Clock multiplexer for glitchfree clock switching Clock Gating Check Mux we will discuss the same here in this paper with the example of such a scenario: the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. The. Clock Gating Check Mux.

From community.cadence.com

Are the add and master_clock constraints needed in an MMMC setup Clock Gating Check Mux Definition of clock gating check: Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. A clock gating check is a constraint, either. The inferred logic. Clock Gating Check Mux.

From www.edaboard.com

SDC constraints for MUXed clock input + clock divider + MUXed clock Clock Gating Check Mux Definition of clock gating check: The inferred logic block in the original. there can be two cases: In the following figure, it is. The first method is used when. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. Out of the many scenarios in which a multiplexer. Clock Gating Check Mux.

From www.researchgate.net

The structure of a 31 positiveedgetriggered clock multiplexer Clock Gating Check Mux Data signal at the select pin of mux used to select between two clocks. Clock gating check as inferred and applied on clock path multiplexers. we will discuss the same here in this paper with the example of such a scenario: the clock gating setup check is used to ensure the controlling data signals are stable before the. Clock Gating Check Mux.

From semiengineering.com

Clock Gating Semiconductor Engineering Clock Gating Check Mux A clock gating check is a constraint, either. In the following figure, it is. Definition of clock gating check: clock gating checks in case of mux select transition when both clocks are running. This mux is controlled by an enable signal. in this article, two different methods of avoiding a glitch at the output clock line of a. Clock Gating Check Mux.

From fyogyhdyn.blob.core.windows.net

What Is Clock Gating Efficiency at Mark Goff blog Clock Gating Check Mux Clock gating check as inferred and applied on clock path multiplexers. the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. The inferred logic block in the original.. Clock Gating Check Mux.

From www.vrogue.co

Vlsi Soc Design Clock Gating Integrated Cell vrogue.co Clock Gating Check Mux Data signal at the select pin of mux used to select between two clocks. consider a multiplexer (mux) at the data input of a register. In the following figure, it is. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: clock gating checks in. Clock Gating Check Mux.

From mungfali.com

Clock Gating VLSI Clock Gating Check Mux clock gating checks in case of mux select transition when both clocks are running. This mux is controlled by an enable signal. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. Data signal at the select pin of mux used to select between two clocks. Definition of. Clock Gating Check Mux.

From medium.com

Let’s talk about Clock Gating!. Clock gating is a technique that… by Clock Gating Check Mux Clock gating check as inferred and applied on clock path multiplexers. clock gating checks in case of mux select transition when both clocks are running. This mux is controlled by an enable signal. Data signal at the select pin of mux used to select between two clocks. in this article, two different methods of avoiding a glitch at. Clock Gating Check Mux.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Check Mux A clock gating check is a constraint, either. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. there can be two cases: The first method is used when. In the following figure, it is. Out of the many scenarios in which a multiplexer may be present in. Clock Gating Check Mux.

From www.cnblogs.com

clock gating clock gating的timing check 春风一郎 博客园 Clock Gating Check Mux Data signal at the select pin of mux used to select between two clocks. A clock gating check is a constraint, either. we will discuss the same here in this paper with the example of such a scenario: consider a multiplexer (mux) at the data input of a register. clock gating checks in case of mux select. Clock Gating Check Mux.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Check Mux This mux is controlled by an enable signal. we will discuss the same here in this paper with the example of such a scenario: In the following figure, it is. Clock gating check as inferred and applied on clock path multiplexers. the clock gating setup check is used to ensure the controlling data signals are stable before the. Clock Gating Check Mux.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Check Mux one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. The inferred logic block in the original. the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. clock gating checks in case. Clock Gating Check Mux.

From www.elecfans.com

门控时钟检查(clock gating check)的理解和设计应用电子发烧友网 Clock Gating Check Mux the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. Definition of clock gating check: The inferred logic block in the original. Clock gating check as inferred and applied on clock path multiplexers. This mux is controlled by an enable signal. Out of the many scenarios in which a. Clock Gating Check Mux.

From blog.csdn.net

静态时序分析(STA)_门控时钟(Clock Gating Checks)_门控时钟的时序分析CSDN博客 Clock Gating Check Mux Definition of clock gating check: The first method is used when. clock gating checks in case of mux select transition when both clocks are running. In the following figure, it is. there can be two cases: This mux is controlled by an enable signal. Clock gating check as inferred and applied on clock path multiplexers. we will. Clock Gating Check Mux.

From blog.csdn.net

静态时序分析(STA)_门控时钟(Clock Gating Checks)_门控时钟的时序分析CSDN博客 Clock Gating Check Mux Definition of clock gating check: one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. Data signal at the select pin of mux. Clock Gating Check Mux.

From zhuanlan.zhihu.com

门控时钟检查(clock gating check) 知乎 Clock Gating Check Mux there can be two cases: consider a multiplexer (mux) at the data input of a register. The inferred logic block in the original. one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. The first method is used when. A clock gating. Clock Gating Check Mux.

From www.elecfans.com

门控时钟检查(clock gating check)的理解和设计应用电子发烧友网 Clock Gating Check Mux one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. clock gating checks in case of mux select transition when both clocks are running. Clock gating check as inferred and applied on clock path multiplexers. consider a multiplexer (mux) at the data. Clock Gating Check Mux.

From community.cadence.com

How to resolve clock gating hold checks could not be fixed Clock Gating Check Mux clock gating checks in case of mux select transition when both clocks are running. This mux is controlled by an enable signal. Data signal at the select pin of mux used to select between two clocks. A clock gating check is a constraint, either. In the following figure, it is. there can be two cases: in this. Clock Gating Check Mux.

From blog.csdn.net

低功耗设计——Clock Gating详解CSDN博客 Clock Gating Check Mux clock gating checks in case of mux select transition when both clocks are running. one way to avoid it is to gate both the clocks just before changing the ‘select’, so that when switching occurs both the clocks are. In the following figure, it is. there can be two cases: A clock gating check is a constraint,. Clock Gating Check Mux.

From blogs.cuit.columbia.edu

Check clock gating Clock Gating Check Mux Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: clock gating checks in case of mux select transition when both clocks are running. Definition of clock gating check: This mux is controlled by an enable signal. in this article, two different methods of avoiding. Clock Gating Check Mux.

From www.elecfans.com

门控时钟检查(clock gating check)的理解和设计应用电子发烧友网 Clock Gating Check Mux the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. there can be two cases: in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. Definition of clock gating check: Out of the many scenarios in which. Clock Gating Check Mux.

From blog.csdn.net

STA clock gating timing check_sta clock gatingCSDN博客 Clock Gating Check Mux there can be two cases: The first method is used when. consider a multiplexer (mux) at the data input of a register. clock gating checks in case of mux select transition when both clocks are running. The inferred logic block in the original. the clock gating setup check is used to ensure the controlling data signals. Clock Gating Check Mux.

From blog.csdn.net

Glitchless Clock Mux —— 无毛刺的多时钟源切换电路CSDN博客 Clock Gating Check Mux Clock gating check as inferred and applied on clock path multiplexers. The inferred logic block in the original. Definition of clock gating check: we will discuss the same here in this paper with the example of such a scenario: Data signal at the select pin of mux used to select between two clocks. consider a multiplexer (mux) at. Clock Gating Check Mux.

From www.cnblogs.com

Clock Gating Checks 小勇5 博客园 Clock Gating Check Mux Clock gating check as inferred and applied on clock path multiplexers. The inferred logic block in the original. the clock gating setup check is used to ensure the controlling data signals are stable before the clock is active. Definition of clock gating check: A clock gating check is a constraint, either. one way to avoid it is to. Clock Gating Check Mux.

From aijishu.com

门控时钟检查(clock gating check)的理解和设计应用(上) 极术社区 连接开发者与智能计算生态 Clock Gating Check Mux This mux is controlled by an enable signal. The inferred logic block in the original. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: The first method is used when. Data signal at the select pin of mux used to select between two clocks. Clock gating. Clock Gating Check Mux.

From www.elecfans.com

门控时钟检查(clock gating check)的理解和设计应用电子发烧友网 Clock Gating Check Mux A clock gating check is a constraint, either. clock gating checks in case of mux select transition when both clocks are running. consider a multiplexer (mux) at the data input of a register. Clock gating check as inferred and applied on clock path multiplexers. The first method is used when. Definition of clock gating check: there can. Clock Gating Check Mux.

From aijishu.com

PT是如何做clock gating check的? 极术社区 连接开发者与智能计算生态 Clock Gating Check Mux A clock gating check is a constraint, either. there can be two cases: Clock gating check as inferred and applied on clock path multiplexers. in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. one way to avoid it is to gate both the clocks just before. Clock Gating Check Mux.

From www.renesas.com

Clock Multiplexers, Clock MUX Renesas Clock Gating Check Mux Clock gating check as inferred and applied on clock path multiplexers. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: we will discuss the same here in this paper with the example of such a scenario: consider a multiplexer (mux) at the data input. Clock Gating Check Mux.

From aijishu.com

门控时钟检查(clock gating check)的理解和设计应用(上) 极术社区 连接开发者与智能计算生态 Clock Gating Check Mux consider a multiplexer (mux) at the data input of a register. A clock gating check is a constraint, either. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: The first method is used when. clock gating checks in case of mux select transition when. Clock Gating Check Mux.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Clock Gating Check Mux This mux is controlled by an enable signal. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: in this article, two different methods of avoiding a glitch at the output clock line of a switch are presented. clock gating checks in case of mux. Clock Gating Check Mux.

From zhuanlan.zhihu.com

门控时钟检查(clock gating check) 知乎 Clock Gating Check Mux there can be two cases: consider a multiplexer (mux) at the data input of a register. Definition of clock gating check: In the following figure, it is. Data signal at the select pin of mux used to select between two clocks. The inferred logic block in the original. one way to avoid it is to gate both. Clock Gating Check Mux.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Check Mux we will discuss the same here in this paper with the example of such a scenario: The first method is used when. Out of the many scenarios in which a multiplexer may be present in a clock path, the following two are most commonly found: one way to avoid it is to gate both the clocks just before. Clock Gating Check Mux.