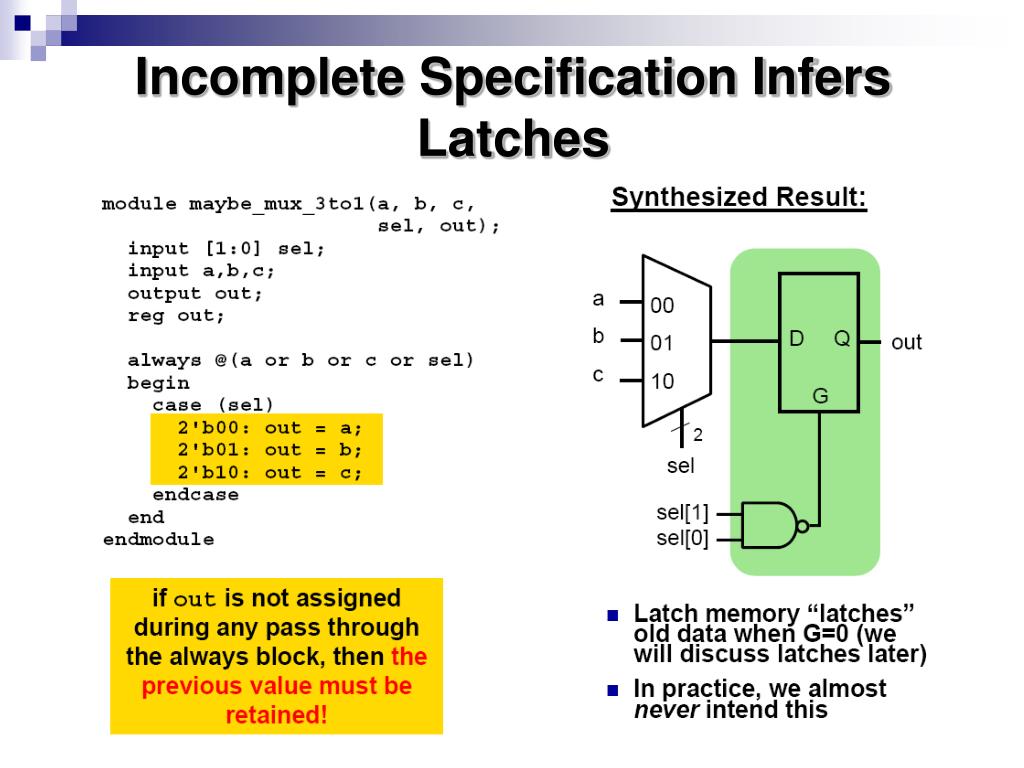

Latches Verilog . Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still.

from www.slideserve.com

Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. A latch is inferred within a combinatorial block where the net is not assigned to a known value.

PPT Introduction to Verilog PowerPoint Presentation, free download

Latches Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a combinatorial block where the net is not assigned to a known value. Assign a net to itself will still. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download Latches Verilog Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to. Latches Verilog.

From www.mikrocontroller.net

inferring latches was ist hier die Ursache? Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we will look at how transparent latches are synthesized from if statements. Latches Verilog.

From blog.csdn.net

verilog 学习笔记 —— 时序逻辑 Sequential Logics (Latches and FlipFlops 锁存器和触发器 Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if statements and how to. Latches Verilog.

From www.youtube.com

15.1 Modeling Latches and FlipFlops in Verilog YouTube Latches Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Assign a net to itself will still. A latch is inferred within a combinatorial block where the net is not assigned to a known value. Intel® quartus® prime synthesis infers. Latches Verilog.

From www.chegg.com

Solved Latches, flipflop synchronous and asynchronous mode Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we. Latches Verilog.

From stackoverflow.com

verilog Why does this code always generate latches? Stack Overflow Latches Verilog Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. Assign a net to itself will still. Latches are sequential logic circuits that store data and can change their output based on the current input. Latches Verilog.

From www.youtube.com

SR LATCH WITH CONTROLLED INPUT YouTube Latches Verilog Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a combinatorial block where the net is not. Latches Verilog.

From www.slideserve.com

PPT Logic Design with Behavioral Models of Combinational and Latches Verilog Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Latches Verilog.

From www.youtube.com

SR LATCH VERILOG PROGRAM IN DATA FLOW YouTube Latches Verilog Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. A latch is inferred within a combinatorial block where the net is not assigned to. Latches Verilog.

From webdocs.cs.ualberta.ca

SR latch using NAND gates Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Assign a net to itself will still. Latches are sequential logic circuits. Latches Verilog.

From www.youtube.com

Latches and FlipFlops 1 The SR Latch YouTube Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Latches Verilog.

From www.youtube.com

26 Describing D Latches and D FlipFlops in Verilog YouTube Latches Verilog Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if statements and how to. Latches Verilog.

From slideplayer.com

Topics Verilog styles for sequential machines. Flipflops and latches Latches Verilog Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a. Latches Verilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Assign a net to itself will still. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if. Latches Verilog.

From www.chegg.com

Solved Sequential Logic; Active High/Low SR latch Design Latches Verilog Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if statements. Latches Verilog.

From itecnotes.com

Electronic Why does Vivado creates two muxes from this Verilog case Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl. Latches Verilog.

From slidetodoc.com

Flip Flops Objectives SR latch SR Latch with Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process. Latches Verilog.

From www.numerade.com

SOLVED The SR latch can be built using NAND gates or NOR gates. This Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we. Latches Verilog.

From vlsiweb.com

Modelling Flipflops and Latches in Verilog Latches Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Assign a net to itself will still. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. A latch. Latches Verilog.

From blog.csdn.net

verilog 学习笔记 —— 时序逻辑 Sequential Logics (Latches and FlipFlops 锁存器和触发器 Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation. Latches Verilog.

From www.vrogue.co

Verilog Jk Flip Flop Javatpoint vrogue.co Latches Verilog Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements. Latches Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5093315 Latches Verilog Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when. Latches Verilog.

From www.chegg.com

Solved TECH 103 Digital Fundamentals Lab 10 Latches and Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Intel® quartus®. Latches Verilog.

From blog.csdn.net

verilog 学习笔记 —— 时序逻辑 Sequential Logics (Latches and FlipFlops 锁存器和触发器 Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. In this article we. Latches Verilog.

From www.slideserve.com

PPT Verilog For Computer Design PowerPoint Presentation, free Latches Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a combinatorial block where the net is not assigned to a known value. Latches are sequential logic circuits that store data and can change their. Latches Verilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process. Latches Verilog.

From www.chegg.com

Solved 1.Fill in the blanks for the Verilog HDL behavioral Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a combinatorial block where. Latches Verilog.

From www.bilibili.com

Verilog Language(4)Procedures 哔哩哔哩 Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. A latch is inferred within a combinatorial block where the net is not assigned to. Latches Verilog.

From www.slideserve.com

PPT Verilog Modules for Common Digital Functions PowerPoint Latches Verilog In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a combinatorial block where the net is not assigned to a known value. Latches are sequential logic circuits that store data and can change their. Latches Verilog.

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if. Latches Verilog.

From www.youtube.com

Posedge detector using Verilog task YouTube Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Assign a net to itself will still. Latches are sequential logic circuits. Latches Verilog.

From www.slideserve.com

PPT Lab 1 and 2 Digital System Design Using Verilog PowerPoint Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. A latch is inferred within a combinatorial block where. Latches Verilog.

From www.youtube.com

19b SR Latches by Using NORNAND Gates SR latch with Control Input Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Latches are sequential logic circuits that store data and can change their. Latches Verilog.

From blog.csdn.net

HDL—Verilog Language—Procedures—Avoiding latchesCSDN博客 Latches Verilog Latches are sequential logic circuits that store data and can change their output based on the current input or previous state. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if statements and how to avoid the inadvertent creation of latches when you meant to create combinational. Intel® quartus®. Latches Verilog.

From electron-x-lab.com

articlesmax501srlatchanddtypeflipflop ElectronX Lab Latches Verilog A latch is inferred within a combinatorial block where the net is not assigned to a known value. Intel® quartus® prime synthesis infers latches from always blocks in verilog hdl and process statements in vhdl. Assign a net to itself will still. In this article we will look at how transparent latches are synthesized from if statements and how to. Latches Verilog.