Place Design Error Vivado . Check if opt_design has removed all the leaf cells of your design. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Does the design have outputs? Also, are you sure you are not running synthesis and. Are the i/o pins assigned in the constraints? For using this option, you first synthesize the design and open the. A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. As you probably told vivado that you are using the zybo, it cannot solve this issue alone. Change the io voltage of gt_reset to 1.2 v. The first thing that i have noticed, is that you are using vivado 2016.2. So, if you have an external clock source,. It is common for vivado to report placer problems when register utilization reaches levels of 75%.

from xilinx.github.io

For using this option, you first synthesize the design and open the. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Are the i/o pins assigned in the constraints? The first thing that i have noticed, is that you are using vivado 2016.2. Check if opt_design has removed all the leaf cells of your design. Change the io voltage of gt_reset to 1.2 v. A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. So, if you have an external clock source,. Does the design have outputs?

Vivado Design Flow FPGA Design with Vivado

Place Design Error Vivado So, if you have an external clock source,. For using this option, you first synthesize the design and open the. Change the io voltage of gt_reset to 1.2 v. The first thing that i have noticed, is that you are using vivado 2016.2. So, if you have an external clock source,. Check if opt_design has removed all the leaf cells of your design. Are the i/o pins assigned in the constraints? As you probably told vivado that you are using the zybo, it cannot solve this issue alone. Also, are you sure you are not running synthesis and. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Does the design have outputs? A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado.

From community.element14.com

Vivado The Design is Empty [solved] element14 Community Place Design Error Vivado As you probably told vivado that you are using the zybo, it cannot solve this issue alone. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Are the i/o pins assigned in the constraints? So, if you have an external clock source,. For using this option, you. Place Design Error Vivado.

From slideplayer.com

Vivado Design Flow for SoC ppt download Place Design Error Vivado Also, are you sure you are not running synthesis and. A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. Does the design have outputs? So, if you have an external clock source,. Check if opt_design has removed all the leaf cells of your design. The first thing that i. Place Design Error Vivado.

From blog.csdn.net

Vivado报错 [Place 3099] Placer failed with error ‘IO Clock Placer Place Design Error Vivado Also, are you sure you are not running synthesis and. The first thing that i have noticed, is that you are using vivado 2016.2. For using this option, you first synthesize the design and open the. Check if opt_design has removed all the leaf cells of your design. Are the i/o pins assigned in the constraints? So, if you have. Place Design Error Vivado.

From www.xilinx.com

Design Entry & Implementation Place Design Error Vivado Does the design have outputs? Are the i/o pins assigned in the constraints? Check if opt_design has removed all the leaf cells of your design. The first thing that i have noticed, is that you are using vivado 2016.2. Also, are you sure you are not running synthesis and. Change the io voltage of gt_reset to 1.2 v. For using. Place Design Error Vivado.

From design.udlvirtual.edu.pe

Vivado Design Suite Design Talk Place Design Error Vivado Are the i/o pins assigned in the constraints? It is common for vivado to report placer problems when register utilization reaches levels of 75%. As you probably told vivado that you are using the zybo, it cannot solve this issue alone. A user asks for help with a place design error when generating a random number using lfsr algorithm in. Place Design Error Vivado.

From slideplayer.com

Vivado Design Flow for SoC ppt download Place Design Error Vivado Also, are you sure you are not running synthesis and. Does the design have outputs? Change the io voltage of gt_reset to 1.2 v. Check if opt_design has removed all the leaf cells of your design. Are the i/o pins assigned in the constraints? So, if you have an external clock source,. The base.tcl on image v2.0 is verified and. Place Design Error Vivado.

From forum.digilent.com

Cmod A7 Vivado 2021.1 Place 30574 error FPGA Digilent Forum Place Design Error Vivado The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Change the io voltage of gt_reset to 1.2 v. The first thing that i have noticed, is that you are using vivado. Place Design Error Vivado.

From github.com

Build failed for ArtyA7 Vivado ERROR [DRC UTLZ1] Resource Place Design Error Vivado Also, are you sure you are not running synthesis and. Does the design have outputs? As you probably told vivado that you are using the zybo, it cannot solve this issue alone. Change the io voltage of gt_reset to 1.2 v. Check if opt_design has removed all the leaf cells of your design. So, if you have an external clock. Place Design Error Vivado.

From support.xilinx.com

000034812 Vivado 2023.1 Implementation ERROR [Place 30342] pblock Place Design Error Vivado Also, are you sure you are not running synthesis and. A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. Does the design have outputs? As you probably told vivado that you are using the zybo, it cannot solve this issue alone. So, if you have an external clock source,.. Place Design Error Vivado.

From www.allaboutcircuits.com

Design Implementation in the Xilinx Vivado Design Suite News Place Design Error Vivado So, if you have an external clock source,. Are the i/o pins assigned in the constraints? A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. Also, are you sure you are not running synthesis and. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while. Place Design Error Vivado.

From blog.csdn.net

ERRORPlace713_vivado place 30713CSDN博客 Place Design Error Vivado A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. Are the i/o pins assigned in the constraints? Does the design have outputs? Check if opt_design has removed all the leaf cells of your design. Also, are you sure you are not running synthesis and. The first thing that i. Place Design Error Vivado.

From nuclearrambo.com

Programming the Zynq 7000 with Vivado 2019.2 and Vitis Place Design Error Vivado The first thing that i have noticed, is that you are using vivado 2016.2. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. Change the io voltage. Place Design Error Vivado.

From www.youtube.com

Tutorial 2 How to create testbench and simulate design in Xilinx Vivado Place Design Error Vivado The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. So, if you have an external clock source,. A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. As you probably told vivado that you are using the. Place Design Error Vivado.

From surf-vhdl.com

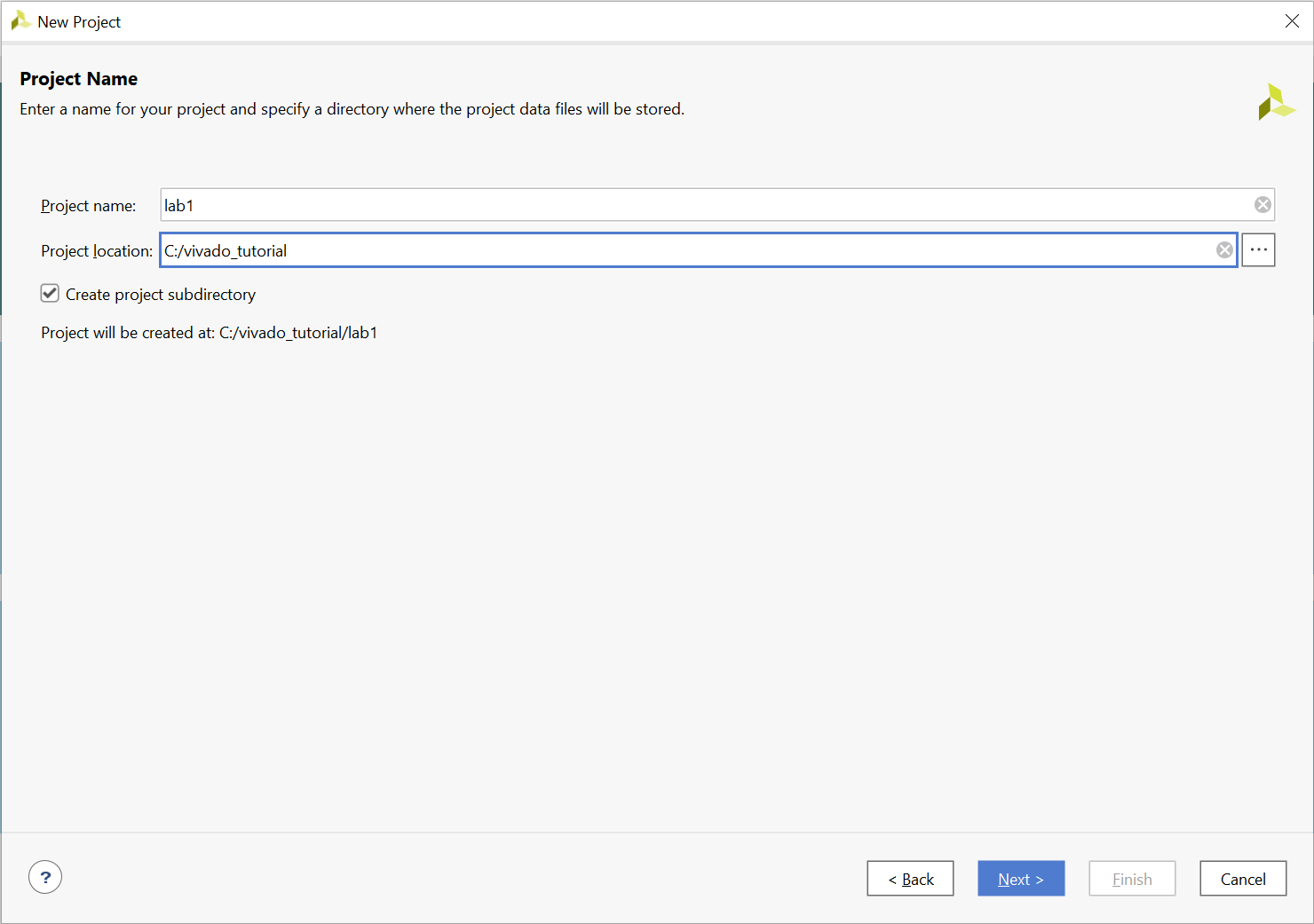

Vivado Project Tutorial SurfVHDL Place Design Error Vivado So, if you have an external clock source,. Does the design have outputs? The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Also, are you sure you are not running synthesis and. The first thing that i have noticed, is that you are using vivado 2016.2. Check. Place Design Error Vivado.

From blog.csdn.net

Vivado报错 [Place 3099] Placer failed with error ‘IO Clock Placer Place Design Error Vivado A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. It is common for vivado to report placer problems when register utilization reaches levels of 75%. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Change the. Place Design Error Vivado.

From support.xilinx.com

Vivado 2020.2 place_design physical optimization causes incorrect logic Place Design Error Vivado It is common for vivado to report placer problems when register utilization reaches levels of 75%. As you probably told vivado that you are using the zybo, it cannot solve this issue alone. Change the io voltage of gt_reset to 1.2 v. So, if you have an external clock source,. Does the design have outputs? The base.tcl on image v2.0. Place Design Error Vivado.

From blog.csdn.net

vivado 开发过程中所遇错误类型一览_synth 86859CSDN博客 Place Design Error Vivado For using this option, you first synthesize the design and open the. Does the design have outputs? The first thing that i have noticed, is that you are using vivado 2016.2. Also, are you sure you are not running synthesis and. Are the i/o pins assigned in the constraints? So, if you have an external clock source,. Check if opt_design. Place Design Error Vivado.

From github.com

Place design Error (Implementation failed) · Issue 476 · Xilinx/PYNQ Place Design Error Vivado The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. As you probably told vivado that you are using the zybo, it cannot solve this issue alone. The first thing that i have noticed, is that you are using vivado 2016.2. Also, are you sure you are not. Place Design Error Vivado.

From forum.digilent.com

Cmod A7 Vivado 2021.1 Place 30574 error FPGA Digilent Forum Place Design Error Vivado Check if opt_design has removed all the leaf cells of your design. As you probably told vivado that you are using the zybo, it cannot solve this issue alone. Does the design have outputs? Also, are you sure you are not running synthesis and. For using this option, you first synthesize the design and open the. The first thing that. Place Design Error Vivado.

From github.com

Place design Error (Implementation failed) · Issue 476 · Xilinx/PYNQ Place Design Error Vivado A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Check if opt_design has removed all the leaf cells of your design. For using this option, you first. Place Design Error Vivado.

From xilinx.github.io

Xilinx Design Constraints FPGA Design with Vivado Place Design Error Vivado So, if you have an external clock source,. Check if opt_design has removed all the leaf cells of your design. It is common for vivado to report placer problems when register utilization reaches levels of 75%. The first thing that i have noticed, is that you are using vivado 2016.2. The base.tcl on image v2.0 is verified and tested based. Place Design Error Vivado.

From insights.sigasi.com

AMD/Xilinx Vivado Integration Sigasi Place Design Error Vivado Are the i/o pins assigned in the constraints? Does the design have outputs? A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Check if opt_design has removed all the leaf cells of your. Place Design Error Vivado.

From www.allaboutcircuits.com

Design Implementation in the Xilinx Vivado Design Suite News Place Design Error Vivado The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Are the i/o pins assigned in the constraints? The first thing that i have noticed, is that you are using vivado 2016.2. Check if opt_design has removed all the leaf cells of your design. Change the io voltage. Place Design Error Vivado.

From xilinx.github.io

Vivado Design Flow FPGA Design with Vivado Place Design Error Vivado The first thing that i have noticed, is that you are using vivado 2016.2. For using this option, you first synthesize the design and open the. Change the io voltage of gt_reset to 1.2 v. Are the i/o pins assigned in the constraints? As you probably told vivado that you are using the zybo, it cannot solve this issue alone.. Place Design Error Vivado.

From eyunzhu.com

vivado仿真出错: Please check the Tcl console or log files for more Place Design Error Vivado Change the io voltage of gt_reset to 1.2 v. It is common for vivado to report placer problems when register utilization reaches levels of 75%. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. So, if you have an external clock source,. A user asks for help. Place Design Error Vivado.

From forum.digilent.com

Vivado 121411 Cannot set LOC property of ports. Digilent Place Design Error Vivado A user asks for help with a place design error when generating a random number using lfsr algorithm in vivado. For using this option, you first synthesize the design and open the. Change the io voltage of gt_reset to 1.2 v. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Check if opt_design. Place Design Error Vivado.

From xilinx.github.io

Vivado Design Flow FPGA Design with Vivado Place Design Error Vivado So, if you have an external clock source,. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Change the io voltage of gt_reset to 1.2 v. Check if opt_design has removed all the leaf cells of your design. Does the design have outputs? For using this option, you first synthesize the design and. Place Design Error Vivado.

From forum.digilent.com

Cmod A7 Vivado 2021.1 Place 30574 error FPGA Digilent Forum Place Design Error Vivado The first thing that i have noticed, is that you are using vivado 2016.2. Change the io voltage of gt_reset to 1.2 v. Check if opt_design has removed all the leaf cells of your design. So, if you have an external clock source,. As you probably told vivado that you are using the zybo, it cannot solve this issue alone.. Place Design Error Vivado.

From forum.digilent.com

Cmod A7 Vivado 2021.1 Place 30574 error FPGA Digilent Forum Place Design Error Vivado As you probably told vivado that you are using the zybo, it cannot solve this issue alone. For using this option, you first synthesize the design and open the. The first thing that i have noticed, is that you are using vivado 2016.2. Check if opt_design has removed all the leaf cells of your design. Are the i/o pins assigned. Place Design Error Vivado.

From ez.analog.com

Vivado SDK building error on KC705 platform Q&A FPGA Reference Place Design Error Vivado So, if you have an external clock source,. Check if opt_design has removed all the leaf cells of your design. Does the design have outputs? It is common for vivado to report placer problems when register utilization reaches levels of 75%. As you probably told vivado that you are using the zybo, it cannot solve this issue alone. Change the. Place Design Error Vivado.

From stackoverflow.com

verilog In Vivado, how to "Create Port" in a "Block Design" that is Place Design Error Vivado Also, are you sure you are not running synthesis and. So, if you have an external clock source,. Check if opt_design has removed all the leaf cells of your design. For using this option, you first synthesize the design and open the. Does the design have outputs? The base.tcl on image v2.0 is verified and tested based on vivado 2016.1,. Place Design Error Vivado.

From xilinx.github.io

Vivado Design Flow FPGA Design with Vivado Place Design Error Vivado Are the i/o pins assigned in the constraints? The first thing that i have noticed, is that you are using vivado 2016.2. Change the io voltage of gt_reset to 1.2 v. So, if you have an external clock source,. For using this option, you first synthesize the design and open the. Also, are you sure you are not running synthesis. Place Design Error Vivado.

From support.xilinx.com

000034812 Vivado 2023.1 Implementation ERROR [Place 30342] pblock Place Design Error Vivado Check if opt_design has removed all the leaf cells of your design. It is common for vivado to report placer problems when register utilization reaches levels of 75%. Also, are you sure you are not running synthesis and. Are the i/o pins assigned in the constraints? As you probably told vivado that you are using the zybo, it cannot solve. Place Design Error Vivado.

From dokumen.tips

(PDF) Vivado Design Suite Tutorial Xilinx · “atomic” commands, synth Place Design Error Vivado The first thing that i have noticed, is that you are using vivado 2016.2. So, if you have an external clock source,. For using this option, you first synthesize the design and open the. Does the design have outputs? It is common for vivado to report placer problems when register utilization reaches levels of 75%. Also, are you sure you. Place Design Error Vivado.

From www.allaboutcircuits.com

Design Implementation in the Xilinx Vivado Design Suite News Place Design Error Vivado The first thing that i have noticed, is that you are using vivado 2016.2. The base.tcl on image v2.0 is verified and tested based on vivado 2016.1, while there is no guarantee that the same tcl. Change the io voltage of gt_reset to 1.2 v. For using this option, you first synthesize the design and open the. It is common. Place Design Error Vivado.