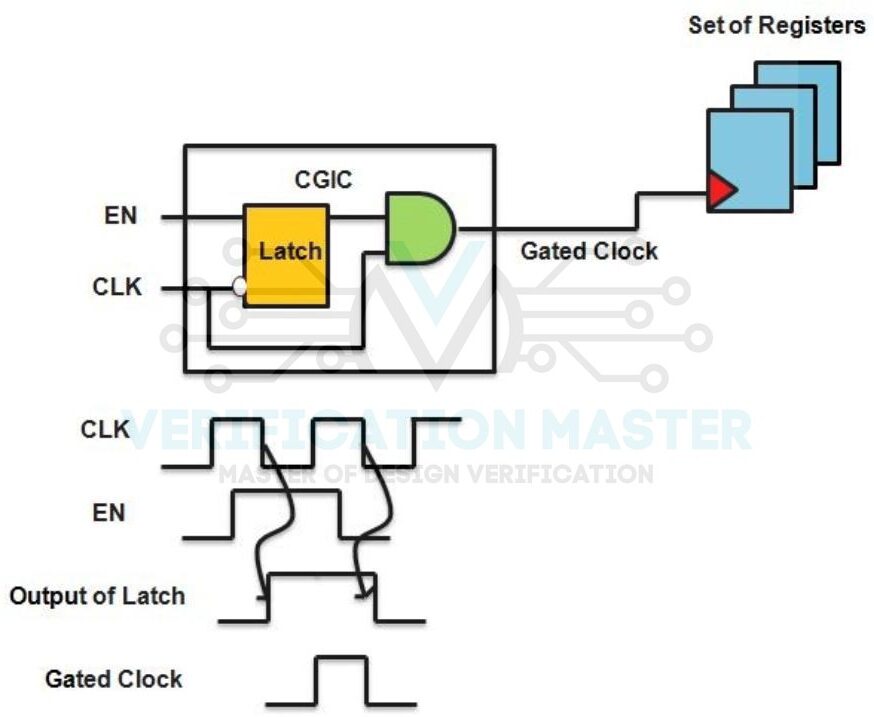

Types Of Clock Gating In Vlsi . In this article, we will go through the architecture, function, and. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Power cmos vlsi design 4th ed. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Clock gating can be implemented using below two methods : In this method, an and or or gate is used. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks.

from vlsimaster.com

In this method, an and or or gate is used. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. In this article, we will go through the architecture, function, and. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Clock gating can be implemented using below two methods : Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Power cmos vlsi design 4th ed.

Clock Gating VLSI Master

Types Of Clock Gating In Vlsi Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this method, an and or or gate is used. Power cmos vlsi design 4th ed. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this article, we will go through the architecture, function, and. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Clock gating can be implemented using below two methods :

From www.youtube.com

Integrated Clock Gating Cell ICG Cell in VLSI Clock Gating Cell Types Of Clock Gating In Vlsi Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Clock gating can be implemented using below two methods : In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. 17 clock gating the best way to reduce the activity is to. Types Of Clock Gating In Vlsi.

From dokumen.tips

(PDF) Integrated Clock Gating Cell _ VLSI Pro DOKUMEN.TIPS Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Clock gating can be implemented using below two methods : Clock gating is a technique employed. Types Of Clock Gating In Vlsi.

From vlsimaster.com

Clock Jitter VLSI Master Types Of Clock Gating In Vlsi In this method, an and or or gate is used. Power cmos vlsi design 4th ed. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In this article, we will go through the architecture, function, and. Clock gating can be implemented using below two methods : In digital vlsi designs, the. Types Of Clock Gating In Vlsi.

From eureka.patsnap.com

Activity correlation based optimal clustering for clock gating for Types Of Clock Gating In Vlsi Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. In this article, we will go through the architecture, function, and. In this method, an and or or gate is used. Clock. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

A Review on Clock Gating Methodologies for power minimization in VLSI Types Of Clock Gating In Vlsi In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this article, we will go through the architecture, function, and. In this method, an and or or. Types Of Clock Gating In Vlsi.

From ivlsi.com

Clock Tree Synthesis in VLSI Physical Design Types Of Clock Gating In Vlsi Clock gating can be implemented using below two methods : Power cmos vlsi design 4th ed. In this article, we will go through the architecture, function, and. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Integrated clock gating (icg) cell is a specially designed cell that is. Types Of Clock Gating In Vlsi.

From vlsimaster.com

Clock Gating VLSI Master Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. In this article, we will go through the architecture, function, and. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this method, an and. Types Of Clock Gating In Vlsi.

From www.youtube.com

PD Lec 52 CTS Algorithms CTS Clock Tree Synthesis VLSI Physical Types Of Clock Gating In Vlsi In this method, an and or or gate is used. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Power cmos vlsi design 4th ed. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go through the architecture,. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

Figure 7 from A Review on Clock Gating Methodologies for power Types Of Clock Gating In Vlsi In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In this method, an and or or gate is used. Integrated clock gating (icg) cell is a specially designed cell that. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

Figure 2.1 from Deterministic clock gating for low power VLSI design Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this article, we will go through the architecture, function, and. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this method, an and. Types Of Clock Gating In Vlsi.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI Types Of Clock Gating In Vlsi In this article, we will go through the architecture, function, and. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Clock gating can be implemented using below two methods : In digital vlsi designs,. Types Of Clock Gating In Vlsi.

From siliconvlsi.com

What do you mean by clock Jitter? Siliconvlsi Types Of Clock Gating In Vlsi Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go through the architecture, function, and. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this method, an and or or gate is used. Clock. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

A Review on Clock Gating Methodologies for power minimization in VLSI Types Of Clock Gating In Vlsi 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. In. Types Of Clock Gating In Vlsi.

From www.slideshare.net

Clock gating Types Of Clock Gating In Vlsi Clock gating can be implemented using below two methods : Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In this method, an and or or gate is used. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Integrated. Types Of Clock Gating In Vlsi.

From vlsi-soc.blogspot.com

VLSI SoC Design Integrated Clock and Power Gating Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. In this article, we will go through the architecture, function, and. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In digital vlsi designs,. Types Of Clock Gating In Vlsi.

From blogs.cuit.columbia.edu

Check clock gating Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Clock gating can be implemented using below two methods : Integrated clock gating (icg) cell. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

[PDF] Deterministic clock gating for low power VLSI design Semantic Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. Clock gating can be implemented using below two methods : In this method, an and or or gate is used. In this article, we will go through the architecture, function, and. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In digital vlsi designs, the. Types Of Clock Gating In Vlsi.

From www.vrogue.co

Vlsi Soc Design Clock Gating Integrated Cell vrogue.co Types Of Clock Gating In Vlsi Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go through the architecture, function, and. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Clock gating is a technique employed in the design of digital. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

Clock gating — A power optimizing technique for VLSI circuits Types Of Clock Gating In Vlsi In this method, an and or or gate is used. In this article, we will go through the architecture, function, and. Power cmos vlsi design 4th ed. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. 17 clock gating the best way to reduce the activity is to. Types Of Clock Gating In Vlsi.

From www.vrogue.co

Clock Gating Cell And Integrated Clock Gating Cell Ic vrogue.co Types Of Clock Gating In Vlsi Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this method, an and or or gate is used. In this article, we will go through the architecture, function, and. Clock gating can be implemented using below two methods : 17 clock gating the best way to reduce the activity is to. Types Of Clock Gating In Vlsi.

From www.youtube.com

Understanding Clock Tree Synthesis (CTS) in VLSI A Comprehensive Guide Types Of Clock Gating In Vlsi Clock gating can be implemented using below two methods : In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. In this method, an and or or gate is used. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In. Types Of Clock Gating In Vlsi.

From www.semanticscholar.org

Figure 3 from Clock Gating Based Low Power ALU Design Semantic Scholar Types Of Clock Gating In Vlsi In this method, an and or or gate is used. Power cmos vlsi design 4th ed. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Clock gating can be implemented. Types Of Clock Gating In Vlsi.

From www.researchgate.net

3 Clock gating of the main clock to some component Download Types Of Clock Gating In Vlsi In this article, we will go through the architecture, function, and. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Power cmos vlsi design 4th ed. Clock gating can be implemented. Types Of Clock Gating In Vlsi.

From www.slideserve.com

PPT 2. VLSI Basic PowerPoint Presentation, free download ID4809887 Types Of Clock Gating In Vlsi In this method, an and or or gate is used. In this article, we will go through the architecture, function, and. Clock gating can be implemented using below two methods : Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Power cmos vlsi design 4th ed. 17 clock gating the best way. Types Of Clock Gating In Vlsi.

From www.youtube.com

Clock Domain Crossing Handshake Synchronizer CDC Technique VLSI Types Of Clock Gating In Vlsi Clock gating can be implemented using below two methods : Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Power cmos vlsi design 4th ed. In this article, we will go. Types Of Clock Gating In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Types Of Clock Gating In Vlsi 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this method, an and or or gate is used. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Integrated clock gating (icg) cell is a specially designed cell that. Types Of Clock Gating In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Types Of Clock Gating In Vlsi Clock gating can be implemented using below two methods : In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Power cmos vlsi design 4th ed. 17 clock gating the best. Types Of Clock Gating In Vlsi.

From vlsibyjim.blogspot.com

VLSI Basics Static Time Analysis Basics Types Of Clock Gating In Vlsi 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Clock gating can be implemented using below two methods : In this article, we will go through the architecture, function, and. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power.. Types Of Clock Gating In Vlsi.

From www.researchgate.net

Waveforms showing edge combinations due to DET clock gating and example Types Of Clock Gating In Vlsi Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In this article, we will go through the architecture, function, and. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Integrated clock gating (icg) cell is a specially designed cell. Types Of Clock Gating In Vlsi.

From www.youtube.com

Lecture6 VLSI System Testing Clock Skew Types YouTube Types Of Clock Gating In Vlsi In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. In this method, an and or or gate is used. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Clock gating can be implemented using below two methods : Power. Types Of Clock Gating In Vlsi.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Types Of Clock Gating In Vlsi Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. Power cmos vlsi design 4th ed. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other. Types Of Clock Gating In Vlsi.

From vlsimaster.com

Clock Gating VLSI Master Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. In this method, an and or or gate is used. In this article, we will go through the architecture, function, and. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other. Types Of Clock Gating In Vlsi.

From www.vlsiguru.com

pdbasicsClocktreesynthesis VLSI Guru Types Of Clock Gating In Vlsi Clock gating is a technique employed in the design of digital circuits, particularly in vlsi, to reduce power. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this article, we will go through the architecture, function, and. Power cmos vlsi design 4th ed. In digital vlsi designs,. Types Of Clock Gating In Vlsi.

From teamvlsi.blogspot.com

Team VLSI Types Of Clock Gating In Vlsi Power cmos vlsi design 4th ed. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. In this method, an and or or gate is used. In digital vlsi designs, the most frequently switching element are clock elements (buffers and other gates used to transport clock signal. Clock gating. Types Of Clock Gating In Vlsi.

From vlsiuniverse.blogspot.com

Clock gating interview questions VLSI n EDA Types Of Clock Gating In Vlsi In this article, we will go through the architecture, function, and. In this method, an and or or gate is used. 17 clock gating the best way to reduce the activity is to turn off the clock to registers in unused blocks. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Power. Types Of Clock Gating In Vlsi.