Twr Memory Timing . Higher values are often better for stability. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. Twr isn't a timing on intel. The minimum time in cycles it takes a row to complete a full cycle. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. If this is set too short it can cause corruption of. This can be determined by; Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. Trc = tras + trp. This is easy to test in os using memtweakit or msi dragon ball. I found that higher twr will actually make the. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Memory timings on the other hand are measured in dividual clock cycles. Memory frequency is measured in the unit for frequency being hertz.

from www.slideserve.com

Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. This is easy to test in os using memtweakit or msi dragon ball. I found that higher twr will actually make the. Memory timings on the other hand are measured in dividual clock cycles. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. This can be determined by; Cas latency is the most widely talked about and compared memory timing.

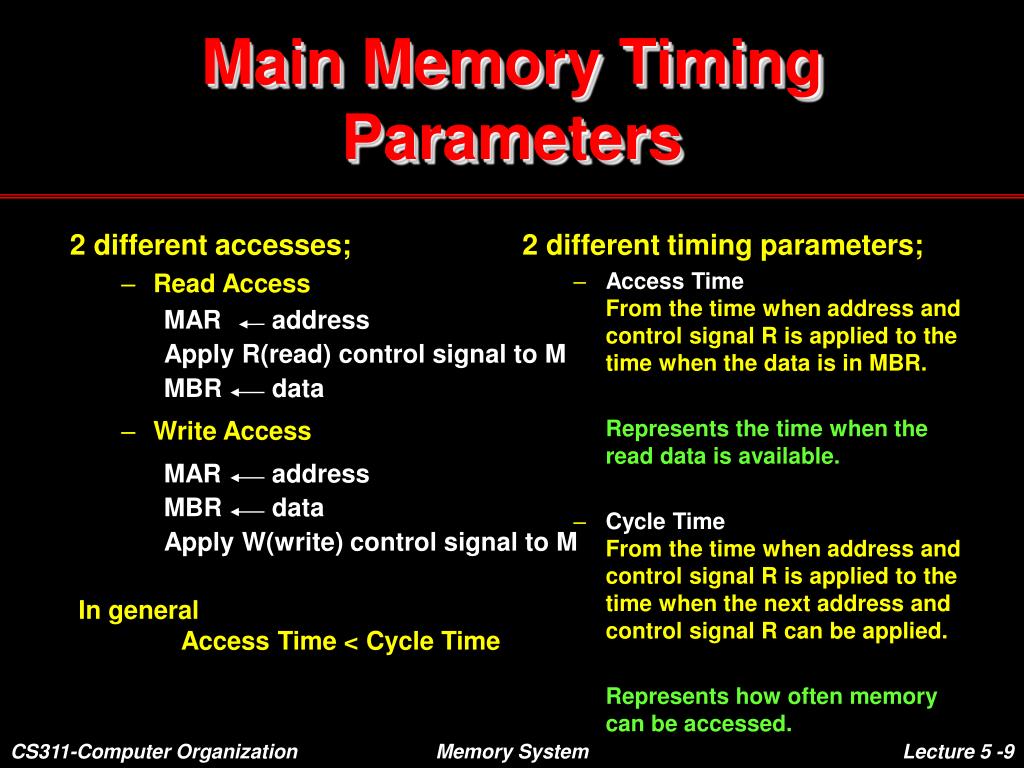

PPT Lecture 5 Storage System PowerPoint Presentation, free download

Twr Memory Timing I found that higher twr will actually make the. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. Memory timings on the other hand are measured in dividual clock cycles. If this is set too short it can cause corruption of. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. Twr isn't a timing on intel. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. This can be determined by; The minimum time in cycles it takes a row to complete a full cycle. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. Memory frequency is measured in the unit for frequency being hertz. I found that higher twr will actually make the. Cas latency is the most widely talked about and compared memory timing. Higher values are often better for stability. Trc = tras + trp.

From in.element14.com

TWRMEM Nxp Daughter Board, Tower System Memory Module, Rapid Twr Memory Timing This is easy to test in os using memtweakit or msi dragon ball. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. Cas latency is the most widely talked about and compared memory timing. Trc = tras + trp. Twr write recovery time, or the time that must. Twr Memory Timing.

From www.researchgate.net

A twotime slot TWR system, where each source node coordinates Twr Memory Timing Twr isn't a timing on intel. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. If this is set too short it can cause. Twr Memory Timing.

From www.mdpi.com

Computers Free FullText Timing and Performance Metrics for TWR Twr Memory Timing I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Hertz is cycles per second, meaning if you have something that is running at. Twr Memory Timing.

From www.slideserve.com

PPT Week 11 Memory Interfacing PowerPoint Presentation, free Twr Memory Timing Cas latency is the most widely talked about and compared memory timing. This is easy to test in os using memtweakit or msi dragon ball. The minimum time in cycles it takes a row to complete a full cycle. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering. Twr Memory Timing.

From www.slideserve.com

PPT Computer Architecture Memory SRAM, DRAM PowerPoint Presentation Twr Memory Timing Trc = tras + trp. If this is set too short it can cause corruption of. I found that higher twr will actually make the. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. This can be determined by; When you set twr, your motherboard will calculate twr. Twr Memory Timing.

From www.youtube.com

MP Module 2 Timing Diagram for Memory Read and Write Operation YouTube Twr Memory Timing Memory frequency is measured in the unit for frequency being hertz. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. When you set twr, your motherboard will calculate. Twr Memory Timing.

From www.researchgate.net

(PDF) Timing and Performance Metrics for TWRK70F120M device Twr Memory Timing When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. If this is set too short it can cause corruption of. I found that higher twr will actually make the. Twr isn't a timing on intel. Memory frequency is measured in the unit for frequency being hertz. Higher values are often. Twr Memory Timing.

From www.slideserve.com

PPT SEMICONDUCTOR MEMORIES PowerPoint Presentation, free download Twr Memory Timing Trc = tras + trp. Cas latency is the most widely talked about and compared memory timing. The minimum time in cycles it takes a row to complete a full cycle. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. Memory frequency is measured. Twr Memory Timing.

From slideplayer.com

ECE 353 Introduction to Microprocessor Systems ppt download Twr Memory Timing The minimum time in cycles it takes a row to complete a full cycle. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. Higher values are often better for stability. Twr isn't a timing on intel. Twr write recovery time, or the time that. Twr Memory Timing.

From www.slideserve.com

PPT Computer Memory Basic Concepts PowerPoint Presentation ID2427233 Twr Memory Timing The minimum time in cycles it takes a row to complete a full cycle. Cas latency is the most widely talked about and compared memory timing. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. Hertz is cycles per second, meaning if you have something that is running at. Twr Memory Timing.

From www.hardwaretimes.com

Auto Memory Overclocking May Come with AMD's Ryzen 7000 CPUs for Easy Twr Memory Timing When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. Memory frequency is measured in the unit for frequency being hertz. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. This is easy to test in os using memtweakit. Twr Memory Timing.

From www.slideserve.com

PPT SDRAM Memory Controller PowerPoint Presentation, free download Twr Memory Timing The minimum time in cycles it takes a row to complete a full cycle. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. The cl timing is an exact. Twr Memory Timing.

From www.slideserve.com

PPT Semiconductor Memories PowerPoint Presentation, free download Twr Memory Timing Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. The minimum time in cycles it takes a row to complete a full cycle. If this is set too short it can cause corruption of. Trc = tras + trp. When you set twr, your motherboard will calculate twr +. Twr Memory Timing.

From www.slideserve.com

PPT Interface Design Compute Memory Timing PowerPoint Presentation Twr Memory Timing I found that higher twr will actually make the. Memory timings on the other hand are measured in dividual clock cycles. Cas latency is the most widely talked about and compared memory timing. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Twr isn't a timing on intel.. Twr Memory Timing.

From www.slideserve.com

PPT Unit 4 Memory System Design PowerPoint Presentation, free Twr Memory Timing I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. If this is set too short it can cause corruption of. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario.. Twr Memory Timing.

From www.slideserve.com

PPT Lecture 5 Storage System PowerPoint Presentation, free download Twr Memory Timing Trc = tras + trp. Higher values are often better for stability. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. I found that higher twr. Twr Memory Timing.

From www.mdpi.com

Computers Free FullText Timing and Performance Metrics for TWR Twr Memory Timing Higher values are often better for stability. This can be determined by; Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. The minimum time in cycles it takes a row to complete a full cycle. When you set twr, your motherboard will calculate twr + tcwl + 6,. Twr Memory Timing.

From www.slideserve.com

PPT SEMICONDUCTOR MEMORIES PowerPoint Presentation, free download Twr Memory Timing Higher values are often better for stability. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. If this is set too short it can cause corruption of. I found that higher twr will actually make the. When you set twr, your motherboard will calculate twr + tcwl +. Twr Memory Timing.

From www.slideserve.com

PPT Microprocessor System Design Memory Timing PowerPoint Twr Memory Timing Cas latency is the most widely talked about and compared memory timing. Memory timings on the other hand are measured in dividual clock cycles. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Memory frequency is measured in the unit for frequency being hertz. When you set twr,. Twr Memory Timing.

From www.slideserve.com

PPT Microprocessor System Design Memory Timing PowerPoint Twr Memory Timing Memory timings on the other hand are measured in dividual clock cycles. Twr isn't a timing on intel. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. When. Twr Memory Timing.

From slideplayer.com

Computer Architecture Lecture 10b Memory Latency ppt download Twr Memory Timing I found that higher twr will actually make the. Memory frequency is measured in the unit for frequency being hertz. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. This is easy to test in os using memtweakit or msi dragon ball. Trc = tras. Twr Memory Timing.

From www.youtube.com

Memory Read and Write Machine Cycles in 8085 Microprocessor Timing Twr Memory Timing Higher values are often better for stability. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. Memory frequency is measured in the unit for frequency being hertz. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the. Twr Memory Timing.

From www.slideserve.com

PPT Week 11 Memory Interfacing PowerPoint Presentation, free Twr Memory Timing I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. I found that higher twr will actually make the. Trc = tras + trp. Higher values are often better for stability. Hertz is cycles per second, meaning if you have something that is running at. Twr Memory Timing.

From www.binarytides.com

5 Software Tools to check RAM timings on Windows BinaryTides Twr Memory Timing Memory timings on the other hand are measured in dividual clock cycles. If this is set too short it can cause corruption of. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Higher values are often better for stability. Trc = tras + trp. Cas latency is the. Twr Memory Timing.

From www.slideserve.com

PPT Interface Design DRAM Modules PowerPoint Presentation, free Twr Memory Timing Memory frequency is measured in the unit for frequency being hertz. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. Trc = tras + trp. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. This can be determined. Twr Memory Timing.

From www.mdpi.com

Computers Free FullText Timing and Performance Metrics for TWR Twr Memory Timing Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Twr isn't a timing on intel. This can be determined by; This is easy to test in os using memtweakit or msi dragon ball. I'm on the tightening timings step of this guide, and i'm not seeing gains versus. Twr Memory Timing.

From www.slideserve.com

PPT Computer Memory Basic Concepts PowerPoint Presentation ID2427233 Twr Memory Timing Higher values are often better for stability. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. I'm on the tightening timings step of this guide, and i'm not seeing gains versus the xmp ii settings when lowering trrdl, tfaw, and twr. The minimum time in cycles it takes a row. Twr Memory Timing.

From www.slideserve.com

PPT Digital Integrated Circuits A Design Perspective PowerPoint Twr Memory Timing Trc = tras + trp. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. Cas latency is the most widely talked about and compared memory timing. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre.. Twr Memory Timing.

From memory.net

HP EliteDesk 800 G2 Series SFF/TWR Memory Upgrades Twr Memory Timing Twr isn't a timing on intel. Higher values are often better for stability. This can be determined by; Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. Cas latency. Twr Memory Timing.

From www.slideserve.com

PPT SYSTEM CLOCK PowerPoint Presentation ID2631546 Twr Memory Timing Trc = tras + trp. The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. This can be determined by; The minimum time in cycles it takes a row to complete a full cycle. I found that higher twr will actually make the. Memory timings on. Twr Memory Timing.

From www.slideserve.com

PPT ENGIN 112 Intro to Electrical and Computer Engineering Lecture 30 Twr Memory Timing The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. I found that higher twr will actually make the. Twr write recovery time, or the time that must elapse between a valid write operation and the precharging of another bank. Higher values are often better for. Twr Memory Timing.

From www.youtube.com

Memory Timing Tweaking & Avoiding Stutter 2/2 (Updated in description Twr Memory Timing Memory timings on the other hand are measured in dividual clock cycles. Memory frequency is measured in the unit for frequency being hertz. This is easy to test in os using memtweakit or msi dragon ball. Higher values are often better for stability. I found that higher twr will actually make the. Perfect ram timing rule for extreme overclocked timings. Twr Memory Timing.

From www.researchgate.net

(PDF) Timing and Performance Metrics for TWRK70F120M Device Twr Memory Timing Memory timings on the other hand are measured in dividual clock cycles. Perfect ram timing rule for extreme overclocked timings where you have to change every single timing so the ram operates. When you set twr, your motherboard will calculate twr + tcwl + 6, and feed that value to twrpre. Hertz is cycles per second, meaning if you have. Twr Memory Timing.

From www.slideserve.com

PPT MS108 Computer System I PowerPoint Presentation, free download Twr Memory Timing The cl timing is an exact number, the base time that it takes to get a response from memory in the best possible scenario. Hertz is cycles per second, meaning if you have something that is running at 5hz, you have 5 cycles per second. I found that higher twr will actually make the. Twr isn't a timing on intel.. Twr Memory Timing.

From www.slideserve.com

PPT Week 11 Memory Interfacing PowerPoint Presentation, free Twr Memory Timing This can be determined by; Memory timings on the other hand are measured in dividual clock cycles. Cas latency is the most widely talked about and compared memory timing. Twr isn't a timing on intel. Memory frequency is measured in the unit for frequency being hertz. Twr write recovery time, or the time that must elapse between a valid write. Twr Memory Timing.