Explain Cycle Time In Computer Architecture . 2ns to 0.25ns reciprocal is frequency: 0.5 ghz to 4 ghz (1 htz. Cycle time is a function of the processor’s design. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. The severity of the problem is determined by the difference in the timing of register file update (first instruction). The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. More on this later, when we discuss pipelining. The cpu repetitively performs fetch , decode , execute. The instruction cycle is the basic operation of the cpu which consist of three steps. If the design does less work during a clock cycle, it’s cycle time will be shorter.

from www.slideserve.com

The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The severity of the problem is determined by the difference in the timing of register file update (first instruction). The instruction cycle is the basic operation of the cpu which consist of three steps. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. 0.5 ghz to 4 ghz (1 htz. 2ns to 0.25ns reciprocal is frequency: The cpu repetitively performs fetch , decode , execute. Cycle time is a function of the processor’s design. More on this later, when we discuss pipelining. If the design does less work during a clock cycle, it’s cycle time will be shorter.

PPT CS334 Computer Architecture PowerPoint Presentation, free

Explain Cycle Time In Computer Architecture More on this later, when we discuss pipelining. Cycle time is a function of the processor’s design. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The cpu repetitively performs fetch , decode , execute. More on this later, when we discuss pipelining. The severity of the problem is determined by the difference in the timing of register file update (first instruction). Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. 0.5 ghz to 4 ghz (1 htz. If the design does less work during a clock cycle, it’s cycle time will be shorter. 2ns to 0.25ns reciprocal is frequency: The instruction cycle is the basic operation of the cpu which consist of three steps.

From www.geeksforgeeks.org

Computer Organization Different Instruction Cycles Explain Cycle Time In Computer Architecture Cycle time is a function of the processor’s design. The cpu repetitively performs fetch , decode , execute. If the design does less work during a clock cycle, it’s cycle time will be shorter. 2ns to 0.25ns reciprocal is frequency: Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT CPU Performance Evaluation Cycles Per Instruction (CPI Explain Cycle Time In Computer Architecture Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. If the design does less work during a clock cycle, it’s cycle. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT Computer Architecture and Design ELEN 350 PowerPoint Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. 2ns to 0.25ns reciprocal is frequency: 0.5 ghz to 4 ghz (1 htz. Cycle time is a function of the processor’s design. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The instruction cycle is. Explain Cycle Time In Computer Architecture.

From slideplayer.com

Performance COE 301 / ICS 233 Computer Organization ppt download Explain Cycle Time In Computer Architecture 2ns to 0.25ns reciprocal is frequency: The cpu repetitively performs fetch , decode , execute. Cycle time is a function of the processor’s design. More on this later, when we discuss pipelining. The instruction cycle is the basic operation of the cpu which consist of three steps. Cycle time in computer architecture refers to the time it takes for a. Explain Cycle Time In Computer Architecture.

From www.javatpoint.com

Instruction Cycle Computer Organization and Architecture Tutorial Explain Cycle Time In Computer Architecture The instruction cycle is the basic operation of the cpu which consist of three steps. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an. Explain Cycle Time In Computer Architecture.

From learnlearn.uk

Von Neumann Architecture GCSE Computer Science Theory Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. 2ns to 0.25ns reciprocal is frequency: The instruction cycle is the basic operation of the cpu which consist of three steps. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. If the design does less. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT CS334 Computer Architecture PowerPoint Presentation, free Explain Cycle Time In Computer Architecture 2ns to 0.25ns reciprocal is frequency: If the design does less work during a clock cycle, it’s cycle time will be shorter. The severity of the problem is determined by the difference in the timing of register file update (first instruction). Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be. Explain Cycle Time In Computer Architecture.

From exogyyabt.blob.core.windows.net

Instruction Cycle Diagram In Computer Architecture at Ann Nelson blog Explain Cycle Time In Computer Architecture If the design does less work during a clock cycle, it’s cycle time will be shorter. The severity of the problem is determined by the difference in the timing of register file update (first instruction). Cycle time is a function of the processor’s design. The bus cycle is the cycle or time required to make a single read or write. Explain Cycle Time In Computer Architecture.

From www.codingninjas.com

Memory Hierarchy Design and its Characteristics Coding Ninjas CodeStudio Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. 0.5 ghz to 4 ghz (1 htz. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. More on this later, when we discuss pipelining. 2ns to 0.25ns reciprocal is frequency: If the design does less. Explain Cycle Time In Computer Architecture.

From gallcolleenvirh.blogspot.com

Clock Cycle In Computer Architecture Concepts Of Pipelining Computer Explain Cycle Time In Computer Architecture The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The cpu repetitively performs fetch , decode , execute. Cycle time is a function of the processor’s design. If the design does less work during a clock cycle, it’s cycle time will be shorter. Cycle. Explain Cycle Time In Computer Architecture.

From stackoverflow.com

mips Clock cycle in pipelining and singleclock cycle implementation Explain Cycle Time In Computer Architecture If the design does less work during a clock cycle, it’s cycle time will be shorter. Cycle time is a function of the processor’s design. 0.5 ghz to 4 ghz (1 htz. The severity of the problem is determined by the difference in the timing of register file update (first instruction). 2ns to 0.25ns reciprocal is frequency: The cpu repetitively. Explain Cycle Time In Computer Architecture.

From www.presentationeze.com

Cycle Time Definition Analyse Cycle Time Analysis Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. If the design does less work during a clock cycle, it’s cycle time will be shorter. More on this later, when we discuss pipelining. 0.5 ghz to 4 ghz (1 htz. The severity of the problem is determined by the difference in the timing of register file update (first instruction). The. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT Computer Architecture PowerPoint Presentation, free download ID Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. More on this later, when we discuss pipelining. 0.5 ghz to 4 ghz (1 htz. The severity of the problem is determined by the difference in the timing of register file update (first instruction). If the design does less work during a clock cycle, it’s cycle time will be shorter. 2ns. Explain Cycle Time In Computer Architecture.

From byjus.com

Instruction Pipeline in Computer Architecture GATE Notes Explain Cycle Time In Computer Architecture Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. More on this later, when we discuss pipelining. Cycle time is a function of the processor’s design. 2ns to 0.25ns reciprocal is frequency: The instruction cycle is the basic operation of the cpu which consist of three. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT CS 5513 Computer Architecture Lecture 1 Introduction PowerPoint Explain Cycle Time In Computer Architecture More on this later, when we discuss pipelining. The severity of the problem is determined by the difference in the timing of register file update (first instruction). The cpu repetitively performs fetch , decode , execute. 0.5 ghz to 4 ghz (1 htz. Cycle time is a function of the processor’s design. 2ns to 0.25ns reciprocal is frequency: Cycle time. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT Computer Organization and Architecture PowerPoint Presentation Explain Cycle Time In Computer Architecture More on this later, when we discuss pipelining. The instruction cycle is the basic operation of the cpu which consist of three steps. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. Cycle time is a function of the processor’s design. Cycle time in. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT CS15346 Perspectives in Computer Architecture PowerPoint Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. The instruction cycle is the basic operation of the cpu which consist of three steps. If the design does less work during a clock cycle, it’s cycle time will be shorter. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed. Explain Cycle Time In Computer Architecture.

From www.youtube.com

Instruction cycle // phases of instruction cycle in computer Explain Cycle Time In Computer Architecture The severity of the problem is determined by the difference in the timing of register file update (first instruction). The instruction cycle is the basic operation of the cpu which consist of three steps. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. Cycle. Explain Cycle Time In Computer Architecture.

From www.keypup.io

Calculating Cycle Time Templates and Tutorials Keypup Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. More on this later, when we discuss pipelining. The instruction cycle is the basic operation of the cpu which consist of three steps. 0.5 ghz to 4 ghz (1 htz. 2ns to 0.25ns reciprocal is frequency: The bus cycle is the cycle or time required to make a single read or. Explain Cycle Time In Computer Architecture.

From www.youtube.com

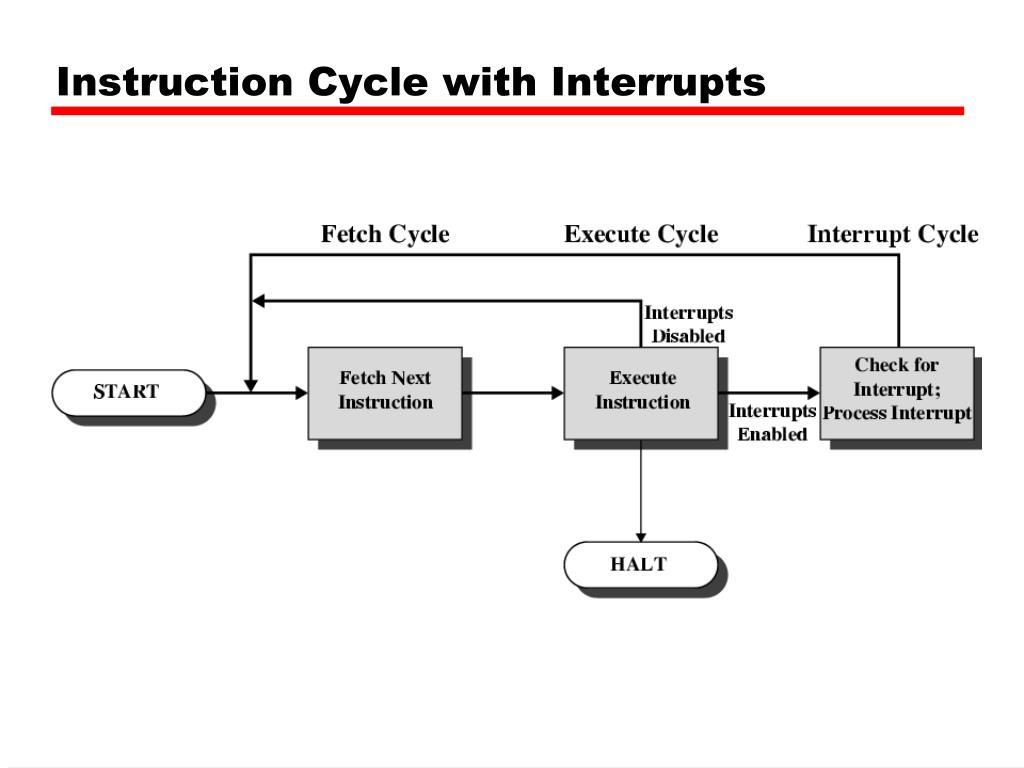

Interrupt cycle in computer architecture // flowchart for operations Explain Cycle Time In Computer Architecture Cycle time is a function of the processor’s design. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The cpu repetitively performs fetch , decode , execute. The severity of the problem is determined by the difference in the timing of register file update. Explain Cycle Time In Computer Architecture.

From joiklbpnh.blob.core.windows.net

Stack Definition Computer Architecture at Michael Leite blog Explain Cycle Time In Computer Architecture If the design does less work during a clock cycle, it’s cycle time will be shorter. More on this later, when we discuss pipelining. Cycle time is a function of the processor’s design. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. The cpu repetitively performs. Explain Cycle Time In Computer Architecture.

From joixlatlw.blob.core.windows.net

The Instruction Cycle In Computer Architecture at Douglas Brady blog Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. 0.5 ghz to 4 ghz (1 htz. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. The severity of the problem is determined by the difference in the timing of register file update (first instruction). The bus. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT Computer Performance Evaluation Cycles Per Instruction (CPI Explain Cycle Time In Computer Architecture The severity of the problem is determined by the difference in the timing of register file update (first instruction). If the design does less work during a clock cycle, it’s cycle time will be shorter. More on this later, when we discuss pipelining. The instruction cycle is the basic operation of the cpu which consist of three steps. 0.5 ghz. Explain Cycle Time In Computer Architecture.

From loebozrbc.blob.core.windows.net

Instruction Time Of A Computer at Delores Smith blog Explain Cycle Time In Computer Architecture Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. The severity of the problem is determined by the difference in the timing of register file update (first instruction). 0.5 ghz to 4 ghz (1 htz. If the design does less work during a clock cycle, it’s. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT Computer Performance Evaluation Cycles Per Instruction (CPI Explain Cycle Time In Computer Architecture More on this later, when we discuss pipelining. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. 0.5 ghz to 4 ghz (1 htz. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an. Explain Cycle Time In Computer Architecture.

From exoqegszq.blob.core.windows.net

Define Instruction Cycle In Computer Architecture at Jose Rhodes blog Explain Cycle Time In Computer Architecture The cpu repetitively performs fetch , decode , execute. 0.5 ghz to 4 ghz (1 htz. The severity of the problem is determined by the difference in the timing of register file update (first instruction). The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such.. Explain Cycle Time In Computer Architecture.

From exogyyabt.blob.core.windows.net

Instruction Cycle Diagram In Computer Architecture at Ann Nelson blog Explain Cycle Time In Computer Architecture The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. If the design does less work during a clock cycle, it’s cycle time will be shorter. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be. Explain Cycle Time In Computer Architecture.

From www.cgdirector.com

What is a CPU's IPC? Instructions per Cycle explained Explain Cycle Time In Computer Architecture Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed by a computer. 0.5 ghz to 4 ghz (1 htz. The instruction cycle is the basic operation of the cpu which consist of three steps. If the design does less work during a clock cycle, it’s cycle time will be. Explain Cycle Time In Computer Architecture.

From loebozrbc.blob.core.windows.net

Instruction Time Of A Computer at Delores Smith blog Explain Cycle Time In Computer Architecture 0.5 ghz to 4 ghz (1 htz. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The severity of the problem is determined by the difference in the timing of register file update (first instruction). If the design does less work during a clock. Explain Cycle Time In Computer Architecture.

From www.codingninjas.com

What is Instruction Cycle in Computer Architecture? Coding Ninjas Explain Cycle Time In Computer Architecture The instruction cycle is the basic operation of the cpu which consist of three steps. The cpu repetitively performs fetch , decode , execute. If the design does less work during a clock cycle, it’s cycle time will be shorter. Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be executed. Explain Cycle Time In Computer Architecture.

From www.me-company.de

Cycle Time Definition und Praxistipps für agile Teams Explain Cycle Time In Computer Architecture 0.5 ghz to 4 ghz (1 htz. The instruction cycle is the basic operation of the cpu which consist of three steps. Cycle time is a function of the processor’s design. The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. If the design does. Explain Cycle Time In Computer Architecture.

From www.programmathically.com

How does a CPU Execute Instructions Understanding Instruction Cycles Explain Cycle Time In Computer Architecture The severity of the problem is determined by the difference in the timing of register file update (first instruction). Cycle time is a function of the processor’s design. If the design does less work during a clock cycle, it’s cycle time will be shorter. 0.5 ghz to 4 ghz (1 htz. The instruction cycle is the basic operation of the. Explain Cycle Time In Computer Architecture.

From circuitbirnirwy.z21.web.core.windows.net

Explain Computer Architecture With Diagram Explain Cycle Time In Computer Architecture 2ns to 0.25ns reciprocal is frequency: Cycle time is a function of the processor’s design. 0.5 ghz to 4 ghz (1 htz. The severity of the problem is determined by the difference in the timing of register file update (first instruction). Cycle time in computer architecture refers to the time it takes for a complete cycle of operations to be. Explain Cycle Time In Computer Architecture.

From www.javatpoint.com

Instruction Pipeline javatpoint Explain Cycle Time In Computer Architecture The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. The cpu repetitively performs fetch , decode , execute. 2ns to 0.25ns reciprocal is frequency: If the design does less work during a clock cycle, it’s cycle time will be shorter. The instruction cycle is. Explain Cycle Time In Computer Architecture.

From www.slideserve.com

PPT PART 2 Foundation to Computer Architecture CHAPTER 3 A TOP Explain Cycle Time In Computer Architecture The bus cycle is the cycle or time required to make a single read or write transaction between the cpu and an external device such. 0.5 ghz to 4 ghz (1 htz. The cpu repetitively performs fetch , decode , execute. More on this later, when we discuss pipelining. Cycle time in computer architecture refers to the time it takes. Explain Cycle Time In Computer Architecture.