From slideplayer.com

Chapter 10 Timing Issues Rev /11/2003 Rev /28/ ppt download Clock To Q Delay Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. For any technology node, there will be several. clock domain defined by seq. Clock To Q Delay.

From www.youtube.com

Setup Time and Hold Time of Flip Flop Explained Digital Electronics Clock To Q Delay For any technology node, there will be several. Q does not necessarily settle at time d. clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.chegg.com

Solved QUESTION 1 For the following FF, the clocktoQ delay Clock To Q Delay For any technology node, there will be several. Q does not necessarily settle at time d. clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.numerade.com

SOLVED Assume the circuit shown below has the following timing Clock To Q Delay clock domain defined by seq. For any technology node, there will be several. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.chegg.com

Solved QUESTION 1 For the following FF, the clocktoQ delay Clock To Q Delay clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. For any technology node, there will be several. Q does not necessarily settle at time d. Clock To Q Delay.

From www.vlsiguru.com

CLOCK TO Q DELAY(pavan) VLSI Guru Clock To Q Delay Q does not necessarily settle at time d. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Clock To Q Delay.

From www.vlsiguru.com

CLOCK TO Q DELAY(pavan) VLSI Guru Clock To Q Delay clock domain defined by seq. Q does not necessarily settle at time d. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.researchgate.net

ClocktoQ delay, and setup and hold times of the original and proposed Clock To Q Delay clock domain defined by seq. For any technology node, there will be several. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.researchgate.net

CLKtoQ delay as a function of dataclock timing skew... Download Clock To Q Delay Q does not necessarily settle at time d. For any technology node, there will be several. clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.researchgate.net

Dependence of clocktoQ delay and setup time of a register on Clock To Q Delay For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Q does not necessarily settle at time d. Clock To Q Delay.

From www.vlsiguru.com

CLOCK TO Q DELAY(pavan) VLSI Guru Clock To Q Delay For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Q does not necessarily settle at time d. Clock To Q Delay.

From www.chegg.com

Solved QUESTION 1 For the following FF, the clocktoQ delay Clock To Q Delay Q does not necessarily settle at time d. clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. For any technology node, there will be several. Clock To Q Delay.

From www.chegg.com

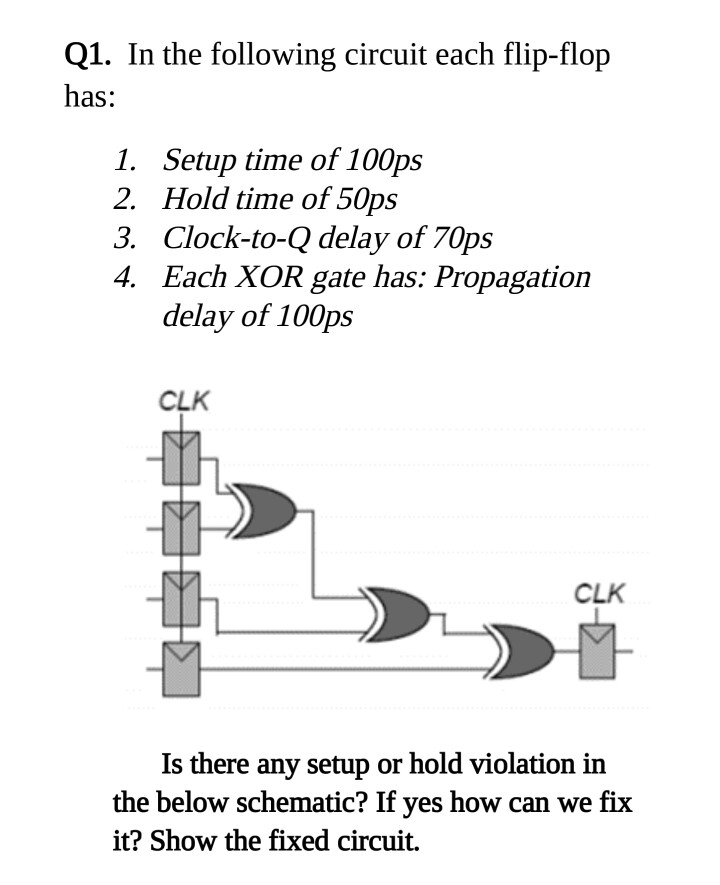

Solved Q1. In the following circuit each flipflop has 1. Clock To Q Delay clock domain defined by seq. For any technology node, there will be several. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.chegg.com

Solved The registers have hold time 0 ns, clocktoQ delay Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Q does not necessarily settle at time d. For any technology node, there will be several. clock domain defined by seq. Clock To Q Delay.

From www.chegg.com

Solved In the circuit below, the delay from clock to Q is 2 Clock To Q Delay For any technology node, there will be several. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Clock To Q Delay.

From www.chegg.com

Consider the following circuit. The clocktoq delay, Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. For any technology node, there will be several. Q does not necessarily settle at time d. Clock To Q Delay.

From www.slideserve.com

PPT Latch versus Register PowerPoint Presentation, free download ID Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Q does not necessarily settle at time d. For any technology node, there will be several. clock domain defined by seq. Clock To Q Delay.

From www.numerade.com

SOLVED If each flip flop has a clocktoQ delay of 1 ns, how much time Clock To Q Delay Q does not necessarily settle at time d. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Clock To Q Delay.

From www.pldworld.info

Clock to Q Propagation Delay Clock To Q Delay clock domain defined by seq. For any technology node, there will be several. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.chegg.com

Solved For the following circuit, the timing characteristics Clock To Q Delay For any technology node, there will be several. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Clock To Q Delay.

From www.vlsiguru.com

CLOCK TO Q DELAY(pavan) VLSI Guru Clock To Q Delay Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. For any technology node, there will be several. clock domain defined by seq. Clock To Q Delay.

From www.chegg.com

Solved Problem 1 Write down the approximate setup time, Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. For any technology node, there will be several. Q does not necessarily settle at time d. Clock To Q Delay.

From slidetodoc.com

Lecture 22 PLLs and DLLs Outline q Clock Clock To Q Delay clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Q does not necessarily settle at time d. For any technology node, there will be several. Clock To Q Delay.

From www.vlsiguru.com

CLOCK TO Q DELAY(pavan) VLSI Guru Clock To Q Delay Q does not necessarily settle at time d. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Clock To Q Delay.

From www.vlsiguru.com

CLOCK TO Q DELAY(pavan) VLSI Guru Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Q does not necessarily settle at time d. clock domain defined by seq. For any technology node, there will be several. Clock To Q Delay.

From www.researchgate.net

(a) ClocktoQ delay simulation of various F/Fs. (b) Powerdelay Clock To Q Delay For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Q does not necessarily settle at time d. Clock To Q Delay.

From www.semanticscholar.org

Figure 1 from Setup time, hold time and clocktoQ delay computation Clock To Q Delay Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. For any technology node, there will be several. clock domain defined by seq. Clock To Q Delay.

From www.chegg.com

Solved Timing Q1 Consider the circuit below. The gate Clock To Q Delay clock domain defined by seq. Q does not necessarily settle at time d. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. For any technology node, there will be several. Clock To Q Delay.

From www.numerade.com

SOLVED Q4. Delay and Timing Constraints For the following circuit Clock To Q Delay For any technology node, there will be several. Q does not necessarily settle at time d. clock domain defined by seq. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.youtube.com

Clock To Q delay Tcq YouTube Clock To Q Delay Q does not necessarily settle at time d. clock domain defined by seq. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.oreilly.com

4. Sequential Logic Learning FPGAs [Book] Clock To Q Delay Q does not necessarily settle at time d. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Clock To Q Delay.

From www.chegg.com

Solved For the following FF, the clock toQ delay is 4 ns. Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Q does not necessarily settle at time d. For any technology node, there will be several. clock domain defined by seq. Clock To Q Delay.

From www.chegg.com

Solved In the following circuit, the XOR gate has a delay in Clock To Q Delay Q does not necessarily settle at time d. clock domain defined by seq. For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Clock To Q Delay.

From www.youtube.com

Electronics What does the "Q" in "ClocktoQ delay" stand for? YouTube Clock To Q Delay hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. clock domain defined by seq. Q does not necessarily settle at time d. For any technology node, there will be several. Clock To Q Delay.

From www.researchgate.net

ClocktoQ delay (Tc) of a DFF as a function of the relative arrival Clock To Q Delay For any technology node, there will be several. hence, input ‘qm’ (which is ‘d’ input from previous ‘low’ clk) is latched to output ‘q’ of negative latch, through ‘tr4’ and ‘inv6’ ‘inv2, inv3’ holds the ‘qm’ state of. Q does not necessarily settle at time d. clock domain defined by seq. Clock To Q Delay.