Arm System Level Cache . In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency.

from www.chegg.com

For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain.

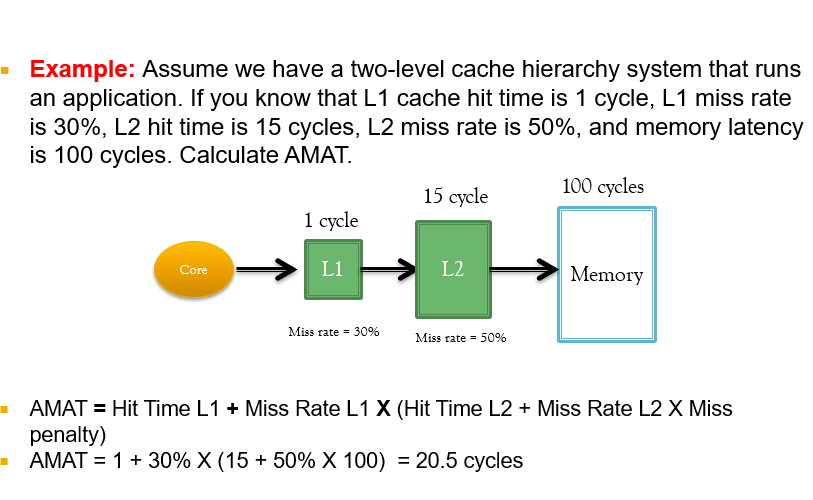

Example Assume we have a twolevel cache hierarchy

Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency.

From community.arm.com

Arm Interconnect for New Total Compute Solutions Architectures and Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From developer.apple.com

What is System Level Cache?Where i… Apple Developer Forums Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the. Arm System Level Cache.

From community.arm.com

CoSimulation Accelerates SoC Verification SoC Design and Simulation Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From blog.bytebytego.com

A Crash Course in Caching Part 1 by Alex Xu Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the. Arm System Level Cache.

From www.anandtech.com

A new CI700 Coherent Interconnect & NI700 NoC For SoCs Arm Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From www.youtube.com

System Design Multi Level Cache Part 2 Solution, Code and Design Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From aijishu.com

arm处理器cache结构的进化,及PoC, PoU的使用 极术社区 连接开发者与智能计算生态 Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From eureka.patsnap.com

Systemlevel cache Eureka Patsnap Arm System Level Cache In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From www.eeworldonline.com

The complexities and advantages of cache and memory hierarchy Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. These aspects of the system level architecture can affect the. Arm System Level Cache.

From www.asset-intertech.com

SourcePoint Arm Trace ASSET InterTech Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From programmer.ink

Chapter 4. Mybatis Caching Mechanism Arm System Level Cache In this post, we explain. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From klazcgckl.blob.core.windows.net

Cache And Main Memory Difference at Waller blog Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From bbs.elecfans.com

ARM应用处理器的Cache level进化历史阐述 ARM技术论坛 电子技术论坛 广受欢迎的专业电子论坛! Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From www.anandtech.com

The CMN700 Mesh Network Bigger, More Flexible Arm Announces Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. These aspects of the system level architecture can affect the. Arm System Level Cache.

From www.anandtech.com

A new CI700 Coherent Interconnect & NI700 NoC For SoCs Arm Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of. Arm System Level Cache.

From progressivecoder.com

Distributed Caching The One Introduction You Definitely Need Arm System Level Cache In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From www.pinterest.com

ARM SystemonChip architecture Arms, Instruction, Timer Arm System Level Cache In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From www.linkedin.com

"Maximizing Performance and Efficiency A Comprehensive Guide to Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to. Arm System Level Cache.

From www.anandtech.com

The CMN700 Mesh Network Bigger, More Flexible Arm Announces Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From www.arteris.com

SemiWiki That Last Level Cache is Pretty Important Arteris Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From webinars.sw.siemens.com

Arm System level RTL power estimation using PowerPro Siemens Software Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From blog.csdn.net

深度学习arm cache系列一篇就够了_刷cache机制CSDN博客 Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From www.anandtech.com

Deciphering the New Cache Hierarchy L1, 512 KB L2, 8 or 16 MB L3 AMD Arm System Level Cache In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From aijishu.com

arm处理器cache结构的进化,及PoC, PoU的使用 极术社区 连接开发者与智能计算生态 Arm System Level Cache • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From www.chegg.com

Example Assume we have a twolevel cache hierarchy Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From poohyhoh.blogspot.com

Pooh Blog ARM SDG Ch12. Caches 02 12.1 The Memory Hierarchy and Arm System Level Cache In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From eureka.patsnap.com

Systemlevel cache Eureka Patsnap Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From semiengineering.com

A Primer On LastLevel Cache Memory For SoC Designs Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. In this post, we explain. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From blog.feabhas.com

Introduction to the ARM® Cortex®M7 Cache Part 2 Cache Replacement Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu. Arm System Level Cache.

From www.nextplatform.com

ARM Goes To War In The Datacenter With “Ares” Designs Arm System Level Cache In this post, we explain. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the. Arm System Level Cache.

From www.anandtech.com

Sponsored Post Keep Your App’s Memory Safe with Arm Memory Tagging Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of. Arm System Level Cache.

From community.arm.com

System Guidance for Infrastructure (SGI) Wiki Open Source Software Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. For example, a system design might introduce additional levels of caching that cannot be managed using the cp15. Arm System Level Cache.

From www.mdpi.com

Cryptography Free FullText A Memory Hierarchy Protected against Arm System Level Cache In this post, we explain. These aspects of the system level architecture can affect the requirements for software management of caches and coherency. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.

From chsgcxy.github.io

DDR and DRAMSim3 Messy Notes Arm System Level Cache For example, a system design might introduce additional levels of caching that cannot be managed using the cp15 maintenance operations defined. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. These aspects of the system level architecture can affect the requirements for software management of. Arm System Level Cache.

From download.mikroe.com

ARM CortexM3 and CortexM4 Memory Organization Arm System Level Cache These aspects of the system level architecture can affect the requirements for software management of caches and coherency. In this post, we explain. • shared cache contention channel demonstrated up to 89% accurate open world attack • novel gpu contention channel performed up to 2% better than. For example, a system design might introduce additional levels of caching that cannot. Arm System Level Cache.