What Is Port In Vhdl . Understanding ports and their modes is crucial. Ports are a part of the block interface: Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Each element listed in a. Vhdl port map is the process of mapping the input/ output ports of component in main module. The component declaration defines the names, order, mode and types of the. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Port map ( [ port_name => ] expression,. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. A port map is used to define the interconnection between instances.

from stackoverflow.com

The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Ports are a part of the block interface: A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. The component declaration defines the names, order, mode and types of the. Port map ( [ port_name => ] expression,. Each element listed in a. Vhdl port map is the process of mapping the input/ output ports of component in main module. Understanding ports and their modes is crucial. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing.

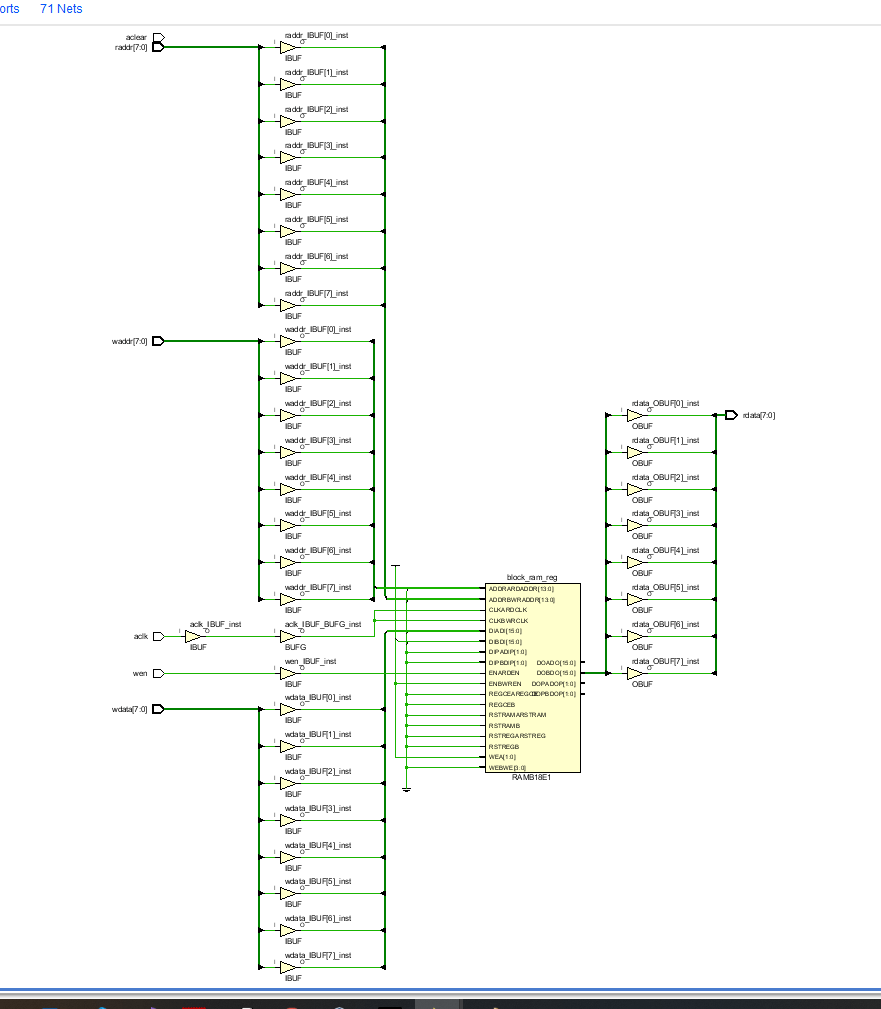

fpga VHDL Correctly way to infer a single port ram with synchronous

What Is Port In Vhdl Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Vhdl port map is the process of mapping the input/ output ports of component in main module. Each element listed in a. Understanding ports and their modes is crucial. Ports are a part of the block interface: Port map ( [ port_name => ] expression,. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. The component declaration defines the names, order, mode and types of the. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. A port map is used to define the interconnection between instances.

From pediaa.com

What is the Difference Between Signal and Variable in VHDL What Is Port In Vhdl Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. A port map is used to define the interconnection between instances. Ports are a part of the block interface: The component declaration defines the names, order, mode and types of the. Understanding ports and their modes is crucial. Each element listed in a.. What Is Port In Vhdl.

From electronics.stackexchange.com

VHDL Uninitialized inout port has no driver Electrical Engineering What Is Port In Vhdl A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Each element listed in a. Vhdl port map is the process of mapping the input/ output ports of component in main module. We use ports in a vhdl entity declaration to define. What Is Port In Vhdl.

From surf-vhdl.com

How to implement a Multi Port memory on FPGA SurfVHDL What Is Port In Vhdl A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Port map ( [ port_name => ] expression,. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. The component declaration defines. What Is Port In Vhdl.

From www.youtube.com

VHDL Component and Port Mapping YouTube What Is Port In Vhdl Ports are a part of the block interface: Understanding ports and their modes is crucial. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. The component declaration defines the names, order, mode. What Is Port In Vhdl.

From bjkj.tsg211.com

How to Design a Simple Boolean Logic based IC using VHDL on ModelSim? What Is Port In Vhdl Each element listed in a. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. A port map is used to define the interconnection between instances. Vhdl port map is the process of mapping the input/ output ports of component in main module. Understanding ports and their modes is crucial.. What Is Port In Vhdl.

From www.slideshare.net

Introduction to VHDL What Is Port In Vhdl Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Vhdl port map is the process of mapping the input/ output ports of component in main module. Ports are a part of the block interface: The component declaration defines the names, order, mode and types of the. Each element listed in a. Understanding. What Is Port In Vhdl.

From stackoverflow.com

fpga Object is used but not declared in VHDL Stack Overflow What Is Port In Vhdl The component declaration defines the names, order, mode and types of the. Understanding ports and their modes is crucial. Port map ( [ port_name => ] expression,. Ports are a part of the block interface: Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Vhdl port map is the process of mapping. What Is Port In Vhdl.

From www.coursehero.com

[Solved] vhdl code is for 4 bit adder subtractor Specify port names A What Is Port In Vhdl Port map ( [ port_name => ] expression,. Understanding ports and their modes is crucial. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. The component declaration defines the names, order, mode and types of the. Vhdl port map is the process of mapping the input/ output ports of. What Is Port In Vhdl.

From stackoverflow.com

initialization Precedence of initialized port/signal assigned to port What Is Port In Vhdl Understanding ports and their modes is crucial. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Vhdl port map is the process of mapping the input/ output ports of component in main module. Ports are a part of the block interface: We use ports in a vhdl entity declaration. What Is Port In Vhdl.

From electronics.stackexchange.com

digital logic VHDL port declaration design for a feedback signal What Is Port In Vhdl Vhdl port map is the process of mapping the input/ output ports of component in main module. Understanding ports and their modes is crucial. Ports are a part of the block interface: Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. A port map is used to define the interconnection between instances.. What Is Port In Vhdl.

From www.youtube.com

VHDL BASIC Tutorial GENERIC YouTube What Is Port In Vhdl Each element listed in a. Ports are a part of the block interface: We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Vhdl port map is the process of mapping the input/ output ports of component in main module. Port map ( [ port_name => ] expression,. The component. What Is Port In Vhdl.

From stackoverflow.com

vhdl Undefined type in block design when using custom IP Stack Overflow What Is Port In Vhdl The component declaration defines the names, order, mode and types of the. Each element listed in a. A port map is used to define the interconnection between instances. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. The port map specifies the connection of the ports of each component. What Is Port In Vhdl.

From stackoverflow.com

fpga VHDL Correctly way to infer a single port ram with synchronous What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. The component declaration defines the names, order, mode and types of the. A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner.. What Is Port In Vhdl.

From electronics.stackexchange.com

Question about VHDL instantiation Electrical Engineering Stack Exchange What Is Port In Vhdl A port map is used to define the interconnection between instances. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Each element listed in a. Port map ( [ port_name => ] expression,. Ports act as the entry and exit points for signals, enabling data transfer in a structured. What Is Port In Vhdl.

From www.slideserve.com

PPT VHDL And Synthesis Review PowerPoint Presentation, free download What Is Port In Vhdl Each element listed in a. The component declaration defines the names, order, mode and types of the. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Vhdl port map is the process of mapping the input/ output ports of component in main module. We use ports in a vhdl. What Is Port In Vhdl.

From jjmk.dk

1.2 First VHDL design What Is Port In Vhdl A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. The component declaration defines the names, order, mode and types of the. Ports are a part of the block interface: Understanding ports and their modes is crucial. We use ports in a. What Is Port In Vhdl.

From slideplayer.com

VHDL 1. ver.7a VHDL1 INTRODUCTION TO VHDL (VERYHIGHSPEEDINTEGRATED What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Ports are a part of the block interface: A port map is used to define the interconnection between instances. The component declaration defines the names, order, mode and types of the. Understanding ports and their modes is crucial. Each element. What Is Port In Vhdl.

From www.slideserve.com

PPT VHDL Introduction PowerPoint Presentation, free download ID5569060 What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Ports are a part of the block interface: Port map ( [ port_name => ] expression,. Each element listed in a. The component declaration defines the names, order, mode and types of the. The port map specifies the connection of. What Is Port In Vhdl.

From www.numerade.com

SOLVED What is Explicit port mapping in VHDL ,Could you give me an What Is Port In Vhdl The component declaration defines the names, order, mode and types of the. Vhdl port map is the process of mapping the input/ output ports of component in main module. Each element listed in a. A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a. What Is Port In Vhdl.

From surf-vhdl.com

How to implement a digital MUX in VHDL SurfVHDL What Is Port In Vhdl The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Port map ( [ port_name => ] expression,. Understanding ports and their modes is crucial. The component declaration defines the names, order, mode and types of the. Vhdl port map is the process of mapping the input/ output ports of. What Is Port In Vhdl.

From www.chegg.com

3.2.1 Procedure 1. Write the VHDL code to describe a What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Ports are a part of the block interface: The component declaration defines the names, order, mode and types of the. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. The port map. What Is Port In Vhdl.

From stackoverflow.com

fpga Linking (two) bidirectional ports between (two) modules in VHDL What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Each element listed in a. The component declaration defines the names, order, mode and types of the. Ports are a. What Is Port In Vhdl.

From www.chegg.com

Solved Figure Q3a shows the circuit diagram of a full adder What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Port map ( [ port_name => ] expression,. Each element listed in a. A port map is used to define the interconnection between instances. Vhdl port map is the process of mapping the input/ output ports of component in main. What Is Port In Vhdl.

From itecnotes.com

Electronic VHDL port declaration design for a feedback signal What Is Port In Vhdl A port map is used to define the interconnection between instances. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Understanding ports and their modes is crucial. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Ports are a part of. What Is Port In Vhdl.

From www.youtube.com

How to use Port Map instantiation in VHDL YouTube What Is Port In Vhdl Vhdl port map is the process of mapping the input/ output ports of component in main module. Port map ( [ port_name => ] expression,. A port map is used to define the interconnection between instances. Ports are a part of the block interface: The port map specifies the connection of the ports of each component instance to signals within. What Is Port In Vhdl.

From www.youtube.com

Bidirectional ports inout port in VHDL and Verilog HDL YouTube What Is Port In Vhdl The component declaration defines the names, order, mode and types of the. Port map ( [ port_name => ] expression,. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Understanding ports and their modes is crucial. We use ports in a vhdl entity declaration to define the inputs and output of the. What Is Port In Vhdl.

From www.youtube.com

Designing Multiplexer and Demultiplexer ICs using VHDL YouTube What Is Port In Vhdl Each element listed in a. A port map is used to define the interconnection between instances. Port map ( [ port_name => ] expression,. Vhdl port map is the process of mapping the input/ output ports of component in main module. Understanding ports and their modes is crucial. Ports are a part of the block interface: We use ports in. What Is Port In Vhdl.

From stackoverflow.com

Passing generic to generic package to set port in VHDL Stack Overflow What Is Port In Vhdl Each element listed in a. A port map is used to define the interconnection between instances. Port map ( [ port_name => ] expression,. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Ports act as the entry and exit points for signals, enabling data transfer in a structured. What Is Port In Vhdl.

From surf-vhdl.com

How to implement a Multi Port memory on FPGA SurfVHDL What Is Port In Vhdl Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Understanding ports and their modes is crucial. Vhdl port map is the process of mapping the input/ output ports of component in main. What Is Port In Vhdl.

From mungfali.com

VHDL Port Map What Is Port In Vhdl A port map is used to define the interconnection between instances. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Understanding ports and their modes is crucial. Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. The component declaration defines the. What Is Port In Vhdl.

From surf-vhdl.com

How to implement a Multi Port memory on FPGA SurfVHDL What Is Port In Vhdl A port map is used to define the interconnection between instances. Ports are a part of the block interface: Vhdl port map is the process of mapping the input/ output ports of component in main module. We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Port map ( [. What Is Port In Vhdl.

From pediaa.com

What is the Difference Between Verilog and VHDL What Is Port In Vhdl Ports act as the entry and exit points for signals, enabling data transfer in a structured manner. Understanding ports and their modes is crucial. The component declaration defines the names, order, mode and types of the. Vhdl port map is the process of mapping the input/ output ports of component in main module. Ports are a part of the block. What Is Port In Vhdl.

From mungfali.com

VHDL Port Map What Is Port In Vhdl Port map ( [ port_name => ] expression,. Understanding ports and their modes is crucial. Vhdl port map is the process of mapping the input/ output ports of component in main module. The port map specifies the connection of the ports of each component instance to signals within the enclosing architecture body. Ports act as the entry and exit points. What Is Port In Vhdl.

From stackoverflow.com

vhdl port Pin constraint for Zedboard (phy0_dv pin What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Vhdl port map is the process of mapping the input/ output ports of component in main module. Port map ( [ port_name => ] expression,. Ports are a part of the block interface: The component declaration defines the names, order,. What Is Port In Vhdl.

From www.numerade.com

SOLVED Text Computer Architecture (VHDL CODE) Lab 4 4Bit Full What Is Port In Vhdl We use ports in a vhdl entity declaration to define the inputs and output of the component we are designing. Understanding ports and their modes is crucial. A port map is used to define the interconnection between instances. Each element listed in a. Vhdl port map is the process of mapping the input/ output ports of component in main module.. What Is Port In Vhdl.