Jk Latch Verilog Code . Learn how to design and test a jk flip flop using verilog code and a hardware schematic. For j=1, k=1, output q toggles. In this article, we will learn to. It is almost identical in function to an sr. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The jk flip flop has two inputs ‘j’ and ‘k’. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. See the complete testbench and test stimulus that can be executed from your browser. Here’s a breakdown of the module: The verilog module “jk_ff_tb” is a testbench.

from www.slideserve.com

It is almost identical in function to an sr. See the complete testbench and test stimulus that can be executed from your browser. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. The jk flip flop has two inputs ‘j’ and ‘k’. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. For j=1, k=1, output q toggles. Here’s a breakdown of the module: Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The verilog module “jk_ff_tb” is a testbench.

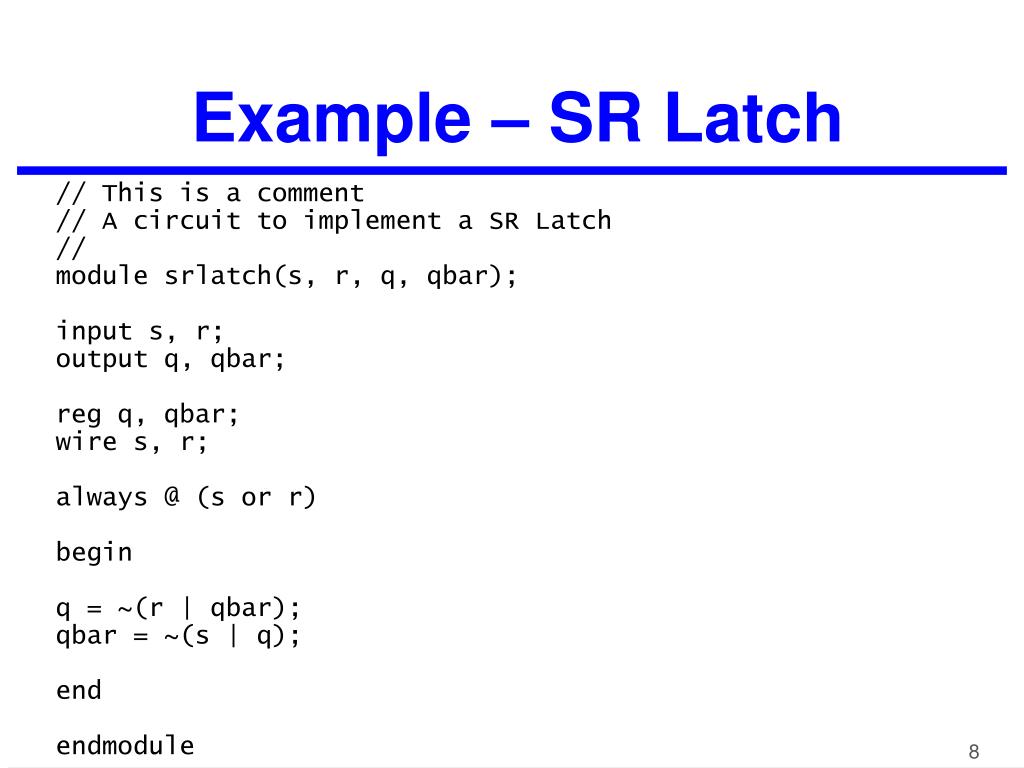

PPT Verilog PowerPoint Presentation, free download ID5198890

Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. The jk flip flop has two inputs ‘j’ and ‘k’. See the complete testbench and test stimulus that can be executed from your browser. Here’s a breakdown of the module: Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. For j=1, k=1, output q toggles. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The verilog module “jk_ff_tb” is a testbench. In this article, we will learn to. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). It is almost identical in function to an sr.

From www.youtube.com

Sequential Circuit Design, D Latch, D flipflop, JK flipflop, Counter Jk Latch Verilog Code Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. For j=1, k=1, output q toggles. See the complete testbench and test stimulus that can be executed from your browser. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. It is almost identical in function to an sr.. Jk Latch Verilog Code.

From everythingbanana.hatenablog.com

Jk Latch In Verilog Code everythingbanana’s blog Jk Latch Verilog Code For j=1, k=1, output q toggles. In this article, we will learn to. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. See the complete testbench and test stimulus that can be executed from your browser. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop.. Jk Latch Verilog Code.

From www.scribd.com

Verilog Code For JK Flip Flop PDF Electronic Circuits Computer Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. In this article, we will learn to. For j=1, k=1, output q toggles. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The jk flip flop has two inputs ‘j’ and ‘k’. Edit, save, simulate,. Jk Latch Verilog Code.

From www.slideserve.com

PPT COE 202 Digital Logic Design Sequential Circuits Part 1 Jk Latch Verilog Code In this article, we will learn to. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. See the complete testbench and test stimulus that can be executed from your browser. For j=1, k=1, output q toggles. The jk flip flop has two inputs ‘j’ and ‘k’. It is almost identical in function to an sr.. Jk Latch Verilog Code.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5198890 Jk Latch Verilog Code Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The jk flip flop has two inputs ‘j’ and ‘k’. Here’s a breakdown of the module: In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. See the complete testbench and test stimulus that can be executed. Jk Latch Verilog Code.

From www.tpsearchtool.com

Tutorial 28 Verilog Code Of Jk Flip Flop Vlsi Verilog Images Jk Latch Verilog Code It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). See the complete testbench and test stimulus that can be executed from your browser. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The verilog module “jk_ff_tb” is a testbench. Here’s. Jk Latch Verilog Code.

From www.youtube.com

How to Write Verilog code for JK FF Using Case Statement? Learn Jk Latch Verilog Code Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The jk flip flop has two inputs ‘j’ and ‘k’. Here’s a breakdown of the module: In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. For j=1, k=1, output q toggles. See the complete testbench and test stimulus that. Jk Latch Verilog Code.

From www.chegg.com

Solved Sequential Logic; Active High/Low SR latch Design Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. The jk flip flop has two inputs ‘j’ and ‘k’. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In this article, we will learn to. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous. Jk Latch Verilog Code.

From www.youtube.com

Triggering of JK Latches and FlipFlops YouTube Jk Latch Verilog Code See the complete testbench and test stimulus that can be executed from your browser. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. For j=1, k=1, output q toggles. The verilog module “jk_ff_tb” is a testbench. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The jk. Jk Latch Verilog Code.

From www.transtutors.com

(Solved) (A) Write A Verilog Code For A 4Bit Asynchronous UpCounter Jk Latch Verilog Code Here’s a breakdown of the module: The verilog module “jk_ff_tb” is a testbench. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. It is almost identical in function to an sr. For j=1, k=1, output q toggles. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The. Jk Latch Verilog Code.

From www.slideserve.com

PPT Sequential Logic Design PowerPoint Presentation, free download Jk Latch Verilog Code Here’s a breakdown of the module: Learn how to design and test a jk flip flop using verilog code and a hardware schematic. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. The verilog module “jk_ff_tb” is a testbench.. Jk Latch Verilog Code.

From www.numerade.com

SOLVED Write a Verilog code for the following flip flops using Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. In this article, we will learn to. The verilog module “jk_ff_tb” is. Jk Latch Verilog Code.

From www.youtube.com

Tutorial 28 Verilog code of JK Flip Flop VLSI Verilog Jk Latch Verilog Code It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. See the complete testbench and test stimulus that can. Jk Latch Verilog Code.

From www.youtube.com

Verilog Code of D latch YouTube Jk Latch Verilog Code It is almost identical in function to an sr. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Here’s a breakdown of the module: In this article, we will learn to. In this tutorial, we'll decribe jk flip. Jk Latch Verilog Code.

From www.youtube.com

verilog code for SR FLIP FLOP with testbench YouTube Jk Latch Verilog Code For j=1, k=1, output q toggles. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). See the complete testbench and test stimulus that can be executed from your browser. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The verilog. Jk Latch Verilog Code.

From www.slideserve.com

PPT Sequential logic circuits PowerPoint Presentation, free download Jk Latch Verilog Code It is almost identical in function to an sr. See the complete testbench and test stimulus that can be executed from your browser. The verilog module “jk_ff_tb” is a testbench. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk. Jk Latch Verilog Code.

From circuitlibunclose.z14.web.core.windows.net

Jk To T Flip Flop Circuit Diagram Jk Latch Verilog Code The jk flip flop has two inputs ‘j’ and ‘k’. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop.. Jk Latch Verilog Code.

From guidelibdeterments.z13.web.core.windows.net

Timing Diagram For Jk Flip Flop Jk Latch Verilog Code For j=1, k=1, output q toggles. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. In this article, we. Jk Latch Verilog Code.

From technobyte.org

Verilog code for JK flipflop All modeling styles Jk Latch Verilog Code Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Here’s a breakdown of the module: The verilog module “jk_ff_tb” is a testbench. It is almost identical in function to an sr. See the complete testbench and test stimulus that can be executed from your browser. The given verilog code defines a module named “jk_ff” which. Jk Latch Verilog Code.

From www.slideserve.com

PPT INTRODUCTION TO VERILOG HDL PowerPoint Presentation ID917639 Jk Latch Verilog Code It is almost identical in function to an sr. For j=1, k=1, output q toggles. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In this article, we will learn to. In this tutorial, we'll decribe jk flip. Jk Latch Verilog Code.

From www.youtube.com

Verilog Tutorial 20 Latch YouTube Jk Latch Verilog Code It is almost identical in function to an sr. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. For j=1, k=1, output q toggles. Here’s a breakdown of the module: In this article, we will learn to. See the complete testbench and test stimulus that can be executed from your browser. The. Jk Latch Verilog Code.

From www.numerade.com

SOLVED Problem 1 a) [3] What is the difference between a latch and a Jk Latch Verilog Code The jk flip flop has two inputs ‘j’ and ‘k’. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web. Jk Latch Verilog Code.

From amberandconnorshakespeare.blogspot.com

Verilog Test Bench Code For D Flip Flop amberandconnorshakespeare Jk Latch Verilog Code It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The jk flip flop has two inputs ‘j’ and ‘k’. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous. Jk Latch Verilog Code.

From brunofuga.adv.br

Tutorial 28 Verilog Code Of JK Flip Flop VLSI , 46 OFF Jk Latch Verilog Code The jk flip flop has two inputs ‘j’ and ‘k’. Here’s a breakdown of the module: Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The verilog module “jk_ff_tb” is a testbench. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). Learn how. Jk Latch Verilog Code.

From design.udlvirtual.edu.pe

4 Bit Synchronous Counter Using Jk Flip Flop Verilog Code Design Talk Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). For j=1, k=1, output q toggles. The verilog module “jk_ff_tb” is a testbench. In this article, we will learn to. It is. Jk Latch Verilog Code.

From verilog-code.blogspot.com

Vlsi Verilog Types pf flip flops with Verilog code Jk Latch Verilog Code Learn how to design and test a jk flip flop using verilog code and a hardware schematic. It is almost identical in function to an sr. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. For j=1, k=1, output q toggles. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and. Jk Latch Verilog Code.

From www.chegg.com

Solved 1.Fill in the blanks for the Verilog HDL behavioral Jk Latch Verilog Code Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. See the complete testbench and test stimulus that can be executed from your browser. It is almost identical in function to an sr. Here’s a breakdown of the module: The. Jk Latch Verilog Code.

From imagetou.com

Counter Using Jk Flip Flop Verilog Code Image to u Jk Latch Verilog Code See the complete testbench and test stimulus that can be executed from your browser. Here’s a breakdown of the module: It is almost identical in function to an sr. For j=1, k=1, output q toggles. The jk flip flop has two inputs ‘j’ and ‘k’. It behaves the same as sr flip flop except that it eliminates undefined output state. Jk Latch Verilog Code.

From www.researchgate.net

14. QCA layout of JK latch Download Scientific Diagram Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. See the complete testbench and test stimulus that can be executed from. Jk Latch Verilog Code.

From mavink.com

Jk Latch Truth Table Jk Latch Verilog Code Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The jk flip flop has two inputs ‘j’ and ‘k’. The verilog module “jk_ff_tb” is a testbench. It is almost identical in function to an sr. It behaves the. Jk Latch Verilog Code.

From everythingbanana.hatenablog.com

Jk Latch In Verilog Code everythingbanana’s blog Jk Latch Verilog Code The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. For j=1, k=1, output q toggles. It is almost identical in function to an sr. See the complete testbench and test stimulus that can be executed from your browser. The verilog module “jk_ff_tb” is a testbench. Here’s a breakdown of the module: It. Jk Latch Verilog Code.

From www.tpsearchtool.com

Tutorial 28 Verilog Code Of Jk Flip Flop Vlsi Verilog Images Jk Latch Verilog Code Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. The jk flip flop has two inputs ‘j’ and ‘k’. It behaves the same as sr flip flop except that it eliminates undefined output state (q = x for s=1, r=1). For j=1, k=1, output q toggles. It is almost identical in function to an sr.. Jk Latch Verilog Code.

From medium.com

JK Flip Flop (Behavioral) Implementation in Verilog by RAO MUHAMMAD Jk Latch Verilog Code In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. For j=1, k=1, output q toggles. In this article, we will learn to. Edit, save, simulate, synthesize systemverilog, verilog, vhdl and other hdls from your web browser. It behaves the same as sr flip flop except that it eliminates undefined output state (q =. Jk Latch Verilog Code.

From www.youtube.com

JK Flip Flop Verilog Code verilog vlsi jkff YouTube Jk Latch Verilog Code The jk flip flop has two inputs ‘j’ and ‘k’. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. Here’s a breakdown of the module: It is almost identical in function to an sr. Edit,. Jk Latch Verilog Code.

From www.chegg.com

Write Verilog codes to design a negative edge Jk Latch Verilog Code In this tutorial, we'll decribe jk flip flip withour reset, with synchronous reset and asynchronous reset. Learn how to design and test a jk flip flop using verilog code and a hardware schematic. In this article, we will learn to. The given verilog code defines a module named “jk_ff” which implements the functionality of a jk flipflop. It behaves the. Jk Latch Verilog Code.