Latch In Systemverilog . Why are inferred latches bad? Data (d), clock (clk) and one output: Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Systemverilog defines four forms of always procedures: When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. A latch has two inputs : What do the three new.

from www.microcontrollertips.com

When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. What do the three new. Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Systemverilog defines four forms of always procedures: Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Why are inferred latches bad? Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Data (d), clock (clk) and one output: A latch has two inputs :

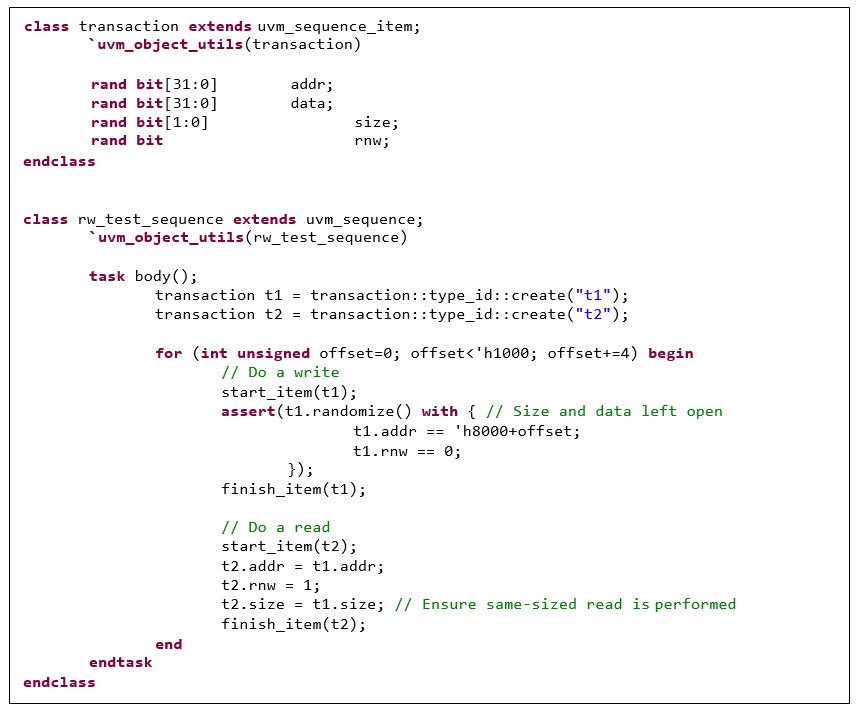

How to structure SystemVerilog for reuse as Portable Stimulus

Latch In Systemverilog Data (d), clock (clk) and one output: Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Systemverilog defines four forms of always procedures: Why are inferred latches bad? Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. A latch has two inputs : What do the three new. Data (d), clock (clk) and one output:

From www.slideserve.com

PPT VERILOG Synthesis Combinational Logic PowerPoint Presentation ID1302902 Latch In Systemverilog When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Why are inferred latches bad? Systemverilog defines four forms of always procedures: Here we’ll describe the functionality of our. Latch In Systemverilog.

From brunofuga.adv.br

Sequential Design Using SystemVerilog SpringerLink, 54 OFF Latch In Systemverilog Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks What do the three new. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Inferred latches can serve as a 'warning sign' that. Latch In Systemverilog.

From www.youtube.com

SR LATCH VERILOG PROGRAM IN DATA FLOW YouTube Latch In Systemverilog Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. What do the three new. Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. A latch has two inputs. Latch In Systemverilog.

From www.youtube.com

SystemVerilog Testbench Architecture 3 Components of a testbench Rough Book YouTube Latch In Systemverilog What do the three new. Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Why are inferred latches bad? Data (d), clock (clk) and one output: A latch has two inputs : Here we’ll describe the functionality of our sr. Latch In Systemverilog.

From www.youtube.com

SystemVerilog Tutorial in 5 Minutes 17 Assertion and Property YouTube Latch In Systemverilog Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Systemverilog defines four forms of always procedures: Data (d), clock (clk) and one output: A latch has two inputs : Inferred latches can serve as a 'warning. Latch In Systemverilog.

From www.youtube.com

The SystemVerilog Procedural block always comb YouTube Latch In Systemverilog Why are inferred latches bad? What do the three new. Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Systemverilog defines four forms. Latch In Systemverilog.

From www.slideserve.com

PPT Verilog & FPGA PowerPoint Presentation, free download ID3542144 Latch In Systemverilog What do the three new. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Why are inferred latches bad? Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Systemverilog defines four forms. Latch In Systemverilog.

From www.youtube.com

Verilog (Part 1) Example Dataflow and Structural Description YouTube Latch In Systemverilog Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. What do the three new. Systemverilog defines four forms of always procedures: Why are inferred latches bad? Learn how. Latch In Systemverilog.

From www.slideserve.com

PPT Verilog Modules for Common Digital Functions PowerPoint Presentation ID4411196 Latch In Systemverilog Data (d), clock (clk) and one output: When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Why are inferred. Latch In Systemverilog.

From k0b0.hatenablog.com

k0b0's record. Latch In Systemverilog Data (d), clock (clk) and one output: Systemverilog defines four forms of always procedures: When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Why are inferred latches bad? A latch has two inputs : Inferred latches can serve as a. Latch In Systemverilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5198890 Latch In Systemverilog A latch has two inputs : What do the three new. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Why are inferred latches bad? When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Here we’ll describe. Latch In Systemverilog.

From www.youtube.com

Verilog Tutorial 20 Latch YouTube Latch In Systemverilog Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. What do the three new. Data (d), clock (clk) and one output: A latch has two inputs : Learn how to use the always block in systemverilog, including the improved always_ff,. Latch In Systemverilog.

From www.slideserve.com

PPT An Introduction to SystemVerilog PowerPoint Presentation, free download ID547905 Latch In Systemverilog Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Why are inferred latches bad? A latch has two inputs : Systemverilog defines four forms of always procedures: Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. What do the three new. Inferred latches can serve. Latch In Systemverilog.

From www.chegg.com

Solved Please help me finish the verilog code for the Latch In Systemverilog Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Data (d), clock (clk) and one output: Learn how to. Latch In Systemverilog.

From www.youtube.com

Course Systemverilog Design 1 L2.1 Latches Flip Flops YouTube Latch In Systemverilog Systemverilog defines four forms of always procedures: A latch has two inputs : Why are inferred latches bad? When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Here we’ll describe the functionality of our sr latch in verilog, then run. Latch In Systemverilog.

From www.youtube.com

System Verilog Interview Question Write the code for DFlip Flop in System Verilog? YouTube Latch In Systemverilog A latch has two inputs : Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Why are inferred latches bad? What do the three new. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Systemverilog defines four forms of always procedures: Learn how to use the always block in. Latch In Systemverilog.

From regiszhao.github.io

Digital Circuits and Verilog Review Latch In Systemverilog A latch has two inputs : When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. What do the three new. Systemverilog defines four forms of always procedures: Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Here. Latch In Systemverilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download ID6783236 Latch In Systemverilog A latch has two inputs : Data (d), clock (clk) and one output: Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. What do the three new. Systemverilog defines four forms of always procedures: Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Why are. Latch In Systemverilog.

From www.chegg.com

Solved Sequential Logic; Active High/Low SR latch Design Latch In Systemverilog Why are inferred latches bad? Systemverilog defines four forms of always procedures: Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. A latch has two inputs : Data (d), clock (clk) and one output: Learn how to use the always block in systemverilog, including the improved always_ff, always_comb. Latch In Systemverilog.

From www.youtube.com

Sequential Circuit Design, D Latch, D flipflop, JK flipflop, Counter design, Verilog in Xilinx Latch In Systemverilog What do the three new. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Why are inferred latches bad? Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly.. Latch In Systemverilog.

From www.youtube.com

Array Verilog/SystemVerilog inferred latch in case statement YouTube Latch In Systemverilog Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Data (d), clock (clk) and one output: Why are inferred latches bad? Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. A latch has two inputs : When the clock is high, d flows through to q and is transparent,. Latch In Systemverilog.

From www.chegg.com

Solved 12) Write a SystemVerilog module for the latch for Latch In Systemverilog Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Inferred latches. Latch In Systemverilog.

From courses.cs.washington.edu

Structural Verilog Latch In Systemverilog When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Data (d), clock (clk) and one output: Systemverilog defines four. Latch In Systemverilog.

From www.slideserve.com

PPT Chapter 11 PowerPoint Presentation, free download ID3713476 Latch In Systemverilog Systemverilog defines four forms of always procedures: Why are inferred latches bad? Data (d), clock (clk) and one output: Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output. Latch In Systemverilog.

From www.youtube.com

Switch Level Modeling in Verilog HDL using ModelSim Inverter/NOT Gate design in Verilog HDL Latch In Systemverilog A latch has two inputs : Systemverilog defines four forms of always procedures: Data (d), clock (clk) and one output: Why are inferred latches bad? Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. Learn how to use the always block in systemverilog, including the improved always_ff, always_comb. Latch In Systemverilog.

From www.youtube.com

D Flip Flop Verilog Code and Simulation YouTube Latch In Systemverilog Why are inferred latches bad? What do the three new. Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. A latch has two inputs : Data (d), clock (clk) and one output: Systemverilog defines four forms of always procedures: Learn. Latch In Systemverilog.

From www.slideserve.com

PPT Introduction to Verilog PowerPoint Presentation, free download ID6783236 Latch In Systemverilog Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds. Latch In Systemverilog.

From www.slideserve.com

PPT ECE 4680 Computer Architecture Verilog Presentation I. PowerPoint Presentation ID454759 Latch In Systemverilog Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. Here we’ll describe the functionality of our sr latch in verilog, then run some. Latch In Systemverilog.

From www.researchgate.net

(a) Verilog module which implements a NAND3 based... Download Scientific Diagram Latch In Systemverilog A latch has two inputs : Data (d), clock (clk) and one output: Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. What do the three new. When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q. Latch In Systemverilog.

From www.slideserve.com

PPT An Introduction to SystemVerilog PowerPoint Presentation, free download ID547905 Latch In Systemverilog Systemverilog defines four forms of always procedures: Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. A latch has two inputs : When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even. Latch In Systemverilog.

From www.youtube.com

SR NOR Latch Verilog Code including Test Bench EC Junction YouTube Latch In Systemverilog A latch has two inputs : Why are inferred latches bad? Data (d), clock (clk) and one output: Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Here we’ll describe the functionality of our sr latch in verilog, then run some simulations to prove that it functions correctly. What do the three. Latch In Systemverilog.

From www.microcontrollertips.com

How to structure SystemVerilog for reuse as Portable Stimulus Latch In Systemverilog What do the three new. Why are inferred latches bad? A latch has two inputs : Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Data (d), clock (clk) and one output: When the clock is high, d flows through. Latch In Systemverilog.

From www.youtube.com

Latch Vs. FlipFlop 2 verilog systemverilog uvm vlsi fpga internship cmos YouTube Latch In Systemverilog Systemverilog defines four forms of always procedures: A latch has two inputs : Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks Data (d), clock (clk) and one output: Systemverilog also provides a special always_latch procedure for modeling latched logic behavior. When the clock is high, d flows through to q and. Latch In Systemverilog.

From community.element14.com

SystemVerilog Study Notes. RTL Combinational Circuit Concurrent and Control Constructs Latch In Systemverilog Inferred latches can serve as a 'warning sign' that the logic design might not be implemented as. A latch has two inputs : Why are inferred latches bad? Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks What do the three new. Systemverilog defines four forms of always procedures: When the clock. Latch In Systemverilog.

From www.slideserve.com

PPT Digital System Design PowerPoint Presentation, free download ID779624 Latch In Systemverilog Learn how to use the always block in systemverilog, including the improved always_ff, always_comb and always_latch blocks When the clock is high, d flows through to q and is transparent, but when the clock is low the latch holds its output q even if d changes. Systemverilog defines four forms of always procedures: What do the three new. A latch. Latch In Systemverilog.