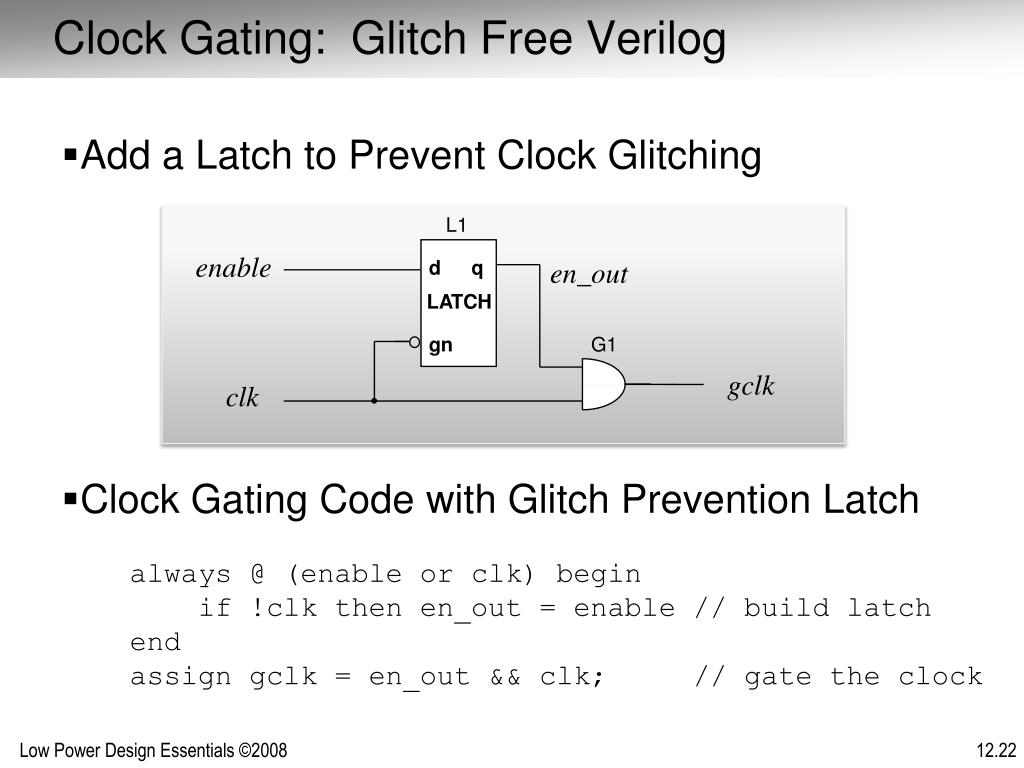

Clock Gating Verilog Code . Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Could you explain me what exactly is clock gating. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. As far as i know the clock signal is fed to the. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. So there are 3 cycles in this. The clock gating logic could be based on functional behavior of. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. As the name implies, clock gating should use a gate, an and gate. Clock gating in verilog hi.

from www.slideserve.com

Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Could you explain me what exactly is clock gating. As far as i know the clock signal is fed to the. Clock gating in verilog hi. As the name implies, clock gating should use a gate, an and gate. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. So there are 3 cycles in this. The clock gating logic could be based on functional behavior of.

PPT Low Power Design Methodologies and Flows PowerPoint Presentation

Clock Gating Verilog Code Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Clock gating in verilog hi. So there are 3 cycles in this. As the name implies, clock gating should use a gate, an and gate. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. As far as i know the clock signal is fed to the. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Could you explain me what exactly is clock gating. The clock gating logic could be based on functional behavior of.

From www.geeksforgeeks.org

2 to 4 Decoder in Verilog HDL Clock Gating Verilog Code So there are 3 cycles in this. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Could you explain me what exactly is clock gating. As far as i know the clock signal is fed. Clock Gating Verilog Code.

From www.youtube.com

How to generate clock in Verilog HDL YouTube Clock Gating Verilog Code Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Clock gating in verilog hi. So there are 3 cycles in this.. Clock Gating Verilog Code.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Gating Verilog Code Clock gating in verilog hi. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. As the name implies, clock gating should use a gate, an and gate. Could you explain me what exactly is clock. Clock Gating Verilog Code.

From www.chegg.com

Solved Write the Verilog code for the gate diagram. A small Clock Gating Verilog Code Clock gating in verilog hi. So there are 3 cycles in this. Could you explain me what exactly is clock gating. The clock gating logic could be based on functional behavior of. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Glitch free verilog •add a latch to prevent clock glitching •clock gating. Clock Gating Verilog Code.

From www.pinterest.com

Verilog code for Alarm clock on FPGA Alarm clock, Clock, Block diagram Clock Gating Verilog Code Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Could you explain me what exactly is clock gating. Clock. Clock Gating Verilog Code.

From www.youtube.com

Clock gating Example (Eda Playground), Verilog coding YouTube Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: So there are 3 cycles in this. The clock gating logic could be based on functional behavior of. As far as i know the clock signal is fed to the. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with. Clock Gating Verilog Code.

From www.researchgate.net

Conventional ClockGating Scheme. Download Scientific Diagram Clock Gating Verilog Code Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: As far as i know the clock signal is fed to the. You need to have the gating signal toggle on the inactive edge of the clock to. Clock Gating Verilog Code.

From www.researchgate.net

Figure A5. VerilogA code of the clock amplitudebased control Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Could you explain me what exactly is clock gating. As far as i know the clock signal is fed to the. You need to have the gating signal. Clock Gating Verilog Code.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Verilog Code As far as i know the clock signal is fed to the. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Could you explain me what exactly is clock gating. The clock gating logic could be based on functional behavior of. Glitch free verilog •add a latch to prevent clock glitching •clock gating. Clock Gating Verilog Code.

From www.cnblogs.com

clock gating check いつまでも 博客园 Clock Gating Verilog Code Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. Could you explain me what exactly is clock gating. As the name implies, clock gating should use a gate, an and gate. The clock gating logic could be. Clock Gating Verilog Code.

From www.intel.com

2.2.7.3.1. Implementing Clock Gating Clock Gating Verilog Code So there are 3 cycles in this. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. As far as i know the clock signal is fed to the. Clock gating in verilog hi. Learn how to reduce. Clock Gating Verilog Code.

From www.youtube.com

Clock divider by 3 with duty cycle 50 using Verilog YouTube Clock Gating Verilog Code So there are 3 cycles in this. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Could you explain me what exactly is clock gating. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Clock gating in verilog hi. Glitch free verilog •add a. Clock Gating Verilog Code.

From www.researchgate.net

Clock gating scheme Adapted from Hsu & Lin, 2011. Download Scientific Clock Gating Verilog Code As far as i know the clock signal is fed to the. The clock gating logic could be based on functional behavior of. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or. Clock Gating Verilog Code.

From www.chegg.com

Solved 4. Draw the circuit corresponding to the Verilog Clock Gating Verilog Code As far as i know the clock signal is fed to the. Clock gating in verilog hi. The clock gating logic could be based on functional behavior of. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: As the name implies, clock gating should use a gate, an and gate. Learn how to. Clock Gating Verilog Code.

From www.chegg.com

Solved I need only the (verilog code) for clock module and Clock Gating Verilog Code Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Clock gating in verilog hi. So there are 3 cycles in this. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention. Clock Gating Verilog Code.

From ileonsun.github.io

Leon Sun Clock Gating Check Clock Gating Verilog Code Could you explain me what exactly is clock gating. Clock gating in verilog hi. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out =. Clock Gating Verilog Code.

From www.youtube.com

verilog code for SR FLIP FLOP with testbench YouTube Clock Gating Verilog Code Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: As the name implies, clock gating should use a gate, an and gate. You need to have the gating signal toggle on the inactive edge of the clock. Clock Gating Verilog Code.

From slideplayer.com

Verilog Synthesis Synthesis vs. Compilation ppt download Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: As far as i know the clock signal is fed to the. As the name implies, clock gating should use a gate, an and gate. Could you explain me what exactly is clock gating. Glitch free verilog •add a latch to prevent clock glitching. Clock Gating Verilog Code.

From www.researchgate.net

(a) Verilog module which implements a NAND3 based Clock Gating Verilog Code Clock gating in verilog hi. As the name implies, clock gating should use a gate, an and gate. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. As far as i know the clock signal is fed. Clock Gating Verilog Code.

From www.chegg.com

Help me design this Arbiter in Verilog. The clock Clock Gating Verilog Code Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Could you explain me what exactly is clock gating. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. You need to. Clock Gating Verilog Code.

From www.youtube.com

Clock gating Technique in Dff and its verilog code YouTube Clock Gating Verilog Code As far as i know the clock signal is fed to the. As the name implies, clock gating should use a gate, an and gate. So there are 3 cycles in this. The clock gating logic could be based on functional behavior of. Clock gating in verilog hi. Enabling rtl clock gating in a design requires only two modifications to. Clock Gating Verilog Code.

From shashisuman.home.blog

16bit RISC Processor Verilog Code with Clock Gating Shashi’s Blog!! Clock Gating Verilog Code You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Clock gating in verilog hi. Could you explain me what exactly is clock gating. So there are 3 cycles in this. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or. Clock Gating Verilog Code.

From www.linkedin.com

A video blog on latch based clock gating and integrated clock gate cell Clock Gating Verilog Code Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then. Clock Gating Verilog Code.

From mavink.com

Verilog Code For And Gate Clock Gating Verilog Code Clock gating in verilog hi. As far as i know the clock signal is fed to the. The clock gating logic could be based on functional behavior of. So there are 3 cycles in this. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: As the name implies, clock gating should use a. Clock Gating Verilog Code.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Clock Gating Verilog Code As the name implies, clock gating should use a gate, an and gate. Could you explain me what exactly is clock gating. The clock gating logic could be based on functional behavior of. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out. Clock Gating Verilog Code.

From shashisuman.home.blog

16bit RISC Processor Verilog Code with Clock Gating Shashi’s Blog!! Clock Gating Verilog Code As far as i know the clock signal is fed to the. As the name implies, clock gating should use a gate, an and gate. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. The clock gating. Clock Gating Verilog Code.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: So there are 3 cycles in this. The clock gating logic could be based on functional behavior of. As the name implies, clock gating should use a gate, an and gate. Could you explain me what exactly is clock gating. Learn how to reduce. Clock Gating Verilog Code.

From www.youtube.com

xilinx clock gating circuitLow power design technique YouTube Clock Gating Verilog Code As far as i know the clock signal is fed to the. Clock gating in verilog hi. So there are 3 cycles in this. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. Could you explain me. Clock Gating Verilog Code.

From www.slideserve.com

PPT Low Power Design Methodologies and Flows PowerPoint Presentation Clock Gating Verilog Code Could you explain me what exactly is clock gating. As far as i know the clock signal is fed to the. Clock gating in verilog hi. So there are 3 cycles in this. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. The clock gating logic could be based on functional behavior of.. Clock Gating Verilog Code.

From www.youtube.com

Verilog Code of Clock Generator with TB to generate CLK with Varying Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then. Clock Gating Verilog Code.

From www.researchgate.net

a Structure of the Clock selector. b PLL and clock controller Verilog Clock Gating Verilog Code As far as i know the clock signal is fed to the. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: Glitch free verilog •add a latch to prevent clock glitching •clock gating code with. Clock Gating Verilog Code.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation Clock Gating Verilog Code Glitch free verilog •add a latch to prevent clock glitching •clock gating code with glitch prevention latch always @ (enable or clk) begin if !clk then en_out = enable // build latch. The clock gating logic could be based on functional behavior of. As the name implies, clock gating should use a gate, an and gate. Could you explain me. Clock Gating Verilog Code.

From www.slideserve.com

PPT Low Power Design Methodologies and Flows PowerPoint Presentation Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: As far as i know the clock signal is fed to the. Learn how to reduce power dissipation in cmos transistors by using clock and power gating techniques. Clock gating in verilog hi. The clock gating logic could be based on functional behavior of.. Clock Gating Verilog Code.

From www.youtube.com

25 Verilog Clock Divider YouTube Clock Gating Verilog Code Enabling rtl clock gating in a design requires only two modifications to the standard synthesis flow: You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. As far as i know the clock signal is fed to the. The clock gating logic could be based on functional behavior of. Could you explain. Clock Gating Verilog Code.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Clock Gating Verilog Code The clock gating logic could be based on functional behavior of. As the name implies, clock gating should use a gate, an and gate. So there are 3 cycles in this. You need to have the gating signal toggle on the inactive edge of the clock to avoid glitches. Could you explain me what exactly is clock gating. Learn how. Clock Gating Verilog Code.