Clock Generator Vhdl . how to use a clock and do assertions. the vast majority of vhdl designs uses clocked logic, also known as synchronous. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. This example shows how to generate a clock, and give inputs and. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. in many test benches i see the following pattern for clock generation: the next thing we do when writing a vhdl testbench is generate a clock and a reset signal.

from www.chegg.com

the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. how to use a clock and do assertions. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. This example shows how to generate a clock, and give inputs and. in many test benches i see the following pattern for clock generation: the vast majority of vhdl designs uses clocked logic, also known as synchronous.

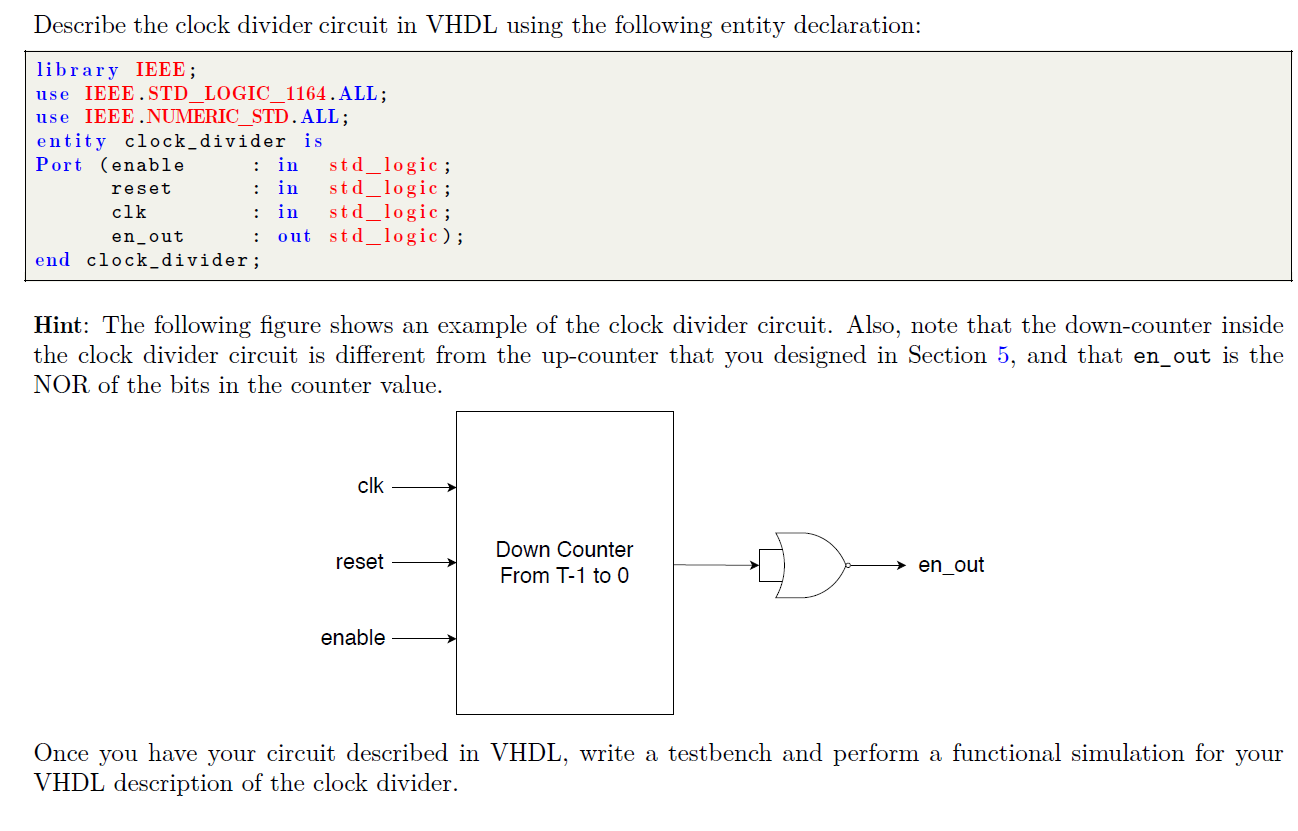

Describe the clock divider circuit in VHDL using the

Clock Generator Vhdl in many test benches i see the following pattern for clock generation: in many test benches i see the following pattern for clock generation: rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the vast majority of vhdl designs uses clocked logic, also known as synchronous. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. This example shows how to generate a clock, and give inputs and. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. how to use a clock and do assertions.

From bestengineeringprojects.com

Clock Signal Generator Circuit Engineering Projects Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the vast majority of vhdl designs uses clocked logic, also known as synchronous. in many test benches i see the following pattern for clock generation: how to use a clock and do assertions. the. Clock Generator Vhdl.

From github.com

GitHub jhpark16/FPGAmuticlockgenerator275MHzXC6SLX9 Multiple (8) high frequency clocks Clock Generator Vhdl generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. how to use a clock and do assertions. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. in many test benches i see the following pattern for clock generation: when you. Clock Generator Vhdl.

From www.researchgate.net

(PDF) A programmable clock generator HDL softcore Clock Generator Vhdl This example shows how to generate a clock, and give inputs and. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. how to use a clock and do assertions. in many test. Clock Generator Vhdl.

From www.youtube.com

How to create a timer in VHDL YouTube Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. This example shows how to generate a clock, and give inputs and. in many test benches i see the. Clock Generator Vhdl.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Vhdl how to use a clock and do assertions. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. the vast majority of vhdl designs uses clocked logic, also known as synchronous. in many test benches i see the following pattern for. Clock Generator Vhdl.

From stackoverflow.com

vhdl clock input to output as a finite state machine Stack Overflow Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the vast majority of vhdl designs uses clocked logic, also known as synchronous. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more. Clock Generator Vhdl.

From www.researchgate.net

Block diagrams of the clock generator (a) and the TFF as a resettable T... Download Scientific Clock Generator Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. in many test benches i see the following pattern for clock generation: generating clock signals in vhdl. Clock Generator Vhdl.

From www.youtube.com

How to generate clock in Verilog HDL Verilog code of clock generator with TB EDA Playground Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the next thing. Clock Generator Vhdl.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale YouTube Clock Generator Vhdl in many test benches i see the following pattern for clock generation: generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the vast majority of vhdl designs uses clocked logic, also known as synchronous. when you need to divide a clock by an integer value, you can implement an integer. Clock Generator Vhdl.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Generator Vhdl generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. how to use a clock and do assertions. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the vast majority of vhdl designs uses clocked logic, also known as. Clock Generator Vhdl.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Based Clock Gating Clock Generator Vhdl how to use a clock and do assertions. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. in many test benches i see the following pattern for clock generation: the next thing we do when writing a vhdl testbench is. Clock Generator Vhdl.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Vhdl when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the next thing we do when writing a vhdl testbench is. Clock Generator Vhdl.

From blog.tindie.com

Tindie Blog Beginner Friendly Clock Generator Kit Offers an Introduction to Digital Logic Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. when you need to. Clock Generator Vhdl.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. in many test benches i see the following pattern for clock generation: generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the next thing we do when writing a vhdl testbench is generate a clock and a. Clock Generator Vhdl.

From www.youtube.com

VHDL alarm clock project YouTube Clock Generator Vhdl in many test benches i see the following pattern for clock generation: the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. the vast majority of vhdl designs uses clocked logic, also known as synchronous. how to use a clock and do assertions. when you need to. Clock Generator Vhdl.

From copyprogramming.com

How do we set time in vhdl simulation for an fpga kit having clock of 100 MHz? Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. how to. Clock Generator Vhdl.

From stackoverflow.com

Generating 2 clock pulses in VHDL Stack Overflow Clock Generator Vhdl how to use a clock and do assertions. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the vast majority of vhdl designs uses clocked logic, also known as synchronous. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. rather. Clock Generator Vhdl.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. . Clock Generator Vhdl.

From www.pinterest.com

FPGA LED blink VHDL FPGA learn by Examples Ep02 VHDL clock divider e... in 2020 Learning Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. how to use a clock and do assertions. This example shows how to generate a clock, and give inputs and. the vast majority of vhdl designs uses clocked logic, also known as synchronous. the next. Clock Generator Vhdl.

From www.slideserve.com

PPT A VHDL nyelv alapjai PowerPoint Presentation ID6115087 Clock Generator Vhdl generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. This example shows how to generate a clock, and give inputs and. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. in many test benches i see the following pattern for clock generation:. Clock Generator Vhdl.

From programmer.ink

Design of digital electronic clock based on VHDL language Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the vast majority of vhdl designs uses clocked logic, also known as synchronous. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. when you need to divide a clock. Clock Generator Vhdl.

From embdev.net

VHDL Double and Single clocks designs compare Clock Generator Vhdl generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. the next thing we do when writing a vhdl testbench is generate a clock and a reset. Clock Generator Vhdl.

From www.youtube.com

Digital Clock in Quartus YouTube Clock Generator Vhdl generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. This example shows how to generate a clock, and give inputs and. in many test benches i see the following pattern for clock generation: how to use a clock and do assertions. when you need to divide a clock by an. Clock Generator Vhdl.

From www.youtube.com

Digital and Analog Clocks using VHDL and FPGA YouTube Clock Generator Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. This example shows how to generate a clock, and give inputs and. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. generating clock. Clock Generator Vhdl.

From github.com

GitHub twinjie/VHDLAlarmClock Alarm clock created on the Nexys 4 DDR FPGA board from Xilinx Clock Generator Vhdl how to use a clock and do assertions. when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. in many test benches i see the following pattern for clock generation: generating clock signals in vhdl is a fundamental aspect of designing. Clock Generator Vhdl.

From embdev.net

VHDL Double and Single clocks designs compare Clock Generator Vhdl when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. the vast majority of vhdl designs uses clocked logic, also known as synchronous. This example shows how to generate a clock, and give inputs and. rather than continuous generation, what we would. Clock Generator Vhdl.

From bestengineeringprojects.com

Clock Signal Generator Circuit Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the vast majority of vhdl designs uses clocked logic, also known as synchronous. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. when you need to divide a clock. Clock Generator Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Clock Generator Vhdl generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the vast majority of vhdl designs uses clocked logic, also known as synchronous. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the next thing we do when writing. Clock Generator Vhdl.

From www.slideserve.com

PPT Lecture 12 Introduction to VHDL PowerPoint Presentation, free download ID9254247 Clock Generator Vhdl when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. in many test benches i see the following pattern for clock generation: the next thing we. Clock Generator Vhdl.

From www.chegg.com

Describe the clock divider circuit in VHDL using the Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. how to use a clock and do assertions. in many test benches i see the following pattern for clock generation: generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. the next thing we do when writing. Clock Generator Vhdl.

From www.youtube.com

VHDL Assignment (Digital Clock with Alarm) YouTube Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. how to use a clock and do assertions. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. when you need to divide a clock by an integer value, you can implement. Clock Generator Vhdl.

From copyprogramming.com

How do we set time in vhdl simulation for an fpga kit having clock of 100 MHz? Clock Generator Vhdl the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. how to use a clock and do assertions. in many test benches i see the following pattern for clock generation: generating clock signals in vhdl is a fundamental aspect of designing and simulating digital systems. rather than. Clock Generator Vhdl.

From picklasopa911.weebly.com

Clock divider mux verilog picklasopa Clock Generator Vhdl the vast majority of vhdl designs uses clocked logic, also known as synchronous. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. how to use a clock and do assertions. in many test benches i see the following pattern for clock generation: when. Clock Generator Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Clock Generator Vhdl rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the next thing we do when writing a vhdl testbench is generate a clock and a reset signal. when you need to divide a clock by an integer value, you can implement an integer clock divider. Clock Generator Vhdl.

From community.cadence.com

Clock Generation in NCVHDL & NCVERILOG Functional Verification Cadence Technology Forums Clock Generator Vhdl when you need to divide a clock by an integer value, you can implement an integer clock divider instead of using a more complex solution. rather than continuous generation, what we would like to do is implement the clock generator inside a process so that a. the next thing we do when writing a vhdl testbench is. Clock Generator Vhdl.