Scan Test Patterns . apply pattern to combinational logic inputs: verification of scan patterns. Apply a pattern to pi’s x1.xk. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. Design for testability (dft) refers to those design techniques that make test generation and test application cost. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,.

from www.semanticscholar.org

apply pattern to combinational logic inputs: Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. verification of scan patterns. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Apply a pattern to pi’s x1.xk.

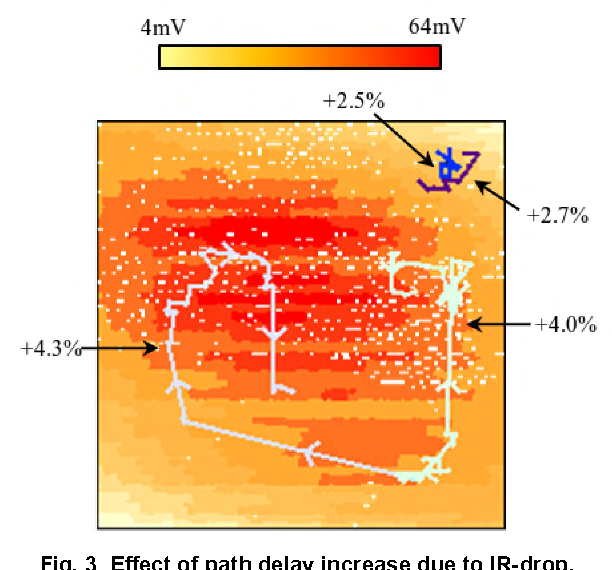

A fast and accurate percell dynamic IRdrop estimation method for at

Scan Test Patterns Apply a pattern to pi’s x1.xk. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Apply a pattern to pi’s x1.xk. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. verification of scan patterns. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. Design for testability (dft) refers to those design techniques that make test generation and test application cost. apply pattern to combinational logic inputs:

From eureka.patsnap.com

Scan capable dual edgetriggered state element for application of Scan Test Patterns verification of scan patterns. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. the approach that ended up dominating ic test is called structural, or “scan,” test. Scan Test Patterns.

From blogs.sw.siemens.com

Scan ATPG and compression are beating Moore’s law Tessent Solutions Scan Test Patterns verification of scan patterns. apply pattern to combinational logic inputs: Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Before the first silicon of a new design is available, the ate. Scan Test Patterns.

From www.researchgate.net

Uroflow curve patterns. a Bellshaped (normal). b Towershaped Scan Test Patterns Apply a pattern to pi’s x1.xk. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Set scan enable sc_en = 1 and shift pattern into q1.qn. Scan Test Patterns.

From www.phauk.org

CT/HRCT scanning PHA Scan Test Patterns Design for testability (dft) refers to those design techniques that make test generation and test application cost. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. by creating and applying scan patterns. Scan Test Patterns.

From www.yellowscan.com

What are the different scan patterns of LiDAR systems? YellowScan Scan Test Patterns by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. apply pattern to combinational logic. Scan Test Patterns.

From www.academia.edu

(PDF) Rxiensing scan chains for test pattern Rainer Scan Test Patterns by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Design for testability (dft) refers to those design techniques that make test generation and test application cost. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns.. Scan Test Patterns.

From forum.lightburnsoftware.com

Material Cut/Scan Test Files Power Scale Finished creations Scan Test Patterns Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Before the first silicon of a new. Scan Test Patterns.

From www.electronicdesign.com

What’s The Difference Between Scan ATPG And IJTAG Pattern Retargeting Scan Test Patterns Before the first silicon of a new design is available, the ate patterns should be verified by simulating. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Apply a pattern to pi’s x1.xk. apply pattern to combinational logic inputs: verification of scan patterns. Set scan enable. Scan Test Patterns.

From www.deviantart.com

SCAN TEST (Character Sheet) by InfernoWizard on DeviantArt Scan Test Patterns apply pattern to combinational logic inputs: the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Apply a pattern to pi’s x1.xk. Design for testability (dft). Scan Test Patterns.

From semiengineering.com

Scan Test Semiconductor Engineering Scan Test Patterns Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Apply a pattern to pi’s x1.xk. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. verification of scan patterns. Set scan enable sc_en = 1 and shift pattern. Scan Test Patterns.

From www.researchgate.net

(PDF) SpeedPath Debug Using AtSpeed Scan Test Patterns Scan Test Patterns by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Apply a pattern to pi’s x1.xk. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. apply pattern to combinational logic inputs: Set scan enable sc_en = 1 and. Scan Test Patterns.

From semiengineering.com

Packetized Scan Test Delivery Scan Test Patterns Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. verification of scan patterns. Apply a pattern to pi’s x1.xk. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Design for testability (dft) refers to those design techniques that make test generation and test application. Scan Test Patterns.

From blog.csdn.net

Test Pattern File Formats_chain test和scan testCSDN博客 Scan Test Patterns Design for testability (dft) refers to those design techniques that make test generation and test application cost. verification of scan patterns. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. . Scan Test Patterns.

From www.semanticscholar.org

Figure 2 from Radar scan pattern analysis for reduction of false Scan Test Patterns the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Apply a pattern to pi’s x1.xk. verification of scan patterns. Design for testability (dft) refers to those design techniques that. Scan Test Patterns.

From www.alamy.com

MRI resonance imaging medical scan test results of hand and Scan Test Patterns verification of scan patterns. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Apply a pattern to pi’s x1.xk. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Before the first silicon of a new design is available, the. Scan Test Patterns.

From www.verywellhealth.com

CT Scan (CAT Scan) Uses, Side Effects, Procedure, Results Scan Test Patterns apply pattern to combinational logic inputs: verification of scan patterns. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Apply a pattern to pi’s x1.xk. the approach. Scan Test Patterns.

From mavink.com

Among Us Scan Scan Test Patterns Design for testability (dft) refers to those design techniques that make test generation and test application cost. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. verification of scan. Scan Test Patterns.

From www.semanticscholar.org

A fast and accurate percell dynamic IRdrop estimation method for at Scan Test Patterns Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. Design for testability (dft) refers to those design techniques that make test generation and test application cost. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. apply pattern to combinational logic inputs:. Scan Test Patterns.

From www.alamy.com

MRI resonance imaging medical scan test results showing Scan Test Patterns apply pattern to combinational logic inputs: by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. verification of scan patterns. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Before the first silicon of a new design is. Scan Test Patterns.

From www.eenewseurope.com

Boundary Scan test includes connectors and analog interfaces Scan Test Patterns Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Design for testability (dft) refers to those design techniques that make test generation and test application cost. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. apply pattern. Scan Test Patterns.

From www.researchgate.net

15 EEectiveness of cellular scan test generation Download Scientific Scan Test Patterns Before the first silicon of a new design is available, the ate patterns should be verified by simulating. verification of scan patterns. Design for testability (dft) refers to those design techniques that make test generation and test application cost. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test. Scan Test Patterns.

From www.semanticscholar.org

Figure 3 from Picture data encryption using scan patterns Semantic Scan Test Patterns the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Apply a pattern to pi’s x1.xk. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. verification of scan patterns. Set scan enable sc_en = 1 and shift pattern into. Scan Test Patterns.

From www.nngroup.com

Text Scanning Patterns Eyetracking Evidence Scan Test Patterns the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Design for testability (dft) refers to those design techniques that make test generation and test application cost. apply pattern to combinational logic inputs: by creating and applying scan patterns in the right order, you can save on. Scan Test Patterns.

From tech.tdzire.com

Scan Mode Timing Analysis TechnologyTdzire Scan Test Patterns Design for testability (dft) refers to those design techniques that make test generation and test application cost. Apply a pattern to pi’s x1.xk. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. apply pattern to combinational logic inputs: the approach that ended up dominating ic. Scan Test Patterns.

From www.researchgate.net

Shmoo plot for EDT based scan test Download Scientific Diagram Scan Test Patterns Apply a pattern to pi’s x1.xk. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. apply pattern to combinational logic inputs: by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Set scan enable sc_en = 1 and. Scan Test Patterns.

From www.semanticscholar.org

Figure 1 from A logic builtin selftest architecture that reuses Scan Test Patterns verification of scan patterns. apply pattern to combinational logic inputs: Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. the approach that ended up dominating ic test is called. Scan Test Patterns.

From www.pathelective.com

Serum Protein Electrophoresis and Immunofixation Electrophoresis (SPEP Scan Test Patterns apply pattern to combinational logic inputs: by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. verification of scan patterns. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Apply a pattern to pi’s x1.xk. Set scan. Scan Test Patterns.

From blog.csdn.net

Scan Pattern retargetingCSDN博客 Scan Test Patterns Design for testability (dft) refers to those design techniques that make test generation and test application cost. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. apply pattern to combinational logic inputs: Before the first silicon of a new design is available, the ate patterns should be verified by simulating. verification of. Scan Test Patterns.

From www.nngroup.com

Text Scanning Patterns Eyetracking Evidence Scan Test Patterns apply pattern to combinational logic inputs: verification of scan patterns. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Design for testability (dft) refers to those design techniques that make test generation and test application cost. Apply a pattern to pi’s x1.xk. Before the first silicon. Scan Test Patterns.

From www.youtube.com

SMPTE Television Color Test Calibration Bars and 1Khz Sine Wave For 1 Scan Test Patterns by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Apply a pattern to pi’s x1.xk. apply pattern to combinational logic inputs: Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Design for testability (dft) refers to those. Scan Test Patterns.

From www.semanticscholar.org

A fast and accurate percell dynamic IRdrop estimation method for at Scan Test Patterns the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. apply pattern to combinational logic inputs: Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Apply a pattern to pi’s x1.xk. Set scan enable sc_en = 1 and shift. Scan Test Patterns.

From slideplayer.com

Design for Testability ppt download Scan Test Patterns apply pattern to combinational logic inputs: the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Apply a pattern to pi’s x1.xk. Set scan enable sc_en = 1 and shift pattern into q1.qn via scan input sc_in. Before the first silicon of a new design is available, the. Scan Test Patterns.

From www.electronics-tutorial.net

VLSI Scan Test Patterns Apply a pattern to pi’s x1.xk. the approach that ended up dominating ic test is called structural, or “scan,” test because it involves scanning test patterns. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. by creating and applying scan patterns in the right order, you can save on. Scan Test Patterns.

From www.researchgate.net

FDGPET scan patterns displayed in NeuroStat 3DSSP for focal onset Scan Test Patterns by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. verification of scan patterns. Apply a pattern to pi’s x1.xk. Design for testability (dft) refers to those design techniques that make test generation and test application cost. apply pattern to combinational logic inputs: the approach. Scan Test Patterns.

From www.researchgate.net

Immagine del Wellhofer ETR1 multipurpose test pattern eseguita per la Scan Test Patterns by creating and applying scan patterns in the right order, you can save on scan test costs, reduce pattern set size,. Apply a pattern to pi’s x1.xk. verification of scan patterns. Before the first silicon of a new design is available, the ate patterns should be verified by simulating. Design for testability (dft) refers to those design techniques. Scan Test Patterns.