State The Function Of Ale And Ready Pin Of 8086 . All signals must be buffered. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. A positive pulse is generated each time the processor. Inserts wait states into the timing. Nmi ates into the timing of the microprocessor. This is done to inform the peripherals and memory devices about. Ale it stands for address enable latch and is available at pin 25. A positive pulse is generated each time the processor begins any operation. It goes high during t1. The ale pin controls a set of latches. 26 rows ale it stands for address enable latch and is available at pin 25. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin.

from wiringfixfourscores.z13.web.core.windows.net

This is done to inform the peripherals and memory devices about. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. A positive pulse is generated each time the processor. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. Inserts wait states into the timing. 26 rows ale it stands for address enable latch and is available at pin 25. Ale it stands for address enable latch and is available at pin 25. Nmi ates into the timing of the microprocessor. It goes high during t1. A positive pulse is generated each time the processor begins any operation.

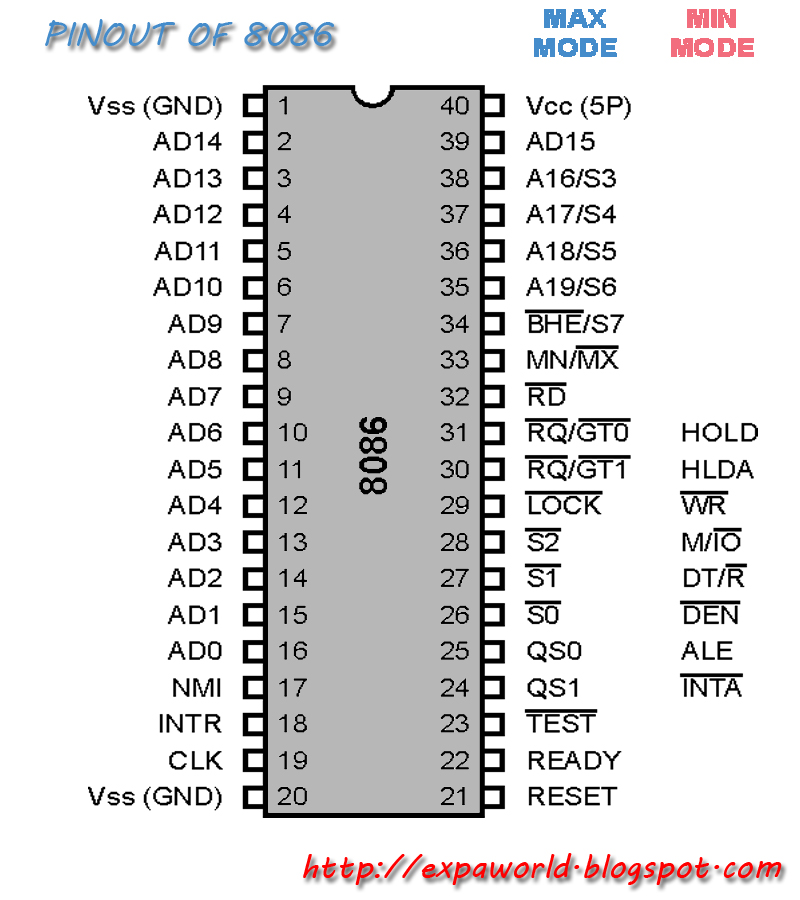

8086 Pin Diagram

State The Function Of Ale And Ready Pin Of 8086 The ale pin controls a set of latches. 26 rows ale it stands for address enable latch and is available at pin 25. The ale pin controls a set of latches. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. All signals must be buffered. It goes high during t1. A positive pulse is generated each time the processor. Nmi ates into the timing of the microprocessor. Inserts wait states into the timing. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. This is done to inform the peripherals and memory devices about. A positive pulse is generated each time the processor begins any operation. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. Ale it stands for address enable latch and is available at pin 25.

From diagramlibrarydialler.z21.web.core.windows.net

8086 Microprocessor Pin Diagram State The Function Of Ale And Ready Pin Of 8086 If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. It goes high during t1. This is done to inform the peripherals and memory devices about. 26 rows ale it stands for address enable latch and is available at pin 25. Inserts wait states into the timing. The microprocessor 8086 sends this. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT 8086 Hardware Specifications PowerPoint Presentation, free State The Function Of Ale And Ready Pin Of 8086 It goes high during t1. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. Nmi ates into the timing of the microprocessor. 26 rows ale it stands for address enable latch and is available at pin 25. The ale pin controls a set of latches. Ale it. State The Function Of Ale And Ready Pin Of 8086.

From www.slideshare.net

8086 pin configuration State The Function Of Ale And Ready Pin Of 8086 All signals must be buffered. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. A positive pulse is generated each time the processor begins any operation. This is done to inform the peripherals and memory devices about. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic. State The Function Of Ale And Ready Pin Of 8086.

From www.goseeko.com

What is Minimum Mode Configuration of 8086? Goseeko blog State The Function Of Ale And Ready Pin Of 8086 Ale it stands for address enable latch and is available at pin 25. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. 26 rows ale it stands for address. State The Function Of Ale And Ready Pin Of 8086.

From diagramlibraryreopens.z21.web.core.windows.net

8086 Pin Diagram State The Function Of Ale And Ready Pin Of 8086 The ale pin controls a set of latches. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. A positive pulse is generated each time the processor. All signals must be buffered. Nmi ates into the timing of the microprocessor. A positive pulse is generated each time the processor begins any operation.. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT 8086 Microprocessor PowerPoint Presentation, free download ID State The Function Of Ale And Ready Pin Of 8086 The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. All signals must be buffered. This is done to inform the peripherals and memory devices about. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. Whenever an address is present in the. State The Function Of Ale And Ready Pin Of 8086.

From pdfprof.com

microprocessor 8086 pin diagram description pdf State The Function Of Ale And Ready Pin Of 8086 A positive pulse is generated each time the processor. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. Whenever an address is present in the multiplexed address and data. State The Function Of Ale And Ready Pin Of 8086.

From www.geeksforgeeks.org

Minimum mode configuration of 8086 microprocessor (Min mode State The Function Of Ale And Ready Pin Of 8086 All signals must be buffered. Ale it stands for address enable latch and is available at pin 25. Nmi ates into the timing of the microprocessor. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. It goes high during t1. Inserts wait states into the timing. Whenever an address is present in the multiplexed. State The Function Of Ale And Ready Pin Of 8086.

From techatronic.com

What is 8086 Microprocessor ? 8086 Pin Diagram 8086 architecture State The Function Of Ale And Ready Pin Of 8086 A positive pulse is generated each time the processor begins any operation. Ale it stands for address enable latch and is available at pin 25. The ale pin controls a set of latches. It goes high during t1. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the.. State The Function Of Ale And Ready Pin Of 8086.

From www.etechnog.com

Microprocessor 8086 Pinout Diagram and Pin Description ETechnoG State The Function Of Ale And Ready Pin Of 8086 Ale it stands for address enable latch and is available at pin 25. A positive pulse is generated each time the processor. A positive pulse is generated each time the processor begins any operation. The ale pin controls a set of latches. Inserts wait states into the timing. All signals must be buffered. If the ready pin is placed at. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT PIN DIAGRAM OF 8086 PowerPoint Presentation, free download ID State The Function Of Ale And Ready Pin Of 8086 The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. Nmi ates into the timing of the microprocessor. Ale it stands for address enable latch and is available at pin 25. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. It goes high during t1. The. State The Function Of Ale And Ready Pin Of 8086.

From wiringfixfourscores.z13.web.core.windows.net

8086 Pin Diagram State The Function Of Ale And Ready Pin Of 8086 If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. Ale it stands for address enable latch and is available at pin 25. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. If placed at a logic 0, the microprocessor enters into wait. State The Function Of Ale And Ready Pin Of 8086.

From mungfali.com

Pin Diagram Of 8086 Microprocessor State The Function Of Ale And Ready Pin Of 8086 If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. This is done to inform the peripherals and memory devices about. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. If placed at a logic 0, the microprocessor enters into wait states and. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT 8086/8088 Microprocessor PowerPoint Presentation ID441559 State The Function Of Ale And Ready Pin Of 8086 If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. A positive pulse is generated each time the processor begins any operation. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. 26 rows ale it stands for address enable latch and is available at pin 25.. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT 8086 Pin diagram PowerPoint Presentation, free download ID4570821 State The Function Of Ale And Ready Pin Of 8086 Ale it stands for address enable latch and is available at pin 25. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. A positive pulse is generated each time the processor begins any operation. A positive pulse is generated each time the processor. 26 rows ale it. State The Function Of Ale And Ready Pin Of 8086.

From codingatharva.blogspot.com

5 Signal Groups/ Pin descriptions of 8086 Coding Atharva State The Function Of Ale And Ready Pin Of 8086 It goes high during t1. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. 26 rows ale it stands for address enable latch and is available at pin 25. Nmi ates into. State The Function Of Ale And Ready Pin Of 8086.

From diagramlibrarydialler.z21.web.core.windows.net

Draw The Pin Diagram Of 8086 Microprocessor State The Function Of Ale And Ready Pin Of 8086 The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. All signals must be buffered. Inserts wait states into the timing. A positive pulse is generated each time the processor begins any operation. Ale it stands for address enable latch and is available at pin 25. The ale pin controls a set of latches. This. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT Chapter 9 8086/8088 Hardware Specifications PowerPoint State The Function Of Ale And Ready Pin Of 8086 A positive pulse is generated each time the processor. The ale pin controls a set of latches. This is done to inform the peripherals and memory devices about. All signals must be buffered. It goes high during t1. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. Inserts wait states into the timing. 26. State The Function Of Ale And Ready Pin Of 8086.

From slideplayer.com

8086 Microprocessor. ppt download State The Function Of Ale And Ready Pin Of 8086 If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. All signals must be buffered. The ale pin controls a set of latches. Inserts wait states into the timing. This is done to inform the peripherals and memory devices about. It goes high during t1. Nmi ates into the timing of the. State The Function Of Ale And Ready Pin Of 8086.

From guidelibroos.z21.web.core.windows.net

8086 Pin Diagram State The Function Of Ale And Ready Pin Of 8086 26 rows ale it stands for address enable latch and is available at pin 25. Ale it stands for address enable latch and is available at pin 25. Nmi ates into the timing of the microprocessor. All signals must be buffered. It goes high during t1. A positive pulse is generated each time the processor. Whenever an address is present. State The Function Of Ale And Ready Pin Of 8086.

From digitallocha.blogspot.com

Digital Locha ALE signal of 8086/8088 State The Function Of Ale And Ready Pin Of 8086 Nmi ates into the timing of the microprocessor. Inserts wait states into the timing. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. A positive pulse is generated each time the processor begins any operation. The ale pin controls a set of latches. All signals must be buffered. The microprocessor 8086. State The Function Of Ale And Ready Pin Of 8086.

From www.geeksforgeeks.org

Maximum mode configuration of 8086 microprocessor (Max mode State The Function Of Ale And Ready Pin Of 8086 The ale pin controls a set of latches. A positive pulse is generated each time the processor. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. It goes high during t1. Inserts wait states into the timing. Whenever an address is present in the multiplexed address and data bus, then the. State The Function Of Ale And Ready Pin Of 8086.

From www.eeeguide.com

8086 Microprocessor Pin Diagram and 8088 Pin Diagram State The Function Of Ale And Ready Pin Of 8086 The ale pin controls a set of latches. Nmi ates into the timing of the microprocessor. 26 rows ale it stands for address enable latch and is available at pin 25. A positive pulse is generated each time the processor begins any operation. All signals must be buffered. The microprocessor 8086 sends this signal to latch the address into the. State The Function Of Ale And Ready Pin Of 8086.

From studylib.net

8086 Pin Functions (2) State The Function Of Ale And Ready Pin Of 8086 A positive pulse is generated each time the processor. Inserts wait states into the timing. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. The ale pin controls a set of latches. This is done to inform the peripherals and memory devices about. The microprocessor 8086 sends this signal to latch. State The Function Of Ale And Ready Pin Of 8086.

From www.researchgate.net

RESET, CLK and READY pins in 8086/8088 microprocessors and their State The Function Of Ale And Ready Pin Of 8086 All signals must be buffered. 26 rows ale it stands for address enable latch and is available at pin 25. Nmi ates into the timing of the microprocessor. The ale pin controls a set of latches. This is done to inform the peripherals and memory devices about. A positive pulse is generated each time the processor. It goes high during. State The Function Of Ale And Ready Pin Of 8086.

From www.coursehero.com

[Solved] Answer all questions in detail 1. Draw Pin diagram of 8086 State The Function Of Ale And Ready Pin Of 8086 Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. A positive pulse is generated each time the processor. The ale pin controls a set of latches. All signals must be buffered. A positive pulse is generated each time the processor begins any operation. Ale it stands for address enable latch and. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT 8086 Pin diagram PowerPoint Presentation, free download ID4570821 State The Function Of Ale And Ready Pin Of 8086 26 rows ale it stands for address enable latch and is available at pin 25. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. The ale pin controls a set of latches. A positive pulse is generated each time the processor. This is done to inform the peripherals and memory devices. State The Function Of Ale And Ready Pin Of 8086.

From www.scribd.com

Pin Functions of the 8086 Microprocessor An Overview of the Roles and State The Function Of Ale And Ready Pin Of 8086 Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. A positive pulse is generated each time the processor. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. If placed at a logic 0, the microprocessor enters into wait states and remains idle. State The Function Of Ale And Ready Pin Of 8086.

From diagramdataclemently.z21.web.core.windows.net

8086 Pin Diagram State The Function Of Ale And Ready Pin Of 8086 The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. If placed at a logic 0, the microprocessor enters into wait states and remains idle if logic 1, no effect on the. Nmi ates into the timing. State The Function Of Ale And Ready Pin Of 8086.

From www.brainkart.com

8086 signals State The Function Of Ale And Ready Pin Of 8086 Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. 26 rows ale it stands for address enable latch and is available at pin 25. This is done to inform the peripherals and memory devices about. The ale pin controls a set of latches. A positive pulse is generated each time the. State The Function Of Ale And Ready Pin Of 8086.

From www.youtube.com

Pin Configuration of 8086 Microprocessor YouTube State The Function Of Ale And Ready Pin Of 8086 The ale pin controls a set of latches. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. If the ready pin is placed at logic 0 level, the microprocess r enters into wait states and. It goes high during t1. A positive pulse is generated each time the processor begins any. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT PIN DIAGRAM OF 8086 PowerPoint Presentation, free download ID State The Function Of Ale And Ready Pin Of 8086 The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. Ale it stands for address enable latch and is available at pin 25. All signals must be buffered. Whenever an address is present in the multiplexed address and data bus, then the microprocessor enables this pin. 26 rows ale it stands for address enable latch. State The Function Of Ale And Ready Pin Of 8086.

From www.slideserve.com

PPT 8086/8088 Microprocessor PowerPoint Presentation ID441559 State The Function Of Ale And Ready Pin Of 8086 Inserts wait states into the timing. Ale it stands for address enable latch and is available at pin 25. The ale pin controls a set of latches. All signals must be buffered. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. If placed at a logic 0, the microprocessor enters into wait states and. State The Function Of Ale And Ready Pin Of 8086.

From learnloner.com

Pin Diagram Of 8086 And Functions Of Its 40 Pins State The Function Of Ale And Ready Pin Of 8086 It goes high during t1. This is done to inform the peripherals and memory devices about. The microprocessor 8086 sends this signal to latch the address into the intel 8282/8283 latch. Inserts wait states into the timing. 26 rows ale it stands for address enable latch and is available at pin 25. The ale pin controls a set of latches.. State The Function Of Ale And Ready Pin Of 8086.

From ioesolutions.esign.com.np

IOE Note Microprocessor [EX 551] Microprocessor System State The Function Of Ale And Ready Pin Of 8086 A positive pulse is generated each time the processor begins any operation. A positive pulse is generated each time the processor. Inserts wait states into the timing. This is done to inform the peripherals and memory devices about. Ale it stands for address enable latch and is available at pin 25. 26 rows ale it stands for address enable latch. State The Function Of Ale And Ready Pin Of 8086.