Clock Synchronization Fpga . The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. How to do clock domain crossing in an fpga.

from e2e.ti.com

Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: How to do clock domain crossing in an fpga.

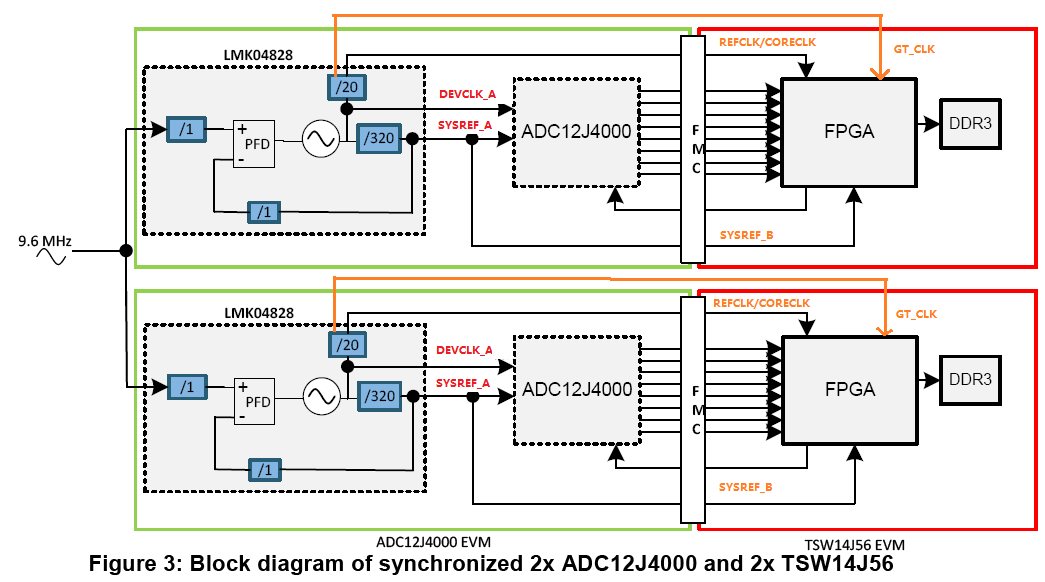

How to synchronize multiple ADCs and FPGAs across JESD204B link Data

Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. How to do clock domain crossing in an fpga. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes:

From numato.com

Styx How to use Xilinx Zynq PS PLL Clocks in FPGA Fabric Numato Lab Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is. Clock Synchronization Fpga.

From surf-vhdl.com

How to Connect an ADC to an FPGA SurfVHDL Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. How to. Clock Synchronization Fpga.

From e2e.ti.com

How to synchronize multiple ADCs and FPGAs across JESD204B link Data Clock Synchronization Fpga How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools. Clock Synchronization Fpga.

From blog.csdn.net

【数字IC/FPGA学习记录】时钟抖动(clock jitter )和时钟偏移( clock skew)是什么意思?CTS (时钟树综合)对 Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which. Clock Synchronization Fpga.

From igorfreire.com.br

Clock Synchronization Algorithms Over PTPUnaware Networks Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock. Clock Synchronization Fpga.

From www.silicom.dk

Time Synchronization using FPGA SmartNICs Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. How to. Clock Synchronization Fpga.

From www.researchgate.net

Clock domain crossing with TMR and sampling uncertainty. Download Clock Synchronization Fpga How to do clock domain crossing in an fpga. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the. Clock Synchronization Fpga.

From www.mdpi.com

Electronics Free FullText Synchronization and Sampling Time Clock Synchronization Fpga How to do clock domain crossing in an fpga. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools. Clock Synchronization Fpga.

From www.embedded.com

Asynchronous reset synchronization and distribution ASICs and FPGAs Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. How to do clock domain crossing in an fpga. Robust clock routing and the strategic placement of clock buffers. Clock Synchronization Fpga.

From www.youtube.com

6 How to Generate a Slow Clock on an FPGA Board? Verilog Stepby Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. How to. Clock Synchronization Fpga.

From www.pantechsolutions.net

Implementation of Digital Clock using Spartan3an FPGA Evaluation Kit Clock Synchronization Fpga How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic. Clock Synchronization Fpga.

From www.researchgate.net

(PDF) Clock Synchronization Algorithms Over PTPUnaware Networks Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which. Clock Synchronization Fpga.

From www.researchgate.net

(PDF) Synchronization Techniques for Crossing Multiple Clock Domains in Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: How. Clock Synchronization Fpga.

From www.silicom.dk

Time Synchronization using FPGA SmartNICs Clock Synchronization Fpga How to do clock domain crossing in an fpga. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools may assume you are only constrained by the clock period, but in reality you want an even faster. Clock Synchronization Fpga.

From www.techdesignforums.com

FPGAs deal with power and clocking challenges at 20nm Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is. Clock Synchronization Fpga.

From www.youtube.com

PLLs & Clocks FPGA Basics Episode 5 YouTube Clock Synchronization Fpga How to do clock domain crossing in an fpga. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools. Clock Synchronization Fpga.

From www.researchgate.net

(PDF) Synchronization Techniques for Crossing Multiple Clock Domains in Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which. Clock Synchronization Fpga.

From www.scientific.net

A New Clock Synchronization Method for MultiFPGA Systems Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools. Clock Synchronization Fpga.

From www.mdpi.com

Photonics Free FullText Fast Frame Synchronization Design and FPGA Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr. Clock Synchronization Fpga.

From slideplayer.com

RIBF DAQ Hidetada Baba. ppt download Clock Synchronization Fpga Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust. Clock Synchronization Fpga.

From www.guzik.com

FPGA Accelerated RF Wideband Measurements Guzik Technical Enterprises Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. How to do clock domain crossing in an fpga. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which cross clock domains in tmr. Clock Synchronization Fpga.

From semiwiki.com

Clock Domain Crossing in FPGA SemiWiki Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock. Clock Synchronization Fpga.

From journals.sagepub.com

A New Design of Clock Synchronization Algorithm Jingmeng Liu, Xuerong Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: The tools may assume you are only constrained by the clock. Clock Synchronization Fpga.

From www.researchgate.net

An illustration of clock frequency synchronization and of full clock Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. How to do clock domain crossing in an fpga. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. For intel® hyperflex™ architecture fpgas, synchronize the. Clock Synchronization Fpga.

From www.allaboutcircuits.com

Clock Signal Management Clock Resources of FPGAs Technical Articles Clock Synchronization Fpga Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools may assume you are only constrained by the clock. Clock Synchronization Fpga.

From www.omicron-lab.com

PTP Time Synchronization (IEEE1588) Clock Synchronization Fpga For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools. Clock Synchronization Fpga.

From electronica.guru

Altera III Cyclone FPGA problema de sincronización de entrada Electronica Clock Synchronization Fpga Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Signals which. Clock Synchronization Fpga.

From www.techdesignforums.com

Enabling FPGA prototyping of large ASIC and SoC designs Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr circuits may suffer. Clock Synchronization Fpga.

From www.mdpi.com

Electronics Free FullText Synchronization and Sampling Time Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two. Clock Synchronization Fpga.

From www.ni.com

Advanced Synchronization Technologies for CompactRIO and NI Industrial Clock Synchronization Fpga How to do clock domain crossing in an fpga. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: For intel® hyperflex™ architecture fpgas, synchronize. Clock Synchronization Fpga.

From www.synopsys.com

Automating Synchronous Signal Distribution in Multiple FPGAs with HAPS Clock Synchronization Fpga How to do clock domain crossing in an fpga. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools may assume you are only constrained by the clock period, but in reality you want an even faster. Clock Synchronization Fpga.

From www.researchgate.net

Clock generation and synchronization requirement for an 8channel OSCR Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: How to do clock domain crossing in an fpga. Robust clock routing and the strategic. Clock Synchronization Fpga.

From www.scientific.net

Implementation of Clock Synchronization in PTN Based on FPGA Clock Synchronization Fpga The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is to provide. How to do clock domain crossing in an fpga. For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Signals which cross clock domains in tmr circuits may suffer. Clock Synchronization Fpga.

From colinoflynn.com

Experimenting with Metastability and Multiple Clocks on FPGAs Colin O Clock Synchronization Fpga How to do clock domain crossing in an fpga. Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: For intel® hyperflex™ architecture fpgas, synchronize the clock crossing paths before entering combinational logic. Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools. Clock Synchronization Fpga.

From igorfreire.com.br

An FPGAbased Design of a Packetized Fronthaul Testbed with IEEE 1588 Clock Synchronization Fpga Signals which cross clock domains in tmr circuits may suffer from the combined effects of two failure modes: Robust clock routing and the strategic placement of clock buffers contribute to a reliable and efficient network. The tools may assume you are only constrained by the clock period, but in reality you want an even faster route, since the objective is. Clock Synchronization Fpga.