Clock Skew Explained . Special attention is given to. In this blog post, we’ll delve into this crucial. The clock skew between two points x and y in a semicoductor ic is given. Clock skew in synchronous digital circuit systems. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals.

from www.slideserve.com

This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew in synchronous digital circuit systems. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. The clock skew between two points x and y in a semicoductor ic is given. Special attention is given to. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In this blog post, we’ll delve into this crucial.

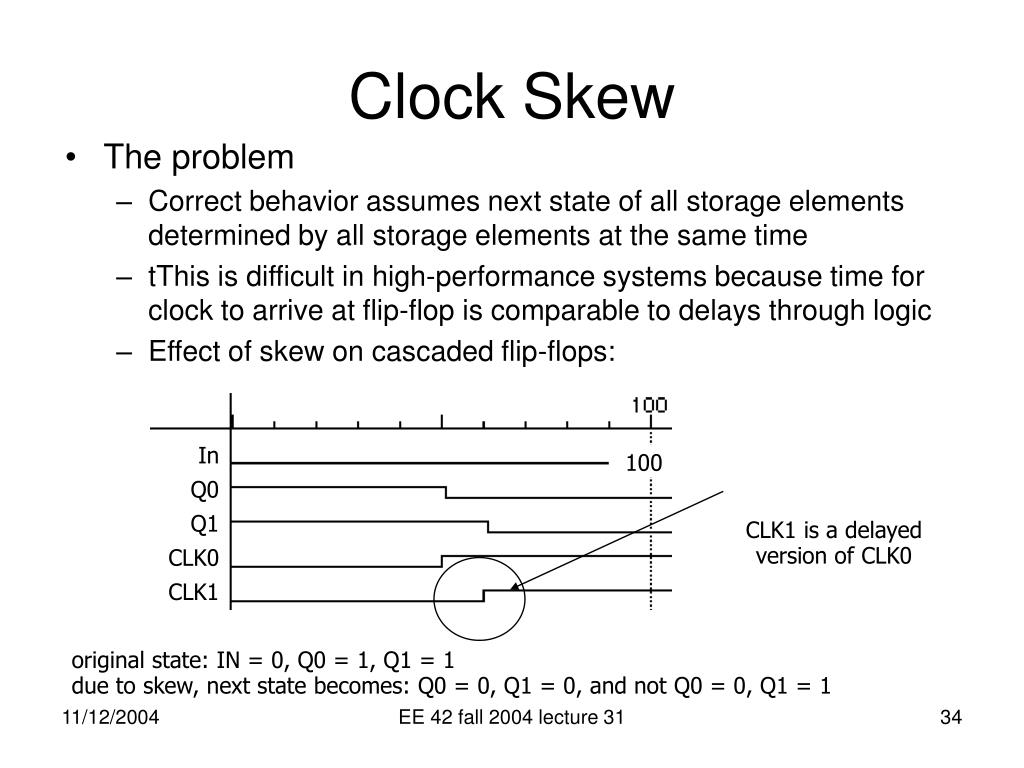

PPT Lecture 31 FlipFlops, Clocks, Timing PowerPoint Presentation

Clock Skew Explained Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Special attention is given to. In this blog post, we’ll delve into this crucial. The clock skew between two points x and y in a semicoductor ic is given. Clock skew in synchronous digital circuit systems.

From www.slideserve.com

PPT Chapter 10 PowerPoint Presentation, free download ID6062070 Clock Skew Explained In this blog post, we’ll delve into this crucial. Clock skew in synchronous digital circuit systems. The clock skew between two points x and y in a semicoductor ic is given. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Clock skew, in simple terms, is the difference in timing between. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skewing Sequential Logic Synthesis and Verification Clock Skew Explained Special attention is given to. In this blog post, we’ll delve into this crucial. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. The clock skew between two points. Clock Skew Explained.

From www.slideserve.com

PPT Chapter 11 Timing Issues in Digital Systems PowerPoint Clock Skew Explained Special attention is given to. In this blog post, we’ll delve into this crucial. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. The clock skew between two points x and y in a semicoductor ic is given. Clock skew, in simple terms, is the. Clock Skew Explained.

From www.slideserve.com

PPT Lecture 31 FlipFlops, Clocks, Timing PowerPoint Presentation Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew is the variation in the arrival. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID1132940 Clock Skew Explained Special attention is given to. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. The clock skew between two points x and y in a semicoductor ic is given. Clock skew in synchronous digital circuit systems. This application note discusses various types of skew, propagation delays, and phase error/phase offset in. Clock Skew Explained.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Skew Explained Clock skew in synchronous digital circuit systems. The clock skew between two points x and y in a semicoductor ic is given. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition. Clock Skew Explained.

From www.slideserve.com

PPT Clock and Synchronization PowerPoint Presentation, free download Clock Skew Explained Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In this blog post, we’ll delve into this crucial. Special attention is given to. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Clock skew in synchronous digital circuit systems.. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID1132940 Clock Skew Explained Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID1132940 Clock Skew Explained This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Special attention is given to. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In this blog post, we’ll delve into this crucial. Clock skew is defined as the variations in the. Clock Skew Explained.

From www.youtube.com

What is Clock Skew ? The Positive and Negative Clock Skew Explained Clock Skew Explained This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Special attention is given to. The clock skew between two points x and y in a semicoductor ic is given. In this blog post, we’ll delve into this crucial. Clock skew in synchronous digital circuit systems. Clock skew is defined as the variations in. Clock Skew Explained.

From www.scribd.com

STA Explanation of Clock Skew Concepts in VLSI by ANKIT MAHAJAN Clock Skew Explained Special attention is given to. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. The clock skew between two points x and y in a semicoductor ic is given.. Clock Skew Explained.

From www.slideserve.com

PPT Timing Faults in VLSI circuits PowerPoint Presentation, free Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. In this blog post, we’ll delve into this crucial. Special attention is given to. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew in synchronous digital circuit systems.. Clock Skew Explained.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Clock Skew Explained Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew is defined as the variations in the arrival time of clock transition in. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Explained Clock skew in synchronous digital circuit systems. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. In this blog post, we’ll delve into this crucial. This application. Clock Skew Explained.

From www.slideserve.com

PPT The clock PowerPoint Presentation, free download ID2403529 Clock Skew Explained Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew in synchronous digital circuit systems. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. This application note discusses various types of skew, propagation delays, and phase error/phase offset. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID1132940 Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. In this blog post, we’ll delve. Clock Skew Explained.

From studylib.net

Clock skew Clock Skew Explained In this blog post, we’ll delve into this crucial. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Special attention is given to. The clock skew between two points x and y in a semicoductor. Clock Skew Explained.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Special attention is given to. Clock skew, in simple terms, is the difference in timing between two or more signals, often. Clock Skew Explained.

From mahajankankit.medium.com

STA Explanation of Clock Skew Concepts in VLSI by ANKIT MAHAJAN Medium Clock Skew Explained Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. In this blog post, we’ll delve into this crucial. Clock skew, in simple terms, is the difference in. Clock Skew Explained.

From www.slideserve.com

PPT Signal and Timing Parameters I Common Clock Class 2 PowerPoint Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew is defined as the variations in. Clock Skew Explained.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Clock Skew Explained Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. In this blog post, we’ll delve into this crucial. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew in synchronous digital circuit systems. Special attention is given to.. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Explained Clock skew in synchronous digital circuit systems. In this blog post, we’ll delve into this crucial. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. The clock skew between two points x and y in a semicoductor ic is given. Special attention is given to. This application note discusses various types. Clock Skew Explained.

From www.slideserve.com

PPT Chapter 10 PowerPoint Presentation, free download ID6062070 Clock Skew Explained Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. In this blog post, we’ll delve into this crucial. The clock skew between two points x and y. Clock Skew Explained.

From www.slideserve.com

PPT EE365 Adv. Digital Circuit Design Clarkson University Lecture 13 Clock Skew Explained Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. In this blog post, we’ll delve into this crucial. The clock skew between two points x and y. Clock Skew Explained.

From www.slideshare.net

Clock Skew 1 Clock Skew Explained Special attention is given to. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. In this blog post, we’ll delve into this crucial. This application note discusses. Clock Skew Explained.

From www.slideserve.com

PPT The clock PowerPoint Presentation, free download ID2403529 Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a. Clock Skew Explained.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Skew Explained Clock skew in synchronous digital circuit systems. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. The clock skew between two points x and y in a semicoductor ic is given. Special attention is given. Clock Skew Explained.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Clock Skewtolerant circuits Clock Skew Explained Clock skew in synchronous digital circuit systems. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. In this blog post, we’ll delve into this crucial. The clock skew between two points x and y in a semicoductor ic is given. Clock skew, in simple terms,. Clock Skew Explained.

From webdocs.cs.ualberta.ca

Clockskew calculation Clock Skew Explained Clock skew in synchronous digital circuit systems. Clock skew, in simple terms, is the difference in timing between two or more signals, often involving data and clock signals. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. The clock skew between two points x and. Clock Skew Explained.

From www.slideserve.com

PPT DELAY INSERTION METHOD IN CLOCK SKEW SCHEDULING PowerPoint Clock Skew Explained Clock skew in synchronous digital circuit systems. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by. Clock Skew Explained.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Skew Explained In this blog post, we’ll delve into this crucial. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. Clock skew is defined as the variations in the arrival time. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. This application note discusses various types of skew, propagation delays, and phase error/phase offset in general. In this blog post, we’ll. Clock Skew Explained.

From www.vrogue.co

How To Use The Skew Function vrogue.co Clock Skew Explained In this blog post, we’ll delve into this crucial. The clock skew between two points x and y in a semicoductor ic is given. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Special attention is given to. Clock skew is the variation in the arrival time of a clock transition. Clock Skew Explained.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID518276 Clock Skew Explained The clock skew between two points x and y in a semicoductor ic is given. Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. This application note. Clock Skew Explained.

From courses.cs.washington.edu

Clock skew Clock Skew Explained Clock skew is the variation in the arrival time of a clock transition at different clocked elements, caused by an imbalance in the clock. Clock skew is defined as the variations in the arrival time of clock transition in an integrated circuit. Special attention is given to. This application note discusses various types of skew, propagation delays, and phase error/phase. Clock Skew Explained.