How To Make A Clock Divider . In this section, we can use a counter with a comparator to. This is the simplest clock divider you can implement into an fpga or asic. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. The frequency of the output. A simple clock divider circuit combines combinational and clocked digital logic. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated and verified on fpga. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock.

from dusty-clouds.com

This is the simplest clock divider you can implement into an fpga or asic. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated and verified on fpga. A simple clock divider circuit combines combinational and clocked digital logic. In this section, we can use a counter with a comparator to. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. The frequency of the output. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock.

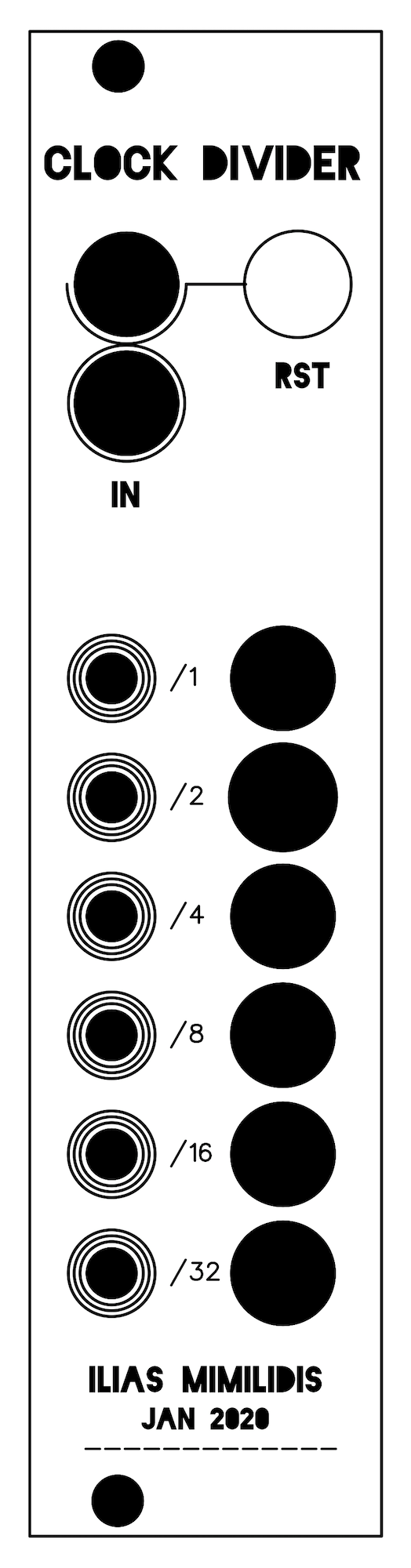

CLOCK DIVIDER Dusty Clouds

How To Make A Clock Divider In this section, we can use a counter with a comparator to. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. The verilog clock divider is simulated and verified on fpga. This is the simplest clock divider you can implement into an fpga or asic. A simple clock divider circuit combines combinational and clocked digital logic. The frequency of the output. In this section, we can use a counter with a comparator to. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge.

From www.synthtopia.com

An Introduction To Modular Synthesizer Clocks & Clock Dividers Synthtopia How To Make A Clock Divider The verilog clock divider is simulated and verified on fpga. In this section, we can use a counter with a comparator to. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The frequency of the output. This verilog project provides full verilog code for the clock divider on fpga. How To Make A Clock Divider.

From dokumen.tips

(PPT) Clock Dividers Made Easy DOKUMEN.TIPS How To Make A Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. A simple clock divider circuit combines combinational and clocked digital logic. This is the simplest clock divider you can implement into an. How To Make A Clock Divider.

From www.youtube.com

How to make a clock divider CMOS logic gates and counters Dive into How To Make A Clock Divider The frequency of the output. A simple clock divider circuit combines combinational and clocked digital logic. This is the simplest clock divider you can implement into an fpga or asic. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. What the above code does is simply that it creates a vhdl. How To Make A Clock Divider.

From www.youtube.com

Step by Step Method to design any Clock Frequency Divider Part2 YouTube How To Make A Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The frequency of the output. The verilog clock divider is simulated and verified on fpga. In this section, we can use a. How To Make A Clock Divider.

From www.youtube.com

Integral Clock Divider Demo 1 YouTube How To Make A Clock Divider What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. The frequency of the output. In this section, we can use a counter. How To Make A Clock Divider.

From www.youtube.com

Using A Clock Divider In A Different Way YouTube How To Make A Clock Divider Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The frequency of the output. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. A simple clock divider circuit combines combinational and clocked digital. How To Make A Clock Divider.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL How To Make A Clock Divider In this section, we can use a counter with a comparator to. This is the simplest clock divider you can implement into an fpga or asic. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which divides the input clock frequency. How To Make A Clock Divider.

From dusty-clouds.com

CLOCK DIVIDER Dusty Clouds How To Make A Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. A simple clock divider circuit combines combinational and clocked digital logic. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The verilog clock divider is simulated and verified on fpga. In. How To Make A Clock Divider.

From blog.csdn.net

Clock divider_odd clock dividerCSDN博客 How To Make A Clock Divider A simple clock divider circuit combines combinational and clocked digital logic. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. What the above code does is simply that it creates a. How To Make A Clock Divider.

From digilent.com

Use Flipflops to Build a Clock Divider Digilent Reference How To Make A Clock Divider The frequency of the output. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This is the simplest clock divider you can implement into an fpga or asic. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up. How To Make A Clock Divider.

From www.davidhaillant.com

UC Clock Divider Electronic things… and stuff How To Make A Clock Divider The verilog clock divider is simulated and verified on fpga. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. In this section, we can use a counter with a comparator to. The frequency of the output. A simple clock divider circuit combines combinational and clocked digital logic. What the. How To Make A Clock Divider.

From synthnl.blogspot.com

Synth.nl Blog DIY Rotating Clock Divider How To Make A Clock Divider This is the simplest clock divider you can implement into an fpga or asic. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The. How To Make A Clock Divider.

From lookmumnocomputer.discourse.group

4017 clock divider DIY STUFF Look Mum No Computer Thingies How To Make A Clock Divider The verilog clock divider is simulated and verified on fpga. The frequency of the output. This is the simplest clock divider you can implement into an fpga or asic. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In our case let us take input frequency as 50mhz and divide the. How To Make A Clock Divider.

From www.youtube.com

Modular Tip Creative Uses for Clock Dividers! (ft. the Mazzatron Clock How To Make A Clock Divider The verilog clock divider is simulated and verified on fpga. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In this section, we can use a counter with a comparator to. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal.. How To Make A Clock Divider.

From www.youtube.com

Clock Divider Frequency Divider (D FlipFlop / Digital Latch) YouTube How To Make A Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. In this section, we can use a counter with a comparator to. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. A simple clock divider circuit combines combinational and clocked digital. How To Make A Clock Divider.

From lookmumnocomputer.discourse.group

Arduino Rotating Clock Divider KOSMO MODULES Look Mum No Computer How To Make A Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. In this section, we can use a counter with a comparator to. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. A simple clock. How To Make A Clock Divider.

From www.youtube.com

25 Verilog Clock Divider YouTube How To Make A Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. In this section, we can use a counter with a comparator to. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. A simple clock divider circuit combines combinational and clocked digital. How To Make A Clock Divider.

From www.youtube.com

Clock frequency divider circuit (divide by 2) using D flip flop YouTube How To Make A Clock Divider A simple clock divider circuit combines combinational and clocked digital logic. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. In our case let. How To Make A Clock Divider.

From www.youtube.com

Simple Clock Divider and a Sub Oscillator DIY Module in a Week 8.1 How To Make A Clock Divider The frequency of the output. This is the simplest clock divider you can implement into an fpga or asic. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. In this section, we can use a counter with a comparator to. In our. How To Make A Clock Divider.

From www.chegg.com

Design a Clock Divider circuit. You must show How To Make A Clock Divider What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. The frequency of the output. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In our case let us take input frequency as 50mhz. How To Make A Clock Divider.

From www.youtube.com

VHDL BASIC Tutorial Clock Divider YouTube How To Make A Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. A simple clock divider circuit combines combinational and clocked digital logic. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. This verilog project provides full verilog code for the clock divider. How To Make A Clock Divider.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL How To Make A Clock Divider A simple clock divider circuit combines combinational and clocked digital logic. The frequency of the output. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. In this section, we can use a counter with a comparator to. This verilog project provides full. How To Make A Clock Divider.

From www.slideshare.net

Clock divider by 3 How To Make A Clock Divider A simple clock divider circuit combines combinational and clocked digital logic. In this section, we can use a counter with a comparator to. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output. How To Make A Clock Divider.

From yusynth.net

CLOCK DIVIDER How To Make A Clock Divider This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This is the simplest clock divider you can implement into an fpga or asic. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. The. How To Make A Clock Divider.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL How To Make A Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. What the above code. How To Make A Clock Divider.

From kr.mathworks.com

Clock divider that divides frequency of input signal by fractional How To Make A Clock Divider In this section, we can use a counter with a comparator to. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. The frequency of the output. This is the simplest clock divider you can implement into an fpga or asic. The verilog. How To Make A Clock Divider.

From www.youtube.com

Step by Step Method to design any Clock Frequency Divider YouTube How To Make A Clock Divider The frequency of the output. This is the simplest clock divider you can implement into an fpga or asic. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. In our case let us take input frequency as 50mhz and divide the clock. How To Make A Clock Divider.

From www.youtube.com

Basic 4017 Clock Divider YouTube How To Make A Clock Divider In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted. How To Make A Clock Divider.

From sound-force.nl

Clocky Clock divider & multiplier SoundForce How To Make A Clock Divider What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. The verilog clock divider is simulated and verified on fpga. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. A simple clock divider circuit. How To Make A Clock Divider.

From mathpag.weebly.com

Clock divider vhdl mathpag How To Make A Clock Divider The frequency of the output. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. The verilog clock divider is simulated and verified on fpga. In our case let us take input frequency as. How To Make A Clock Divider.

From www.scribd.com

Clock Dividers Made Easy PDF Frequency Engineering How To Make A Clock Divider Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. A simple clock divider circuit combines combinational and clocked digital logic. This verilog project provides full verilog code for the clock divider on fpga together with testbench for simulation. This is the simplest clock divider you can implement into an fpga or. How To Make A Clock Divider.

From www.youtube.com

DIY EURORACK CLOCK DIVIDER&MULTIPLIER YouTube How To Make A Clock Divider What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. This is the simplest clock divider you can implement into an fpga or asic. The frequency of the output. This verilog project provides full verilog code for the clock divider on fpga together. How To Make A Clock Divider.

From www.youtube.com

VHDL Lecture 24 Lab 8 Clock Divider and Counters Explanation YouTube How To Make A Clock Divider Clock divider is also known as frequency divider, which divides the input clock frequency and produce output clock. What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. In our case let us take input frequency as 50mhz and divide the clock frequency. How To Make A Clock Divider.

From yusynth.net

CLOCK DIVIDER How To Make A Clock Divider What the above code does is simply that it creates a vhdl module containing a 24 bit counter q, which is counted up on each rising edge. A simple clock divider circuit combines combinational and clocked digital logic. The frequency of the output. This verilog project provides full verilog code for the clock divider on fpga together with testbench for. How To Make A Clock Divider.

From www.youtube.com

DIY clock divider YouTube How To Make A Clock Divider A simple clock divider circuit combines combinational and clocked digital logic. In our case let us take input frequency as 50mhz and divide the clock frequency to generate 1khz output signal. This is the simplest clock divider you can implement into an fpga or asic. This verilog project provides full verilog code for the clock divider on fpga together with. How To Make A Clock Divider.