Clock Gating Example . Dynamic power reduction by gating the clock. Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design.

from semiwiki.com

Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very.

The Role of Clock Gating SemiWiki

Clock Gating Example Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design.

From www.slideserve.com

PPT EE 587 SoC Design & Test PowerPoint Presentation, free download Clock Gating Example In this article, we’ll discuss the basic. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. Clock Gating Example.

From www.semanticscholar.org

A Review on Clock Gating Methodologies for power minimization in VLSI Clock Gating Example Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock Gating Example.

From slidetodoc.com

LowPower IC Design Gating Techniques TsungChu Huang Dept Clock Gating Example In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From www.researchgate.net

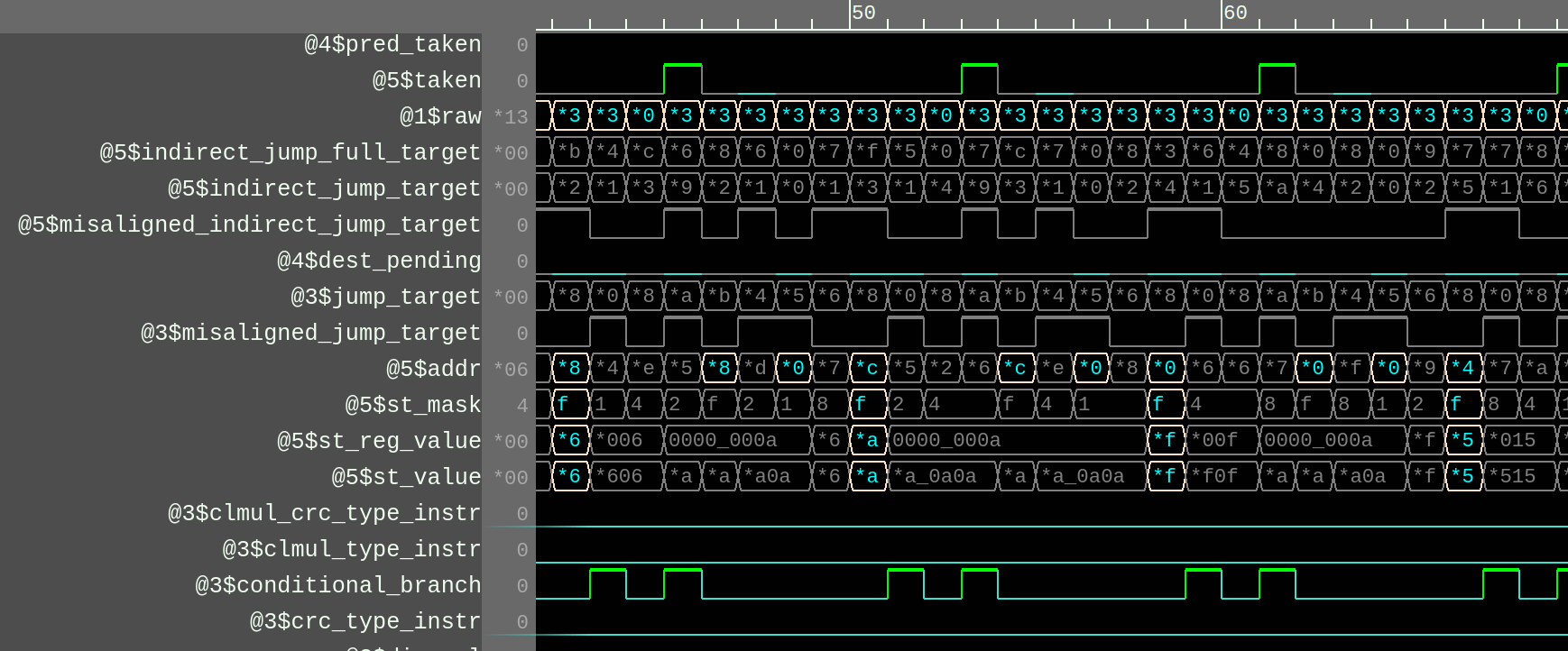

Example simulation trace of clock gating Download Scientific Diagram Clock Gating Example Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In most designs, data is loaded into registers very. Opportunities abound for saving power at different stages of design. Clock Gating Example.

From www.slideserve.com

PPT 32bit parallel load register with clock gating PowerPoint Clock Gating Example Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From www.researchgate.net

(PDF) Power Optimization Using Clock Gating and Power Gating A Review Clock Gating Example In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock Gating Example.

From www.youtube.com

Clock gating Example (Eda Playground), Verilog coding YouTube Clock Gating Example In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From slideplayer.com

Page 1 Department of Electrical Engineering National Chung Cheng Clock Gating Example Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Dynamic power reduction by gating the clock. Opportunities abound for saving power at different stages of design. Clock Gating Example.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation Clock Gating Example Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock Gating Example.

From www.researchgate.net

Multi level clock gating of a dataflow based reconfigurable system Clock Gating Example Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock Gating Example.

From www.myshared.ru

Презентация на тему "Logic and Computer Design Fundamentals Chapter 7 Clock Gating Example In most designs, data is loaded into registers very. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Clock Gating Example.

From www.slideserve.com

PPT Lecture 7 Power PowerPoint Presentation, free download ID4495903 Clock Gating Example Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. Dynamic power reduction by gating the clock. Clock Gating Example.

From www.youtube.com

Clock Gating Based Energy Efficient ALU Design and Implementation on Clock Gating Example Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In most designs, data is loaded into registers very. Dynamic power reduction by gating the clock. Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. Clock Gating Example.

From www.fpgakey.com

Clock gating FPGABased Prototyping Methodology FPGAkey Clock Gating Example Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Clock Gating Example.

From www.slideserve.com

PPT L17 Logic Level Design PowerPoint Presentation, free download Clock Gating Example In most designs, data is loaded into registers very. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From www.researchgate.net

3 Clock gating of the main clock to some component Download Clock Gating Example In most designs, data is loaded into registers very. Dynamic power reduction by gating the clock. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. Clock Gating Example.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Example In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Dynamic power reduction by gating the clock. Clock Gating Example.

From blogs.cuit.columbia.edu

Check clock gating Clock Gating Example Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock Gating Example.

From slideplayer.com

Efficient High Level Synthesis Algorithm for Lower Power Design ppt Clock Gating Example Dynamic power reduction by gating the clock. In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Clock Gating Example.

From www.cnblogs.com

Clock Gating Checks 小勇5 博客园 Clock Gating Example Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Dynamic power reduction by gating the clock. In most designs, data is loaded into registers very. Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. Clock Gating Example.

From www.researchgate.net

Fine grained clock gating. Download Scientific Diagram Clock Gating Example In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock Gating Example.

From www.linkedin.com

A video blog on latch based clock gating and integrated clock gate cell Clock Gating Example Dynamic power reduction by gating the clock. In most designs, data is loaded into registers very. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. Clock Gating Example.

From slideplayer.com

Overview Part 1 Registers, Microoperations and Implementations ppt Clock Gating Example Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In most designs, data is loaded into registers very. Clock Gating Example.

From community.cadence.com

How to resolve clock gating hold checks could not be fixed Clock Gating Example Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. Dynamic power reduction by gating the clock. In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From community.cadence.com

How to resolve clock gating hold checks could not be fixed Clock Gating Example In most designs, data is loaded into registers very. Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Example Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. In this article, we’ll discuss the basic. In most designs, data is loaded into registers very. Clock Gating Example.

From www.slideserve.com

PPT Low Power Design Methodologies and Flows PowerPoint Presentation Clock Gating Example In most designs, data is loaded into registers very. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. Clock Gating Example.

From semiengineering.com

Clock Gating Semiconductor Engineering Clock Gating Example Dynamic power reduction by gating the clock. Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From www.slideshare.net

Clock gating Clock Gating Example In most designs, data is loaded into registers very. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In this article, we’ll discuss the basic. Dynamic power reduction by gating the clock. Opportunities abound for saving power at different stages of design. Clock Gating Example.

From www.researchgate.net

Waveforms showing edge combinations due to DET clock gating and example Clock Gating Example In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Clock Gating Example.

From www.slideserve.com

PPT Viresh Paruthi, IBM Corporation J. Baumgartner, H. Mony, R. L Clock Gating Example In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Dynamic power reduction by gating the clock. Clock Gating Example.

From semiwiki.com

The Role of Clock Gating SemiWiki Clock Gating Example Dynamic power reduction by gating the clock. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Clock Gating Example.

From www.xilinx.com

AR 51737 Does XST support gated clock conversion? Clock Gating Example Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. In most designs, data is loaded into registers very. Dynamic power reduction by gating the clock. In this article, we’ll discuss the basic. Clock Gating Example.

From www.slideserve.com

PPT The clock PowerPoint Presentation, free download ID2403529 Clock Gating Example In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Opportunities abound for saving power at different stages of design. Dynamic power reduction by gating the clock. Clock Gating Example.

From www.slideshare.net

Clock gating Clock Gating Example Opportunities abound for saving power at different stages of design. Clock gating is one of the most frequently used techniques in rtl to reduce dynamic power consumption without affecting the functionality of the design. Dynamic power reduction by gating the clock. In most designs, data is loaded into registers very. In this article, we’ll discuss the basic. Clock Gating Example.