Transistor Sizing Examples . what we actually scale is the w. All other sizes are in reference to. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. Sizing of transistors to balance performance of single inverter. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. Reduce v dd, the frequency and the switched capacitance (dynamic). The nmos in a inverter of minimal size is defined as being of size 1. Let us understand the concept of transistor sizing with an example. transistor sizing a complex cmos g tcmos gate 1. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model.

from www.chegg.com

what we actually scale is the w. Sizing of transistors to balance performance of single inverter. All other sizes are in reference to. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Let us understand the concept of transistor sizing with an example. transistor sizing a complex cmos g tcmos gate 1. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. The nmos in a inverter of minimal size is defined as being of size 1. Reduce v dd, the frequency and the switched capacitance (dynamic).

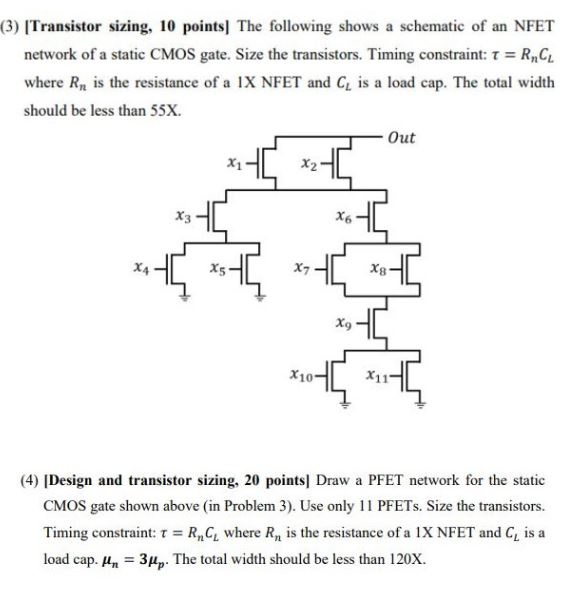

Solved (3) [Transistor sizing, 10 pointsl The following

Transistor Sizing Examples in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. what we actually scale is the w. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. The nmos in a inverter of minimal size is defined as being of size 1. Sizing of transistors to balance performance of single inverter. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. All other sizes are in reference to. transistor sizing a complex cmos g tcmos gate 1. Reduce v dd, the frequency and the switched capacitance (dynamic). Let us understand the concept of transistor sizing with an example.

From randomnerdtutorials.com

Electronics Basics How a Transistor Works Random Nerd Tutorials Transistor Sizing Examples Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. transistor sizing a complex cmos g tcmos gate 1. Let us understand the concept of transistor sizing with an example. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors.. Transistor Sizing Examples.

From dokumen.tips

(PDF) Transistor Sizing Logical Effort ece.cmu.eduece322/LECTURES Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. what we actually scale is the w. Sizing of transistors to balance. Transistor Sizing Examples.

From www.youtube.com

Electronics Sizing transistors for a CMOS circuit? YouTube Transistor Sizing Examples Reduce v dd, the frequency and the switched capacitance (dynamic). in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. what. Transistor Sizing Examples.

From www.slideserve.com

PPT Chapter 5 PowerPoint Presentation, free download ID6125537 Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. Reduce v dd, the frequency and the switched capacitance (dynamic). Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. what we actually scale is the w. Let us understand. Transistor Sizing Examples.

From www.semanticscholar.org

[PDF] Variations Aware Robust Transistor Sizing for PowerDelay Optimal Transistor Sizing Examples Reduce v dd, the frequency and the switched capacitance (dynamic). Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. transistor sizing a complex cmos g tcmos gate 1. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. Let. Transistor Sizing Examples.

From www.researchgate.net

Transistor sizing of NANDbased twobit multiplexer using LM Download Transistor Sizing Examples Reduce v dd, the frequency and the switched capacitance (dynamic). what we actually scale is the w. Let us understand the concept of transistor sizing with an example. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. transistor sizing a complex cmos g. Transistor Sizing Examples.

From electronics.stackexchange.com

Sizing transistors for a CMOS circuit? Electrical Engineering Stack Transistor Sizing Examples All other sizes are in reference to. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. what we actually scale is the w. transistor sizing a complex cmos g tcmos gate 1. Reduce v dd,. Transistor Sizing Examples.

From www.youtube.com

Transistor Sizing Static CMOS Design Know How YouTube Transistor Sizing Examples Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. The nmos in a inverter of minimal size is defined as being of size 1. Reduce v dd, the frequency and the switched capacitance (dynamic). Sizing of transistors to balance performance of single inverter. Start with. Transistor Sizing Examples.

From www.conrad.de

BC547 Transistor » Aufbau & Funktionsweise anschaulich erklärt Transistor Sizing Examples in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Let us understand the concept of transistor sizing with an example. Reduce v dd, the frequency and the switched capacitance (dynamic). transistor sizing a complex cmos g. Transistor Sizing Examples.

From www.researchgate.net

(a) Staticizer transistor sizing for correct functionality, and (b Transistor Sizing Examples Reduce v dd, the frequency and the switched capacitance (dynamic). Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. Sizing of transistors to balance performance of single inverter. All other sizes are in reference to. For a unit pmos transistor, the effective resistance with the. Transistor Sizing Examples.

From www.researchgate.net

2 Sizing result using the improved transistor circuit model. Download Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. what we actually scale is the w. transistor sizing a complex cmos g tcmos gate 1. Let us understand the concept of transistor sizing with an example. All other sizes are in reference to. Reduce v dd, the frequency and the switched capacitance. Transistor Sizing Examples.

From www.vlsiuniverse.com

VLSI UNIVERSE Transistor sizing W/L CMOS VLSI Transistor Sizing Examples Let us understand the concept of transistor sizing with an example. Sizing of transistors to balance performance of single inverter. Reduce v dd, the frequency and the switched capacitance (dynamic). Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. All other sizes are in reference to. For a unit pmos transistor, the effective resistance. Transistor Sizing Examples.

From theengineeringmindset.com

Transistor Explained How Transistors Work The Engineering Mindset Transistor Sizing Examples what we actually scale is the w. Sizing of transistors to balance performance of single inverter. Let us understand the concept of transistor sizing with an example. transistor sizing a complex cmos g tcmos gate 1. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. All other sizes are in reference to.. Transistor Sizing Examples.

From www.slideserve.com

PPT COMBINATIONAL LOGIC PowerPoint Presentation, free download ID Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. Let us understand the concept of transistor sizing with an example. All other sizes are in reference to. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. transistor sizing. Transistor Sizing Examples.

From builtin.com

What Is a Transistor? (Definition, How It Works, Example) Built In Transistor Sizing Examples Sizing of transistors to balance performance of single inverter. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. transistor sizing a complex cmos g tcmos gate 1. The nmos in a inverter of minimal size is defined as being of size 1. All other. Transistor Sizing Examples.

From www.youtube.com

Transistor Sizing YouTube Transistor Sizing Examples transistor sizing a complex cmos g tcmos gate 1. Reduce v dd, the frequency and the switched capacitance (dynamic). Sizing of transistors to balance performance of single inverter. The nmos in a inverter of minimal size is defined as being of size 1. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. . Transistor Sizing Examples.

From www.youtube.com

How to do transistor sizing for static CMOS CircuitEasy method YouTube Transistor Sizing Examples in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Reduce v dd, the frequency and the switched capacitance (dynamic). For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. Let us. Transistor Sizing Examples.

From www.slideserve.com

PPT Digital CMOS Logic Circuits PowerPoint Presentation, free Transistor Sizing Examples All other sizes are in reference to. transistor sizing a complex cmos g tcmos gate 1. Let us understand the concept of transistor sizing with an example. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. Given the logic function y = a ( b + c ) + d e and asked. Transistor Sizing Examples.

From learn.sparkfun.com

Transistors SparkFun Learn Transistor Sizing Examples Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Let us understand the. Transistor Sizing Examples.

From www.slideserve.com

PPT Designing Static CMOS Logic Circuits PowerPoint Presentation Transistor Sizing Examples in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. Start with a transistor. Transistor Sizing Examples.

From www.scribd.com

Transistor Sizing TSPC and C2MOS Electronic Design Transistor Sizing Examples Sizing of transistors to balance performance of single inverter. Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. All other sizes are in reference to. Reduce v dd, the frequency and the switched capacitance (dynamic). The nmos in a inverter of minimal size is defined as being of size 1. in this article,. Transistor Sizing Examples.

From itecnotes.com

Electrical Sizing transistors for a CMOS circuit Valuable Tech Notes Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. transistor sizing a complex cmos g tcmos gate 1. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Let us understand. Transistor Sizing Examples.

From www.chegg.com

Solved 5. 10.34 (Transistor Sizing) Find appropriate sizes Transistor Sizing Examples All other sizes are in reference to. The nmos in a inverter of minimal size is defined as being of size 1. what we actually scale is the w. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. Start with a transistor in the. Transistor Sizing Examples.

From www.vlsiuniverse.com

Transistor sizing W/L CMOS VLSI VLSI UNIVERSE Transistor Sizing Examples Let us understand the concept of transistor sizing with an example. Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. The nmos in a inverter of minimal size is defined as being of size 1. Start with a transistor in the pdn, that is (preferably). Transistor Sizing Examples.

From www.chegg.com

Solved Example Transistor sizing ratio PMOSNMOS=51.5 a) Transistor Sizing Examples Let us understand the concept of transistor sizing with an example. Sizing of transistors to balance performance of single inverter. what we actually scale is the w. Reduce v dd, the frequency and the switched capacitance (dynamic). Given the logic function y = a ( b + c ) + d e and asked to size the pmos and. Transistor Sizing Examples.

From www.chegg.com

Solved (3) [Transistor sizing, 10 pointsl The following Transistor Sizing Examples what we actually scale is the w. All other sizes are in reference to. Sizing of transistors to balance performance of single inverter. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. transistor sizing a complex cmos g tcmos gate 1. in this article, we will learn how to find. Transistor Sizing Examples.

From siliconvlsi.com

Transistor Sizing Siliconvlsi Transistor Sizing Examples Reduce v dd, the frequency and the switched capacitance (dynamic). in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Sizing of transistors to balance performance of single inverter. All other sizes are in reference to. For a. Transistor Sizing Examples.

From www.researchgate.net

Summary of Op Amp Transistor Sizing Transistor g m /I D (S/A) Number of Transistor Sizing Examples Sizing of transistors to balance performance of single inverter. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Start with a. Transistor Sizing Examples.

From www.build-electronic-circuits.com

PNP Transistor How Does It Work? Transistor Sizing Examples For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. Reduce v dd, the frequency and the switched capacitance (dynamic). what we actually scale is the w. transistor sizing a complex cmos g tcmos gate 1. Let us understand the concept of transistor sizing with an example. The nmos in a inverter. Transistor Sizing Examples.

From www.researchgate.net

Transistor sizing and layout for the 6T SRAM cell. Download Transistor Sizing Examples what we actually scale is the w. All other sizes are in reference to. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the. Transistor Sizing Examples.

From www.youtube.com

CMOS Logic Design Transistor Sizing YouTube Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. Reduce v dd, the frequency and the switched capacitance (dynamic). what we actually scale is the w. transistor sizing a complex cmos g tcmos gate 1. Sizing of transistors to balance performance of single inverter. Start with a transistor in the pdn, that. Transistor Sizing Examples.

From www.slideserve.com

PPT Review CMOS Inverter Dynamic PowerPoint Presentation, free Transistor Sizing Examples Given the logic function y = a ( b + c ) + d e and asked to size the pmos and nmos transistors. transistor sizing a complex cmos g tcmos gate 1. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired. Transistor Sizing Examples.

From studiousguy.com

18 Transistor Examples in Daily Life StudiousGuy Transistor Sizing Examples Start with a transistor in the pdn, that is (preferably) isolated (i.e., it can pull. All other sizes are in reference to. Sizing of transistors to balance performance of single inverter. transistor sizing a complex cmos g tcmos gate 1. in this article, we will learn how to find the optimal size of a transistor/logic gate present in. Transistor Sizing Examples.

From www.researchgate.net

Transistor sizing concept in a threedimensional spaces [6]. Download Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. Sizing of transistors to balance performance of single inverter. For a unit pmos transistor, the effective resistance with the width k is given by 2r/k. what we actually scale is the w. in this article, we will learn how to find the optimal. Transistor Sizing Examples.

From www.chegg.com

Solved Question 3) CMOS gate transistor sizing 130 POINTSI Transistor Sizing Examples The nmos in a inverter of minimal size is defined as being of size 1. what we actually scale is the w. in this article, we will learn how to find the optimal size of a transistor/logic gate present in a larger circuit to provide the desired performance using the linear delay model. Given the logic function y. Transistor Sizing Examples.