Quartus Clock Assignment . Customers should click here to go to the newest version. With this method, you can manually constrain the input clock and output clocks of the pll. If you like your clk_4_77mhz (i.e. The clock assignment properties pane displays properties of the selected clock assignment. All pll parameters are specified and parameter values. It is more descriptive), eliminate the clk4_del2 and replace the assignment: By default, the clock assignment properties pane. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. A newer version of this document is available. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. Creating clocks and clock constraints.

from edg.uchicago.edu

The clock assignment properties pane displays properties of the selected clock assignment. It is more descriptive), eliminate the clk4_del2 and replace the assignment: クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. If you like your clk_4_77mhz (i.e. A newer version of this document is available. Creating clocks and clock constraints. With this method, you can manually constrain the input clock and output clocks of the pll. All pll parameters are specified and parameter values. Customers should click here to go to the newest version.

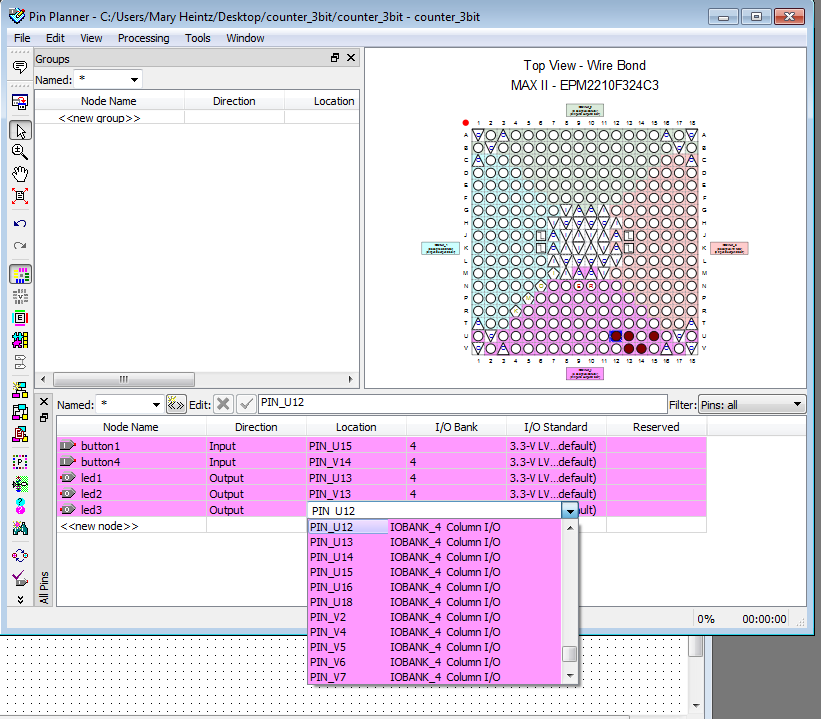

Quartus/Modelsim Tutorial

Quartus Clock Assignment Creating clocks and clock constraints. By default, the clock assignment properties pane. It is more descriptive), eliminate the clk4_del2 and replace the assignment: All pll parameters are specified and parameter values. Customers should click here to go to the newest version. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. If you like your clk_4_77mhz (i.e. Creating clocks and clock constraints. A newer version of this document is available. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. With this method, you can manually constrain the input clock and output clocks of the pll. The clock assignment properties pane displays properties of the selected clock assignment.

From www.pianshen.com

Quartus 12小时时钟(同步) 程序员大本营 Quartus Clock Assignment Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. All pll parameters are specified and parameter values. By default, the clock assignment properties pane. Creating clocks and clock constraints. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Customers should click here to go to the newest version. With this method, you can. Quartus Clock Assignment.

From www.youtube.com

Quartus II для начинающих. Урок 2. YouTube Quartus Clock Assignment If you like your clk_4_77mhz (i.e. Creating clocks and clock constraints. Customers should click here to go to the newest version. The clock assignment properties pane displays properties of the selected clock assignment. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. A newer version of this document is available. It is more descriptive), eliminate the clk4_del2 and replace the assignment:. Quartus Clock Assignment.

From www.etsy.com

QUARTUS Wooden Clock Kit Etsy Quartus Clock Assignment Creating clocks and clock constraints. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. With this method, you can manually constrain the input clock and output clocks of the pll. A newer version of this document is available. Customers should click here to go to the newest version. If you like your clk_4_77mhz (i.e. All pll parameters are specified and parameter values. The. Quartus Clock Assignment.

From www.chegg.com

Solved *I'm Building This Circuit On Altera Quartus*.... Quartus Clock Assignment With this method, you can manually constrain the input clock and output clocks of the pll. A newer version of this document is available. All pll parameters are specified and parameter values. The clock assignment properties pane displays properties of the selected clock assignment. By default, the clock assignment properties pane. Creating clocks and clock constraints. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus®. Quartus Clock Assignment.

From itecnotes.com

Electronic Quartus II selected a signal as a clock in combinational Quartus Clock Assignment A newer version of this document is available. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. Creating clocks and clock constraints. It is more descriptive), eliminate the clk4_del2 and replace the assignment: With this method, you can manually constrain the input clock and output clocks of the pll. The clock assignment properties pane displays properties of the selected clock assignment. All pll. Quartus Clock Assignment.

From www.youtube.com

Uso de conexiones en bus en Quartus II YouTube Quartus Clock Assignment A newer version of this document is available. By default, the clock assignment properties pane. With this method, you can manually constrain the input clock and output clocks of the pll. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. If you like your clk_4_77mhz (i.e. Customers should click here to go to the newest version. The clock assignment properties pane. Quartus Clock Assignment.

From www.chegg.com

Solved Design clock with Alarm project using Quartus 13.1. Quartus Clock Assignment A newer version of this document is available. Creating clocks and clock constraints. By default, the clock assignment properties pane. If you like your clk_4_77mhz (i.e. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. With this method, you can manually constrain the input clock and output clocks of the pll. It is more descriptive), eliminate the clk4_del2 and replace the assignment: All. Quartus Clock Assignment.

From triptonkosti.ru

Как создать проект в quartus 84 фото Quartus Clock Assignment Creating clocks and clock constraints. With this method, you can manually constrain the input clock and output clocks of the pll. It is more descriptive), eliminate the clk4_del2 and replace the assignment: If you like your clk_4_77mhz (i.e. The clock assignment properties pane displays properties of the selected clock assignment. All pll parameters are specified and parameter values. By default,. Quartus Clock Assignment.

From edg.uchicago.edu

Quartus/Modelsim Tutorial Quartus Clock Assignment A newer version of this document is available. Creating clocks and clock constraints. With this method, you can manually constrain the input clock and output clocks of the pll. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. Customers should click here to go to the newest version. The clock. Quartus Clock Assignment.

From www.chegg.com

Solved I want to solve this assignment using quartus program Quartus Clock Assignment Customers should click here to go to the newest version. By default, the clock assignment properties pane. With this method, you can manually constrain the input clock and output clocks of the pll. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. Creating clocks and clock constraints. The clock assignment properties pane displays properties of the selected clock assignment. A newer version of. Quartus Clock Assignment.

From www.numerade.com

SOLVED Please design the block diagram in Quartus software. Assignment Quartus Clock Assignment If you like your clk_4_77mhz (i.e. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. With this method, you can manually constrain the input clock and output clocks of the pll. The clock assignment properties pane displays properties of the selected clock assignment. Customers should click here to go to the newest version. It is more descriptive), eliminate the clk4_del2 and. Quartus Clock Assignment.

From jentaplerdesigns.blogspot.com

Quartu 2 Block Diagram Tutorial jentaplerdesigns Quartus Clock Assignment It is more descriptive), eliminate the clk4_del2 and replace the assignment: All pll parameters are specified and parameter values. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. A newer version of this document is available. Customers should click here to go to the newest version. With this method, you can manually constrain the input clock and output clocks of the pll. Creating. Quartus Clock Assignment.

From electronics.stackexchange.com

verilog Need some help with my Quartus code since it is not showing Quartus Clock Assignment The clock assignment properties pane displays properties of the selected clock assignment. With this method, you can manually constrain the input clock and output clocks of the pll. It is more descriptive), eliminate the clk4_del2 and replace the assignment: クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. If you like your clk_4_77mhz (i.e. Customers should click here to go to the newest. Quartus Clock Assignment.

From stackoverflow.com

verilog Capturing the right posedge clock in Quartus waveform Stack Quartus Clock Assignment Customers should click here to go to the newest version. With this method, you can manually constrain the input clock and output clocks of the pll. A newer version of this document is available. All pll parameters are specified and parameter values. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. It is more descriptive), eliminate the clk4_del2 and replace the. Quartus Clock Assignment.

From sagara-works.jp

シミュレーション クロック波形入力の使い方 Quartusを使った自作CPUの作り方 相楽製作所 Quartus Clock Assignment Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. All pll parameters are specified and parameter values. By default, the clock assignment properties pane. It is more descriptive), eliminate the clk4_del2 and replace the assignment: クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. If you like your clk_4_77mhz (i.e. A newer version of this document is available. Creating clocks and clock constraints. The. Quartus Clock Assignment.

From electronics.stackexchange.com

Quartus II Memory Read Clock Problem Electrical Engineering Stack Quartus Clock Assignment All pll parameters are specified and parameter values. Creating clocks and clock constraints. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. If you like your clk_4_77mhz (i.e. With this method, you can manually constrain the input clock and output clocks of the pll. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の.. Quartus Clock Assignment.

From www.youtube.com

Creating Block/Symbol Files in Quartus II YouTube Quartus Clock Assignment Customers should click here to go to the newest version. Creating clocks and clock constraints. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. A newer version of this document is available. If you like your clk_4_77mhz (i.e. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. The clock assignment properties pane displays properties of the selected clock assignment. With this method, you can. Quartus Clock Assignment.

From www.mikrocontroller.net

Quartus Node was determined to be a clock but was found without an Quartus Clock Assignment All pll parameters are specified and parameter values. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. Customers should click here to go to the newest version. By default, the clock assignment properties pane. With this method, you can manually constrain the input clock and output clocks of the pll. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. A newer version of this. Quartus Clock Assignment.

From edg.uchicago.edu

Quartus/Modelsim Tutorial Quartus Clock Assignment クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. The clock assignment properties pane displays properties of the selected clock assignment. All pll parameters are specified and parameter values. Creating clocks and clock constraints. If you like your clk_4_77mhz (i.e. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Customers should click here to go to the newest version. With this. Quartus Clock Assignment.

From electronix.ru

Quartus Assignment Editor Работаем с ПЛИС, области применения, выбор Quartus Clock Assignment クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Customers should click here to go to the newest version. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. All pll parameters are specified and parameter values. With this method, you can manually constrain the input clock and output clocks of the pll. The. Quartus Clock Assignment.

From www.youtube.com

FPGA first steps in Quartus II (Altera) YouTube Quartus Clock Assignment Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. The clock assignment properties pane displays properties of the selected clock assignment. A newer version of this document is available. All pll parameters are specified and parameter values. Creating clocks and clock constraints. Customers should click here to go to the newest version. It is more descriptive), eliminate the clk4_del2 and replace. Quartus Clock Assignment.

From www.youtube.com

Simulation in Quartus II v15.0 YouTube Quartus Clock Assignment All pll parameters are specified and parameter values. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. With this method, you can manually constrain the input clock and output clocks of the pll. The clock assignment properties pane displays properties of the selected clock assignment. It is more descriptive), eliminate the clk4_del2 and replace the assignment: A newer version of this document is. Quartus Clock Assignment.

From felixstraykidslineartdrawing.blogspot.com

quartus no clocks defined in design felixstraykidslineartdrawing Quartus Clock Assignment It is more descriptive), eliminate the clk4_del2 and replace the assignment: If you like your clk_4_77mhz (i.e. A newer version of this document is available. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. By default, the clock assignment properties pane. Customers should click here to go to the newest version. The clock assignment properties pane displays properties of the selected. Quartus Clock Assignment.

From electronica.guru

¿Cómo asignar clock / reset a sram en Quartus? Electronica Quartus Clock Assignment With this method, you can manually constrain the input clock and output clocks of the pll. A newer version of this document is available. Creating clocks and clock constraints. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. By default, the clock assignment properties pane. If you like your clk_4_77mhz (i.e. Customers should click here. Quartus Clock Assignment.

From stackoverflow.com

Quartus isn't displaying Correctly Stack Overflow Quartus Clock Assignment With this method, you can manually constrain the input clock and output clocks of the pll. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. A newer version of this document is available. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Creating clocks and clock constraints. By default, the clock assignment properties. Quartus Clock Assignment.

From cseweb.ucsd.edu

CSE140L Fa10 Lab 2 Part 0 Quartus Clock Assignment クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. With this method, you can manually constrain the input clock and output clocks of the pll. Creating clocks and clock constraints. Customers should click here to go to the newest version. It is more descriptive), eliminate the clk4_del2 and replace the assignment: The clock assignment properties pane displays properties of the selected clock assignment.. Quartus Clock Assignment.

From www.youtube.com

Intel® Quartus® Prime Pro Software Timing Analysis Part 3 Clock Quartus Clock Assignment If you like your clk_4_77mhz (i.e. The clock assignment properties pane displays properties of the selected clock assignment. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. All pll parameters are specified and parameter values. It is more descriptive), eliminate the clk4_del2 and replace the assignment: A newer version of this document is available. Creating clocks and clock constraints. Customers should. Quartus Clock Assignment.

From www.youtube.com

DE1 Onboard Clock using Frequency Division in Quartus YouTube Quartus Clock Assignment All pll parameters are specified and parameter values. Creating clocks and clock constraints. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. By default, the clock assignment properties pane. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. The clock assignment properties pane displays properties of the selected clock assignment. If you like your clk_4_77mhz (i.e. A newer version of this document is available.. Quartus Clock Assignment.

From www.youtube.com

Digital Clock in Quartus YouTube Quartus Clock Assignment With this method, you can manually constrain the input clock and output clocks of the pll. It is more descriptive), eliminate the clk4_del2 and replace the assignment: The clock assignment properties pane displays properties of the selected clock assignment. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. By default, the clock assignment properties pane. Customers should click here to go. Quartus Clock Assignment.

From www.youtube.com

Adding System Clock Timer To Qsys and Quartus II YouTube Quartus Clock Assignment A newer version of this document is available. It is more descriptive), eliminate the clk4_del2 and replace the assignment: クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. The clock assignment properties pane displays properties of the selected clock assignment. Creating clocks and clock constraints. With this method, you can manually constrain the input clock. Quartus Clock Assignment.

From www.youtube.com

Pin Assignment Solution for Quartus II YouTube Quartus Clock Assignment Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. All pll parameters are specified and parameter values. Creating clocks and clock constraints. The clock assignment properties pane displays properties of the selected clock assignment. With this method, you can manually constrain the input clock and output clocks of the pll. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. If you like your clk_4_77mhz. Quartus Clock Assignment.

From denethor.wlu.ca

Introduction to Quartus II Software (using QSim for Simulation) Quartus Clock Assignment Customers should click here to go to the newest version. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. With this method, you can manually constrain the input clock and output clocks of the pll. If you like your clk_4_77mhz (i.e. A newer version of this document is available. Creating clocks and clock constraints. All pll parameters are specified and parameter values. It. Quartus Clock Assignment.

From www.numerade.com

SOLVED In Quartus The objective of this assignment is to design a Quartus Clock Assignment Creating clocks and clock constraints. Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. A newer version of this document is available. All pll parameters are specified and parameter values. It is more descriptive), eliminate the clk4_del2 and replace the assignment: The clock assignment properties pane displays properties of the selected clock assignment. With this method, you can manually constrain the. Quartus Clock Assignment.

From vita-brevis.hatenablog.com

Quartus Ⅱでclock周波数を与える方法 働きたくない Quartus Clock Assignment With this method, you can manually constrain the input clock and output clocks of the pll. Customers should click here to go to the newest version. A newer version of this document is available. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. Creating clocks and clock constraints. By default, the clock assignment properties pane. It is more descriptive), eliminate the clk4_del2 and. Quartus Clock Assignment.

From www.youtube.com

VHDL Assignment (Digital Clock with Alarm) YouTube Quartus Clock Assignment Creating clocks and clock constraints. クロック入力をこれらの専用クロック・ピンの1 本に割り当てるか、 インテル® quartus® prime 割り当てを使用してグローバル配線を割り当てることによ. A newer version of this document is available. If you like your clk_4_77mhz (i.e. It is more descriptive), eliminate the clk4_del2 and replace the assignment: Synopsys* design constraint (sdc) コマンド create_generated_clock を使用して、任意の数と深さの派生クロックを作成できます。 これは下記の. Customers should click here to go to the newest version. All pll parameters are specified and. Quartus Clock Assignment.