Brackets In Verilog . Means zero or more repetitions of the. It should be mentioned that these. Verilog is a hardware description language that is used to realize the digital circuits through code. What do the numbers in the square brackets represent? The verilog syntax description in this reference manual uses the following grammar: Syntax enclosed in square brackets [ ] is optional. Most verilog operators will operate on both busses and simple nets. Verilog hdl is commonly used. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. The verilog concatenate operator is the open and close brackets {, }. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Busses are defined by putting a range in square.

from www.slideserve.com

The verilog syntax description in this reference manual uses the following grammar: Most verilog operators will operate on both busses and simple nets. Verilog hdl is commonly used. Busses are defined by putting a range in square. The verilog concatenate operator is the open and close brackets {, }. Means zero or more repetitions of the. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. Verilog is a hardware description language that is used to realize the digital circuits through code. What do the numbers in the square brackets represent? The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right.

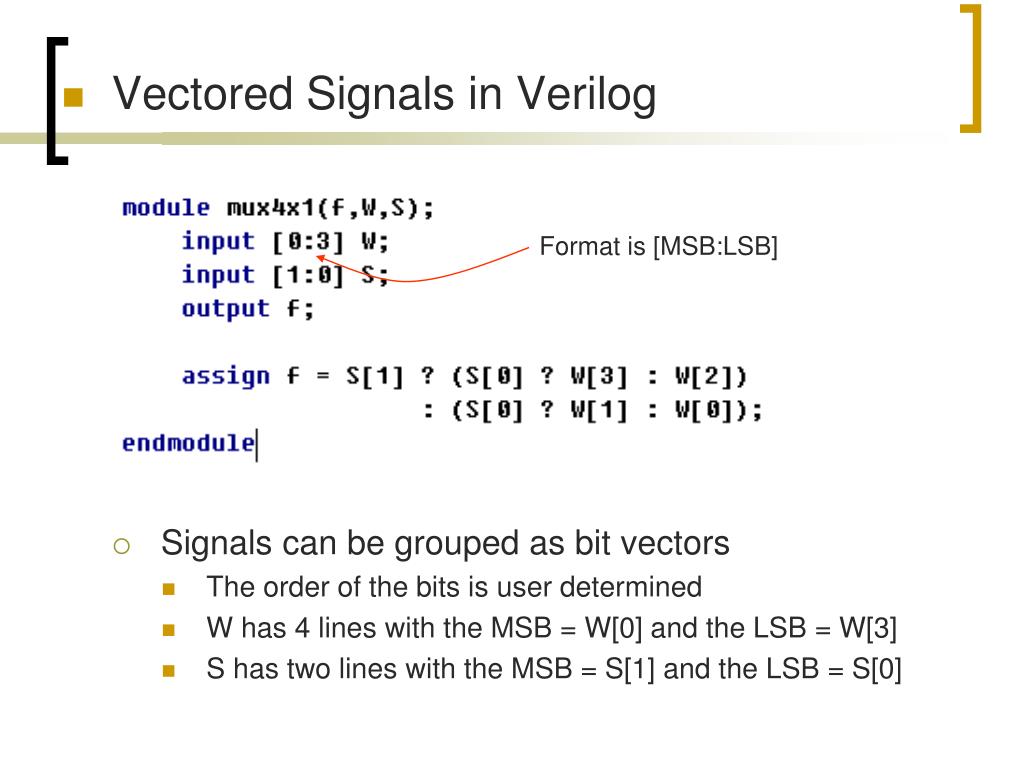

PPT Combinational Logic in Verilog PowerPoint Presentation, free

Brackets In Verilog Most verilog operators will operate on both busses and simple nets. Verilog hdl is commonly used. The verilog syntax description in this reference manual uses the following grammar: I'm a vhdl guy, but typically brackets and parentheses indicate reference to. The verilog concatenate operator is the open and close brackets {, }. Means zero or more repetitions of the. Verilog is a hardware description language that is used to realize the digital circuits through code. What do the numbers in the square brackets represent? Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). It should be mentioned that these. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Busses are defined by putting a range in square. Most verilog operators will operate on both busses and simple nets. Syntax enclosed in square brackets [ ] is optional. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register.

From www.youtube.com

GATE LEVEL MODELLING 2 Design and verify half subtractor using Brackets In Verilog The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Verilog hdl is commonly used. Verilog is a hardware description language that is used to realize the digital circuits through code.. Brackets In Verilog.

From www.chegg.com

Solved Write a Verilog code for the following expression Brackets In Verilog The verilog concatenate operator is the open and close brackets {, }. Most verilog operators will operate on both busses and simple nets. Verilog hdl is commonly used. Busses are defined by putting a range in square. It should be mentioned that these. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written. Brackets In Verilog.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5198890 Brackets In Verilog The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. The verilog concatenate operator is the open and close brackets {, }. What do the numbers in the square brackets represent? Busses are defined by putting a range in square. Most verilog operators will operate on both. Brackets In Verilog.

From github.com

verilog · Issue 7 · tejasvi/rainbowbrackets2 · GitHub Brackets In Verilog Syntax enclosed in square brackets [ ] is optional. It should be mentioned that these. Verilog is a hardware description language that is used to realize the digital circuits through code. What do the numbers in the square brackets represent? The verilog syntax description in this reference manual uses the following grammar: This brochure describes the common verilog language syntax. Brackets In Verilog.

From link.springer.com

Verilog Constructs SpringerLink Brackets In Verilog Most verilog operators will operate on both busses and simple nets. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Busses are defined by putting a range in square. Means zero or more repetitions of the. The verilog concatenate operator is the open and close brackets {, }. The verilog syntax description in. Brackets In Verilog.

From www.youtube.com

An Example Verilog Test Bench YouTube Brackets In Verilog It should be mentioned that these. Means zero or more repetitions of the. Verilog hdl is commonly used. The verilog concatenate operator is the open and close brackets {, }. What do the numbers in the square brackets represent? Busses are defined by putting a range in square. Verilog is a hardware description language that is used to realize the. Brackets In Verilog.

From www.chegg.com

Solved Write the Verilog code for the following circuit, use Brackets In Verilog This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Busses are defined by putting. Brackets In Verilog.

From www.youtube.com

verilog code for 4x1 mux using 2x1 with testbench YouTube Brackets In Verilog The verilog syntax description in this reference manual uses the following grammar: This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Most verilog operators will operate on both busses and simple nets. The. Brackets In Verilog.

From louis-dr.github.io

Louis DuretRobert Brackets In Verilog It should be mentioned that these. Verilog hdl is commonly used. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). The curly braces mean concatenation, from most significant bit (msb) on the left. Brackets In Verilog.

From www.youtube.com

Verilog Concatenation YouTube Brackets In Verilog It should be mentioned that these. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. The verilog concatenate operator is the open and close brackets {,. Brackets In Verilog.

From userdiagrammeyer.z19.web.core.windows.net

Logical Operators In Verilog Brackets In Verilog Most verilog operators will operate on both busses and simple nets. Means zero or more repetitions of the. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the. Brackets In Verilog.

From mungfali.com

Verilog Structural Model Brackets In Verilog The verilog syntax description in this reference manual uses the following grammar: Syntax enclosed in square brackets [ ] is optional. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. What do the numbers in the square brackets represent? The verilog concatenate operator is the open and close brackets. Brackets In Verilog.

From courses.cs.washington.edu

Verilog Data Types and Values Brackets In Verilog Means zero or more repetitions of the. What do the numbers in the square brackets represent? Verilog hdl is commonly used. Most verilog operators will operate on both busses and simple nets. Syntax enclosed in square brackets [ ] is optional. It should be mentioned that these. The curly braces mean concatenation, from most significant bit (msb) on the left. Brackets In Verilog.

From www.youtube.com

Electronics What do square brackets represent in verilog? (2 Solutions Brackets In Verilog Means zero or more repetitions of the. Busses are defined by putting a range in square. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. Verilog is a hardware description language that is used to realize the digital circuits through code. The curly braces mean concatenation, from most significant bit (msb) on the left down to the. Brackets In Verilog.

From siytek.com

How To Use Verilog In Quartus (Easy FPGA StepByStep Guide) Siytek Brackets In Verilog Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Verilog is a hardware description language that is used to realize the digital circuits through code. Syntax enclosed in square brackets [ ] is optional. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the. Brackets In Verilog.

From www.chipverify.com

Verilog Module Instantiations Brackets In Verilog Verilog is a hardware description language that is used to realize the digital circuits through code. Syntax enclosed in square brackets [ ] is optional. The verilog concatenate operator is the open and close brackets {, }. What do the numbers in the square brackets represent? Busses are defined by putting a range in square. This brochure describes the common. Brackets In Verilog.

From www.youtube.com

System Verilog tutorial Combinational logic design coding AND OR Brackets In Verilog This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. Verilog hdl is commonly used. The verilog concatenate operator is the open and close brackets {, }. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). What do the numbers in the square. Brackets In Verilog.

From mavink.com

Shift Register Verilog Brackets In Verilog Verilog is a hardware description language that is used to realize the digital circuits through code. The verilog syntax description in this reference manual uses the following grammar: What do the numbers in the square brackets represent? Verilog hdl is commonly used. The verilog concatenate operator is the open and close brackets {, }. I'm a vhdl guy, but typically. Brackets In Verilog.

From www.youtube.com

Adder Using Concatenation in Verilog YouTube Brackets In Verilog Busses are defined by putting a range in square. Means zero or more repetitions of the. The verilog concatenate operator is the open and close brackets {, }. What do the numbers in the square brackets represent? It should be mentioned that these. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written. Brackets In Verilog.

From slideplayer.com

Week 5, Verilog & Full Adder ppt download Brackets In Verilog Means zero or more repetitions of the. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. Syntax enclosed in square brackets [ ] is optional. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Most. Brackets In Verilog.

From guillermokruwhorn.blogspot.com

Data Flow Modelling in Verilog GuillermokruwHorn Brackets In Verilog Syntax enclosed in square brackets [ ] is optional. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. It should be mentioned that these. I'm a vhdl guy, but typically. Brackets In Verilog.

From www.youtube.com

Electronics Verilog negative value in brackets of vector signal Brackets In Verilog The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Syntax enclosed in square brackets [ ] is optional. Means zero or more repetitions of the. Busses are defined by putting. Brackets In Verilog.

From www.vrogue.co

Verilog Coding Verilog Code For 2 To 4 Line Decoder vrogue.co Brackets In Verilog Verilog hdl is commonly used. It should be mentioned that these. Verilog is a hardware description language that is used to realize the digital circuits through code. Means zero or more repetitions of the. The verilog concatenate operator is the open and close brackets {, }. What do the numbers in the square brackets represent? Brackets [] are part of. Brackets In Verilog.

From startnaxre.weebly.com

44 multiplier verilog code startnaxre Brackets In Verilog The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). The verilog syntax description in this reference manual uses the following grammar: Most verilog operators will operate on both busses and. Brackets In Verilog.

From www.chegg.com

Using Verilog and the shift operator, design an Nbit Brackets In Verilog What do the numbers in the square brackets represent? I'm a vhdl guy, but typically brackets and parentheses indicate reference to. The verilog concatenate operator is the open and close brackets {, }. Syntax enclosed in square brackets [ ] is optional. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant. Brackets In Verilog.

From wikidocs.net

01. Verilog Syntax. Xilinx FPGA 강좌. Brackets In Verilog Most verilog operators will operate on both busses and simple nets. Verilog hdl is commonly used. Busses are defined by putting a range in square. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). The verilog concatenate operator is the open and close brackets {, }. It should be mentioned that these. The. Brackets In Verilog.

From courses.cs.washington.edu

Verilog Continuous Assignment Brackets In Verilog It should be mentioned that these. Means zero or more repetitions of the. Busses are defined by putting a range in square. The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Verilog hdl is commonly used. Syntax enclosed in square brackets [ ] is optional. What. Brackets In Verilog.

From github.com

GitHub ctangel/bracketsverilog Brackets In Verilog Busses are defined by putting a range in square. Means zero or more repetitions of the. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. What do the numbers in the square brackets represent? Verilog hdl is commonly used. I'm a vhdl guy, but typically brackets and parentheses indicate. Brackets In Verilog.

From www.windward.solutions

Verilog tutorial youtube Brackets In Verilog Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Busses are defined by putting a range in square. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. What do the numbers in the square brackets represent? Means zero or more repetitions of the. The curly braces mean concatenation, from most. Brackets In Verilog.

From www.slideshare.net

Crash course in verilog Brackets In Verilog Verilog hdl is commonly used. Verilog is a hardware description language that is used to realize the digital circuits through code. This brochure describes the common verilog language syntax supported by the cadence tools that accept models written at the register. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Most verilog operators. Brackets In Verilog.

From electronics.stackexchange.com

Verilog 8 Bit ALU Electrical Engineering Stack Exchange Brackets In Verilog Means zero or more repetitions of the. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. Syntax enclosed in square brackets [ ] is optional. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). Verilog is a hardware description language that is used to realize the digital circuits through code.. Brackets In Verilog.

From www.youtube.com

Function syntax in Verilog(41 mux implementation using 21 mux) YouTube Brackets In Verilog Busses are defined by putting a range in square. Syntax enclosed in square brackets [ ] is optional. Most verilog operators will operate on both busses and simple nets. The verilog concatenate operator is the open and close brackets {, }. Verilog is a hardware description language that is used to realize the digital circuits through code. What do the. Brackets In Verilog.

From digilent.com

Verilog® HDL Project 1 Digilent Reference Brackets In Verilog The verilog concatenate operator is the open and close brackets {, }. Syntax enclosed in square brackets [ ] is optional. The verilog syntax description in this reference manual uses the following grammar: I'm a vhdl guy, but typically brackets and parentheses indicate reference to. Verilog hdl is commonly used. Most verilog operators will operate on both busses and simple. Brackets In Verilog.

From www.vrogue.co

Module Hierarchy Example 1 Verilog Pro vrogue.co Brackets In Verilog The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb) on the right. Busses are defined by putting a range in square. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). The verilog syntax description in this reference manual uses the following grammar:. Brackets In Verilog.

From www.slideserve.com

PPT Combinational Logic in Verilog PowerPoint Presentation, free Brackets In Verilog Means zero or more repetitions of the. Verilog hdl is commonly used. I'm a vhdl guy, but typically brackets and parentheses indicate reference to. Brackets [] are part of the verilog syntax (vector range, bit and part select, memory element). The curly braces mean concatenation, from most significant bit (msb) on the left down to the least significant bit (lsb). Brackets In Verilog.