Clock Multiplexer Example . Such a clock multiplexer needs to. On the clock output port you'll have 8 generated. a clock multiplexer (also called clock switch) is required for the selection of the clock source. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. The output of a clock multiplexer (mux) is a form of generated clock. for example, let's say you have 8 input clocks called inclk[7:0]. • 525 race street • san jose.

from www.renesas.cn

the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. On the clock output port you'll have 8 generated. for example, let's say you have 8 input clocks called inclk[7:0]. • 525 race street • san jose. a clock multiplexer (also called clock switch) is required for the selection of the clock source. The output of a clock multiplexer (mux) is a form of generated clock. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. Such a clock multiplexer needs to.

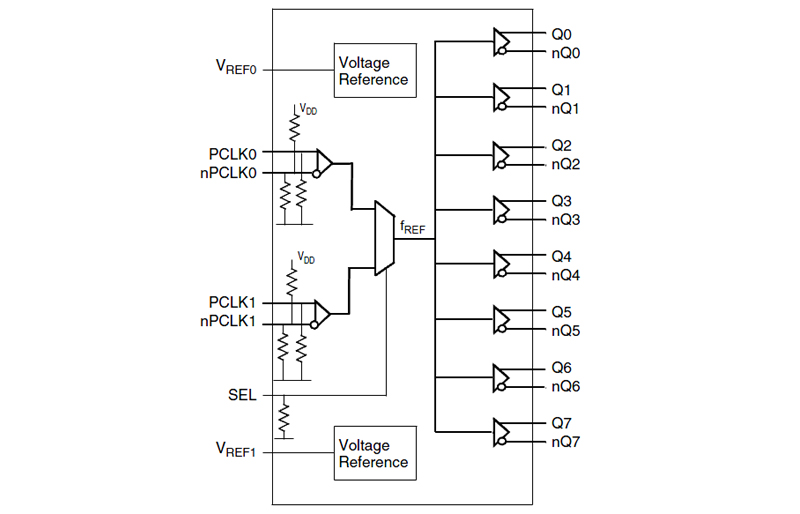

时钟多路复用器(MUX) Renesas

Clock Multiplexer Example for example, let's say you have 8 input clocks called inclk[7:0]. • 525 race street • san jose. Such a clock multiplexer needs to. a clock multiplexer (also called clock switch) is required for the selection of the clock source. for example, let's say you have 8 input clocks called inclk[7:0]. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. The output of a clock multiplexer (mux) is a form of generated clock. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. On the clock output port you'll have 8 generated.

From ar.inspiredpencil.com

2x1 Mux Schematic Clock Multiplexer Example The output of a clock multiplexer (mux) is a form of generated clock. • 525 race street • san jose. Such a clock multiplexer needs to. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. for example, let's say you have 8 input clocks called inclk[7:0]. the timing analyzer makes. Clock Multiplexer Example.

From wiredataistrajemta.z4.web.core.windows.net

Multilevel Circuit Diagram Truth Table Clock Multiplexer Example Such a clock multiplexer needs to. • 525 race street • san jose. for example, let's say you have 8 input clocks called inclk[7:0]. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. The output of a clock multiplexer (mux) is a form of generated clock. the timing analyzer makes. Clock Multiplexer Example.

From wiringfixsumeriessf.z21.web.core.windows.net

Design 81 Multiplexer Using 41 Multiplexer Clock Multiplexer Example On the clock output port you'll have 8 generated. • 525 race street • san jose. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. a clock multiplexer (also called clock switch) is required for the selection of the clock source. Such a clock multiplexer needs to. for example, let's. Clock Multiplexer Example.

From 778139821211757900.weebly.com

Multiplexer Design Digital Clock Project Clock Multiplexer Example • 525 race street • san jose. Such a clock multiplexer needs to. a clock multiplexer (also called clock switch) is required for the selection of the clock source. On the clock output port you'll have 8 generated. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. The output of. Clock Multiplexer Example.

From support.xilinx.com

301 Moved Permanently Clock Multiplexer Example clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. • 525 race street • san jose. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. The output of a clock multiplexer (mux) is a form of generated clock. On the clock output port. Clock Multiplexer Example.

From slideplayer.com

IAY 0600 Digital Systems Design ppt download Clock Multiplexer Example • 525 race street • san jose. The output of a clock multiplexer (mux) is a form of generated clock. On the clock output port you'll have 8 generated. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. Such a clock multiplexer needs to. a clock multiplexer (also called clock. Clock Multiplexer Example.

From dev.to

Verilog Mux 2 to 1 (Multiplexer) DEV Community Clock Multiplexer Example for example, let's say you have 8 input clocks called inclk[7:0]. a clock multiplexer (also called clock switch) is required for the selection of the clock source. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. Such a clock multiplexer needs to. The output of a clock multiplexer (mux). Clock Multiplexer Example.

From www.renesas.cn

时钟多路复用器(MUX) Renesas Clock Multiplexer Example Such a clock multiplexer needs to. • 525 race street • san jose. a clock multiplexer (also called clock switch) is required for the selection of the clock source. The output of a clock multiplexer (mux) is a form of generated clock. for example, let's say you have 8 input clocks called inclk[7:0]. On the clock output port. Clock Multiplexer Example.

From descubrearduino.com

🥇 Multiplexor, ¿Qúe es y cómo Funciona este tipo de circuitos? Clock Multiplexer Example the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. for example, let's say you have 8 input clocks called inclk[7:0]. Such a clock multiplexer needs to. a clock multiplexer (also called clock switch) is required for the selection of the clock source. clock multiplexers trigger warnings from a. Clock Multiplexer Example.

From www.renesas.com

Clock Multiplexers, Clock MUX Renesas Clock Multiplexer Example the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. • 525 race street • san jose. a clock multiplexer (also called clock switch) is required for the selection of the clock source. On the clock output port you'll have 8 generated. clock multiplexers trigger warnings from a wide range. Clock Multiplexer Example.

From www.google.com.mx

Patent US7893748 Glitchfree clock multiplexer that provides an Clock Multiplexer Example Such a clock multiplexer needs to. The output of a clock multiplexer (mux) is a form of generated clock. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. a clock multiplexer (also called clock switch) is required for the selection of the clock source. for example, let's say you have. Clock Multiplexer Example.

From alarminabox.co.za

MAKS Multiplexer Wired 8 Zones Module, including 2500 mAh battery up Clock Multiplexer Example The output of a clock multiplexer (mux) is a form of generated clock. a clock multiplexer (also called clock switch) is required for the selection of the clock source. Such a clock multiplexer needs to. On the clock output port you'll have 8 generated. • 525 race street • san jose. the timing analyzer makes it easy to. Clock Multiplexer Example.

From www.coursehero.com

[Solved] Design a 4bit "universal shift register" using four Clock Multiplexer Example The output of a clock multiplexer (mux) is a form of generated clock. Such a clock multiplexer needs to. • 525 race street • san jose. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. a clock multiplexer (also called clock switch) is required for the selection of the clock source.. Clock Multiplexer Example.

From www.youtube.com

Multiplexers YouTube Clock Multiplexer Example for example, let's say you have 8 input clocks called inclk[7:0]. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. On the clock output port you'll have 8 generated. Such a clock multiplexer. Clock Multiplexer Example.

From www.google.ch

Patent US6265930 Glitch free clock multiplexer circuit Google Clock Multiplexer Example clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. a clock multiplexer (also called clock switch) is required for the selection of the clock source. Such a clock multiplexer needs to. The output of a clock multiplexer (mux) is a form of generated clock. • 525 race street • san jose.. Clock Multiplexer Example.

From vlsiuniverse.blogspot.com

Clock multiplexer for glitchfree clock switching Clock Multiplexer Example clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. Such a clock multiplexer needs to. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. • 525 race street • san jose. The output of a clock multiplexer (mux) is a form of generated. Clock Multiplexer Example.

From www.renesas.com

Clock Multiplexers, Clock MUX Renesas Clock Multiplexer Example • 525 race street • san jose. Such a clock multiplexer needs to. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. On the clock output port you'll have 8 generated. a clock multiplexer (also called clock switch) is required for the selection of the clock source. clock multiplexers. Clock Multiplexer Example.

From www.alibaba.com

Integrated Circuits Adclk854bcpz Clock Multiplexer Ic Electronic Clock Multiplexer Example clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. On the clock output port you'll have 8 generated. for example, let's say you have 8 input clocks called inclk[7:0]. a clock multiplexer. Clock Multiplexer Example.

From www.researchgate.net

Timing diagram of the sequential readout. HOLD signal fixes the values Clock Multiplexer Example The output of a clock multiplexer (mux) is a form of generated clock. for example, let's say you have 8 input clocks called inclk[7:0]. • 525 race street • san jose. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. a clock multiplexer (also called clock switch) is required. Clock Multiplexer Example.

From www.electroniclinic.com

Multiplexer in Digital Electronics, Block Diagram, Designing, and Logic Clock Multiplexer Example Such a clock multiplexer needs to. a clock multiplexer (also called clock switch) is required for the selection of the clock source. for example, let's say you have 8 input clocks called inclk[7:0]. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. • 525 race street • san jose.. Clock Multiplexer Example.

From eecs.blog

8Bit Computer Multiplexer and Demultiplexer The EECS Blog Clock Multiplexer Example the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. Such a clock multiplexer needs to. for example, let's say you have 8 input clocks called inclk[7:0]. a clock multiplexer (also called clock switch) is required for the selection of the clock source. • 525 race street • san jose.. Clock Multiplexer Example.

From eureka.patsnap.com

Clock multiplexer device and clock switching method Eureka Patsnap Clock Multiplexer Example the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. for example, let's say you have 8 input clocks called inclk[7:0]. On the clock output port you'll have 8 generated. a clock multiplexer (also called clock switch) is required for the selection of the clock source. clock multiplexers trigger. Clock Multiplexer Example.

From www.researchgate.net

An example graph network generated for two custom states using Clock Multiplexer Example for example, let's say you have 8 input clocks called inclk[7:0]. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. On the clock output port you'll have 8 generated. The output of a. Clock Multiplexer Example.

From newdisplay808.weebly.com

8 To 1 Multiplexer Vhdl newdisplay Clock Multiplexer Example On the clock output port you'll have 8 generated. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. Such a clock multiplexer needs to. for example, let's say you have 8 input clocks called inclk[7:0]. • 525 race street • san jose. The output of a clock multiplexer (mux) is. Clock Multiplexer Example.

From www.cnblogs.com

SDC是如何炼成的?时钟定义篇 附create_generated_clock花式定义方法! 春风一郎 博客园 Clock Multiplexer Example for example, let's say you have 8 input clocks called inclk[7:0]. a clock multiplexer (also called clock switch) is required for the selection of the clock source. Such a clock multiplexer needs to. • 525 race street • san jose. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. . Clock Multiplexer Example.

From vlsiuniverse.blogspot.com

Clock multiplexer for glitchfree clock switching Clock Multiplexer Example for example, let's say you have 8 input clocks called inclk[7:0]. The output of a clock multiplexer (mux) is a form of generated clock. • 525 race street • san jose. On the clock output port you'll have 8 generated. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. Such a. Clock Multiplexer Example.

From www.electroniclinic.com

Multiplexer in Digital Electronics, Block Diagram, Designing, and Logic Clock Multiplexer Example On the clock output port you'll have 8 generated. Such a clock multiplexer needs to. a clock multiplexer (also called clock switch) is required for the selection of the clock source. • 525 race street • san jose. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. the timing analyzer. Clock Multiplexer Example.

From www.semiconductorforu.com

The Multiplexer Working and Its Applications Semiconductor for You Clock Multiplexer Example the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. On the clock output port you'll have 8 generated. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. for example, let's say you have 8 input clocks called inclk[7:0]. The output of a. Clock Multiplexer Example.

From www.arrow.com

SY56017R Reference Design Clock Multiplexer Clock Multiplexer Example a clock multiplexer (also called clock switch) is required for the selection of the clock source. The output of a clock multiplexer (mux) is a form of generated clock. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. Such a clock multiplexer needs to. On the clock output port you'll have. Clock Multiplexer Example.

From www.youtube.com

Construction of Common bus system using Multiplexer with example in Clock Multiplexer Example Such a clock multiplexer needs to. • 525 race street • san jose. The output of a clock multiplexer (mux) is a form of generated clock. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. for example, let's say you have 8 input clocks called inclk[7:0]. clock multiplexers trigger. Clock Multiplexer Example.

From www.researchgate.net

The structure of a 31 positiveedgetriggered clock multiplexer Clock Multiplexer Example clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. The output of a clock multiplexer (mux) is a form of generated clock. for example, let's say you have 8 input clocks called inclk[7:0]. a clock multiplexer (also called clock switch) is required for the selection of the clock source. •. Clock Multiplexer Example.

From www.renesas.com

Clock Multiplexers, Clock MUX Renesas Clock Multiplexer Example a clock multiplexer (also called clock switch) is required for the selection of the clock source. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. On the clock output port you'll have 8 generated. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis. Clock Multiplexer Example.

From www.youtube.com

Multiplexers and Demultiplexers YouTube Clock Multiplexer Example The output of a clock multiplexer (mux) is a form of generated clock. a clock multiplexer (also called clock switch) is required for the selection of the clock source. • 525 race street • san jose. the timing analyzer makes it easy to use synopsys® design constraint (sdc) commands to constrain complex clock. Such a clock multiplexer needs. Clock Multiplexer Example.

From www.glurgeek.com

Behavioral UML diagrams Timing Diagram Clock Multiplexer Example On the clock output port you'll have 8 generated. for example, let's say you have 8 input clocks called inclk[7:0]. clock multiplexers trigger warnings from a wide range of design rule check and timing analysis tools. The output of a clock multiplexer (mux) is a form of generated clock. Such a clock multiplexer needs to. • 525 race. Clock Multiplexer Example.