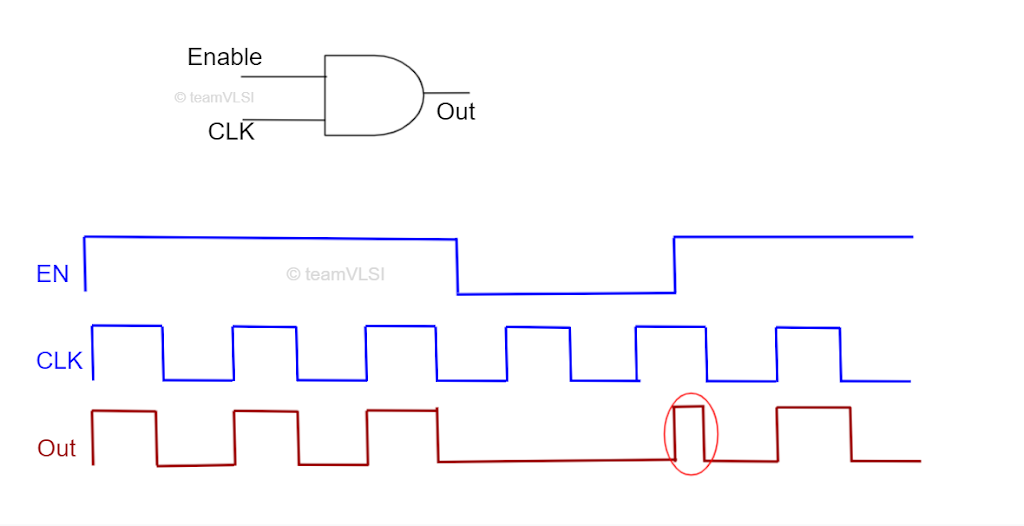

Why Latch Is Used In Clock Gating . Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In this technique, the gated clock output is obtained from the latch and the. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design.

from teamvlsi.com

I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. In this technique, the gated clock output is obtained from the latch and the. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg.

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI

Why Latch Is Used In Clock Gating So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In this technique, the gated clock output is obtained from the latch and the. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design.

From www.cnblogs.com

Clock Gating Checks 小勇5 博客园 Why Latch Is Used In Clock Gating In this technique, the gated clock output is obtained from the latch and the. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. I have seen many sources recommending the. Why Latch Is Used In Clock Gating.

From www.semanticscholar.org

[PDF] Clock Gating Based Low Power ALU Design Semantic Scholar Why Latch Is Used In Clock Gating I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. So whenever, clock is low, the latch. Why Latch Is Used In Clock Gating.

From saurabhanand-21.medium.com

Clock Gating using latch and Logic gates by SAURABH ANAND Medium Why Latch Is Used In Clock Gating Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. In this technique, the gated clock output. Why Latch Is Used In Clock Gating.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Why Latch Is Used In Clock Gating I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In this technique, the gated clock output is obtained from the latch and the. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. In computer architecture, clock gating is a popular power management. Why Latch Is Used In Clock Gating.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Why Latch Is Used In Clock Gating So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Compare. Why Latch Is Used In Clock Gating.

From www.researchgate.net

3 Clock gating of the main clock to some component Download Why Latch Is Used In Clock Gating Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In this technique, the gated clock output is obtained from the latch and the. Learn how to use integrated clock gating cells (icg) to. Why Latch Is Used In Clock Gating.

From vlsimaster.com

Clock Gating VLSI Master Why Latch Is Used In Clock Gating So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. In this technique, the gated. Why Latch Is Used In Clock Gating.

From www.researchgate.net

Latch Clock Gating for DFT Download Scientific Diagram Why Latch Is Used In Clock Gating So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. In computer architecture, clock. Why Latch Is Used In Clock Gating.

From semiengineering.com

Clock Gating Semiconductor Engineering Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. In this technique, the. Why Latch Is Used In Clock Gating.

From www.semanticscholar.org

Figure 1 from Clock Gating Based Low Power ALU Design Semantic Scholar Why Latch Is Used In Clock Gating In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. In this technique, the gated clock output is obtained from the latch and the. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Learn how to use integrated clock gating. Why Latch Is Used In Clock Gating.

From www.slideshare.net

Clock gating Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. In computer architecture, clock gating is. Why Latch Is Used In Clock Gating.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI Why Latch Is Used In Clock Gating I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at. Why Latch Is Used In Clock Gating.

From www.youtube.com

Clock Gating Basics Basics of Clock Gating Clock Gating Techniques Why Latch Is Used In Clock Gating In this technique, the gated clock output is obtained from the latch and the. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. So whenever, clock is low, the latch. Why Latch Is Used In Clock Gating.

From www.slideserve.com

PPT 32bit parallel load register with clock gating PowerPoint Why Latch Is Used In Clock Gating Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. In this technique, the gated. Why Latch Is Used In Clock Gating.

From webdocs.cs.ualberta.ca

Gating the clock Why Latch Is Used In Clock Gating I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. In. Why Latch Is Used In Clock Gating.

From www.researchgate.net

Transmission gate based D latch. Download Scientific Diagram Why Latch Is Used In Clock Gating I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. So whenever, clock is low, the latch. Why Latch Is Used In Clock Gating.

From www.researchgate.net

Latch Clock Gating for DFT Download Scientific Diagram Why Latch Is Used In Clock Gating Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Learn how icg cell. Why Latch Is Used In Clock Gating.

From vlsihq.com

Clock Gating technique for Power Saving vlsiHQ Why Latch Is Used In Clock Gating In this technique, the gated clock output is obtained from the latch and the. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. So whenever, clock is low, the latch will be transparent, and en. Why Latch Is Used In Clock Gating.

From www.slideshare.net

Clock gating Why Latch Is Used In Clock Gating In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get. Why Latch Is Used In Clock Gating.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Why Latch Is Used In Clock Gating I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. In this technique, the gated clock output is obtained from the latch and the. So whenever, clock is low, the latch will be. Why Latch Is Used In Clock Gating.

From electronics.stackexchange.com

digital logic On a method of clock gating with a latch Electrical Why Latch Is Used In Clock Gating In this technique, the gated clock output is obtained from the latch and the. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. Learn how to use integrated clock gating cells (icg) to. Why Latch Is Used In Clock Gating.

From vlsimaster.com

Clock Gating VLSI Master Why Latch Is Used In Clock Gating Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1,. Why Latch Is Used In Clock Gating.

From www.slideserve.com

PPT The clock PowerPoint Presentation, free download ID2403529 Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. In this technique, the gated clock output is obtained from the latch and the. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. I have seen many sources recommending the use of a negative level sensitive. Why Latch Is Used In Clock Gating.

From courses.cs.washington.edu

Clocking an RS latch Why Latch Is Used In Clock Gating In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. So whenever, clock is. Why Latch Is Used In Clock Gating.

From electronics.stackexchange.com

digital logic Why ANDLatch based clock gate (ICG cell) is not Why Latch Is Used In Clock Gating So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In. Why Latch Is Used In Clock Gating.

From www.slideserve.com

PPT L17 Logic Level Design PowerPoint Presentation, free download Why Latch Is Used In Clock Gating Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. In this technique, the gated clock output is obtained from the latch and the. I have seen many sources recommending the use of a negative. Why Latch Is Used In Clock Gating.

From www.electronicsforu.com

Clock Gating for the of Things Design Guide Why Latch Is Used In Clock Gating Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In this technique, the gated clock output is obtained from the latch and the. In computer architecture, clock gating is a popular power. Why Latch Is Used In Clock Gating.

From vlsiuniverse.blogspot.com

Need for clock gating checks need for glitchless clock propagation Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. In this technique, the gated clock output is obtained from the latch and the. I have seen many sources recommending the use of a. Why Latch Is Used In Clock Gating.

From www.linkedin.com

A video blog on latch based clock gating and integrated clock gate cell Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. In this technique, the. Why Latch Is Used In Clock Gating.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. Learn how to use integrated clock gating cells (icg) to reduce dynamic power consumption in vlsi design. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Compare icg with clock gating using. Why Latch Is Used In Clock Gating.

From vlsi-soc.blogspot.com

VLSI SoC Design Integrated Clock and Power Gating Why Latch Is Used In Clock Gating So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get latched at the output of l1, and will remain high until there is a change in en signal. Compare icg with clock gating using and gate and understand the advantages and disadvantages of icg. In computer architecture, clock gating. Why Latch Is Used In Clock Gating.

From mungfali.com

Clock Gating VLSI Why Latch Is Used In Clock Gating In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. So whenever, clock is low, the latch will be transparent, and en which is high from 0.5ns to 1ns will get. Why Latch Is Used In Clock Gating.

From teamvlsi.blogspot.com

Team VLSI Why Latch Is Used In Clock Gating Learn how icg cell (integrated clock gating) can reduce dynamic power consumption in low power asic design. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. So whenever, clock is. Why Latch Is Used In Clock Gating.

From www.slideserve.com

PPT Gated or Clocked SR latch PowerPoint Presentation, free download Why Latch Is Used In Clock Gating In this technique, the gated clock output is obtained from the latch and the. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. Compare icg with clock gating using and. Why Latch Is Used In Clock Gating.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Why Latch Is Used In Clock Gating In computer architecture, clock gating is a popular power management technique used in many synchronous circuits for reducing dynamic. In this technique, the gated clock output is obtained from the latch and the. I have seen many sources recommending the use of a negative level sensitive latch, and an and gate for clock. Compare icg with clock gating using and. Why Latch Is Used In Clock Gating.