Loop Timer Fpga Labview . Timed loop structures are always sctls when. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. The below figure shows the use of feedback. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. In below figure, there is two indicators: The only difference i've found is this: You need to measure tick count after loop timer returns and before your code executes. How to fix the problem: Using the loop timer express vi to enforce proper simulated timing. Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a.

from www.youtube.com

How to fix the problem: The only difference i've found is this: Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. The below figure shows the use of feedback. Using the loop timer express vi to enforce proper simulated timing. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. Timed loop structures are always sctls when. In below figure, there is two indicators: You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. You need to measure tick count after loop timer returns and before your code executes.

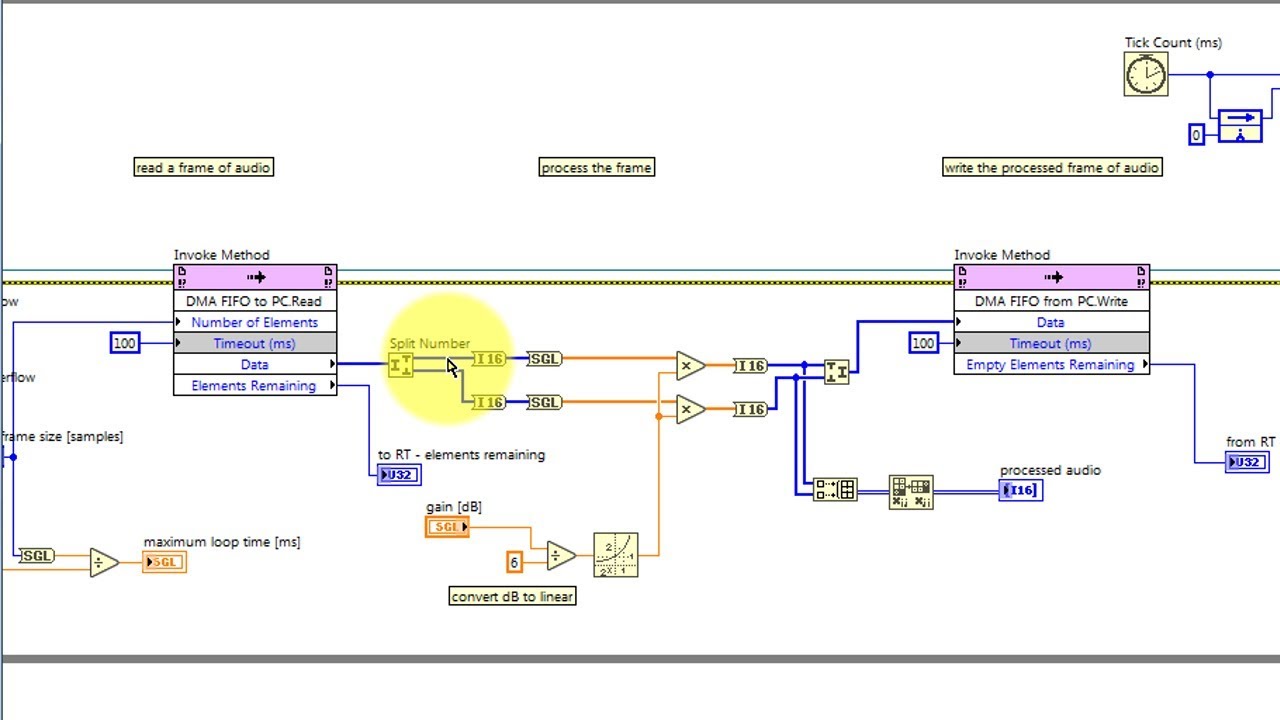

LabVIEW code Stream highspeed data between FPGA and PC with a DMA

Loop Timer Fpga Labview The only difference i've found is this: The only difference i've found is this: I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. Timed loop structures are always sctls when. Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. The below figure shows the use of feedback. You need to measure tick count after loop timer returns and before your code executes. In below figure, there is two indicators: How to fix the problem: Using the loop timer express vi to enforce proper simulated timing.

From www.eetimes.com

Tip FFTs in LabVIEW FPGA EE Times Loop Timer Fpga Labview How to fix the problem: Timed loop structures are always sctls when. In below figure, there is two indicators: Using the loop timer express vi to enforce proper simulated timing. The only difference i've found is this: Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. I fixed the. Loop Timer Fpga Labview.

From forums.ni.com

Synchronizing Timed Loops NI Community Loop Timer Fpga Labview The below figure shows the use of feedback. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. Using the loop timer express vi to enforce proper simulated timing. Timed loop structures are always sctls when. I fixed the control values for each loop timer 100us,. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW code Stream highspeed data between FPGA and RT with a DMA Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. In below figure, there is two indicators: I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. Code parallel to the loop timer will execute twice. Loop Timer Fpga Labview.

From www.mdpi.com

Energies Free FullText RealTime Hardware in the Loop Simulation Loop Timer Fpga Labview The below figure shows the use of feedback. The only difference i've found is this: In below figure, there is two indicators: Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is. Loop Timer Fpga Labview.

From www.researchgate.net

Field programmable gate array (FPGA) code. (a) The highlevel LabVIEW Loop Timer Fpga Labview Timed loop structures are always sctls when. Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. You need to measure tick count after loop timer returns and before your code executes. Using the loop timer express vi to enforce proper simulated timing. In below figure, there is two indicators:. Loop Timer Fpga Labview.

From www.mdpi.com

Energies Free FullText RealTime Hardware in the Loop Simulation Loop Timer Fpga Labview The below figure shows the use of feedback. Timed loop structures are always sctls when. You need to measure tick count after loop timer returns and before your code executes. In below figure, there is two indicators: You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick. Loop Timer Fpga Labview.

From forums.ni.com

Validate Your FPGA Code Before You Compile Using the LabVIEW FPGA Loop Timer Fpga Labview You need to measure tick count after loop timer returns and before your code executes. Timed loop structures are always sctls when. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. The below figure shows the use of feedback. I fixed the control values for. Loop Timer Fpga Labview.

From knowledge.ni.com

What are the Clock Sources for the LabVIEW FPGA Timing VIs? NI Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. How to fix the problem: In below figure, there is two indicators: Timed loop structures are always sctls when. The only difference i've found is this: Using the loop timer express vi to enforce proper simulated. Loop Timer Fpga Labview.

From knowledge.ni.com

How Do I Set the Rate of a Timed Loop on an FPGA Target? NI Loop Timer Fpga Labview I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. You need to measure tick count after loop timer returns and before your code executes. Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. You can obtain the iteration time. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW code Timed loop (walkthrough) YouTube Loop Timer Fpga Labview I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. In below figure, there is two indicators: Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. Timed loop structures are always sctls when. You can obtain the iteration time. Loop Timer Fpga Labview.

From forums.ni.com

Validate Your FPGA Code Before You Compile Using the LabVIEW FPGA Loop Timer Fpga Labview Timed loop structures are always sctls when. The only difference i've found is this: How to fix the problem: Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. I fixed. Loop Timer Fpga Labview.

From www.youtube.com

Labview For loop YouTube Loop Timer Fpga Labview The only difference i've found is this: Using the loop timer express vi to enforce proper simulated timing. Timed loop structures are always sctls when. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. The below figure shows the use of feedback. Code parallel to the loop timer will. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW FPGA Basic RTL constructs timer, frequency divider Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. The only difference i've found is this: How to fix the problem: Using the loop timer express vi to enforce proper simulated timing. In below figure, there is two indicators: Timed loop structures are always sctls. Loop Timer Fpga Labview.

From globlib4u.wordpress.com

LabVIEW FPGA 2012 Productivity Enhancements and Optimizations Lib4U Loop Timer Fpga Labview Timed loop structures are always sctls when. The only difference i've found is this: Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. You need to measure tick count after loop timer returns and before your code executes. I fixed the control values for each loop timer 100us, but you. Loop Timer Fpga Labview.

From www.researchgate.net

FPGA implementation of the inverter model on the cRIO hardware. Top Loop Timer Fpga Labview The below figure shows the use of feedback. The only difference i've found is this: Timed loop structures are always sctls when. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. Code parallel to the loop timer will execute twice at startup without a wait. Loop Timer Fpga Labview.

From www.allaboutcircuits.com

Reading Analog Values and PWM with LabVIEW FPGA Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. How to fix the problem: You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. You need to measure tick count after loop timer returns and before your code executes. The only difference i've found. Loop Timer Fpga Labview.

From www.youtube.com

LABVIEW TUTORIALS FOR LOOP YouTube Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. In below figure, there is two indicators: Timed loop structures are always sctls when. Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. How to fix the problem: The only. Loop Timer Fpga Labview.

From www.researchgate.net

Dedicated program for communication between LabVIEW written program and Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. The only difference i've found is this: Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. You need to measure tick count after loop timer returns and before your code executes. How to fix the problem: In below. Loop Timer Fpga Labview.

From knowledge.ni.com

FPGA Loop Timer Express VI Initial Delay NI Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. In below figure, there is two indicators: Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. I fixed the control values for each loop timer 100us,. Loop Timer Fpga Labview.

From www.metisautomation.co.uk

Embedded Systems, Real Time & FPGA Metis Automation Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. You need to measure tick count after loop timer returns and before your code executes. How to fix the problem: In below figure, there is two indicators: The only difference i've found is this: Code parallel to the loop timer will execute twice at startup without a wait in. Loop Timer Fpga Labview.

From forum.digilent.com

Using hardware timer output as a source for a timed loop LabVIEW Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. You need to measure tick count after loop timer returns and before your code executes. The only difference i've found is this: In below figure, there is two indicators: Using the loop timer express vi to. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW code Timerdriven background process using interrupt request Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. The below figure shows the use of feedback. How to fix the problem: In below figure, there is two indicators: I fixed the control values for each loop timer 100us, but you can find the e_loop_time. Loop Timer Fpga Labview.

From zone.ni.com

Using the SinglePrecision FloatingPoint Data Type LabVIEW 2018 FPGA Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. The only difference i've found is this: Code parallel to the loop timer will execute twice at startup without a wait in between, but code. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW code Stream highspeed data between FPGA and PC with a DMA Loop Timer Fpga Labview In below figure, there is two indicators: Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. Timed loop structures are always sctls when. You need to measure tick count after loop timer returns and before your code executes. You can obtain the iteration time of the loop by subtracting the. Loop Timer Fpga Labview.

From www.youtube.com

SingleCycle Timed Loops in LabVIEW FPGA YouTube Loop Timer Fpga Labview Timed loop structures are always sctls when. You need to measure tick count after loop timer returns and before your code executes. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. Code parallel to the loop timer will execute twice at startup without a wait. Loop Timer Fpga Labview.

From fpganow.com

LabVIEW Page 2 FPGA Now! Loop Timer Fpga Labview The below figure shows the use of feedback. Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. Timed loop structures are always sctls when. In. Loop Timer Fpga Labview.

From forums.ni.com

Loop Speed Fluctuations FPGA NI Community National Instruments Loop Timer Fpga Labview I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. The below figure shows the use of feedback. Using the loop timer express vi to enforce proper simulated timing. How to fix the problem: In below figure, there is two indicators: You can obtain the iteration time of the loop. Loop Timer Fpga Labview.

From learn-cf.ni.com

Global variable (FPGA) Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. The only difference i've found is this: The below figure shows the use of feedback. You need to measure tick count after loop timer returns and before your code. Loop Timer Fpga Labview.

From forums.ni.com

Solved FPGA parallel while loop + Loop Time Problem NI Community Loop Timer Fpga Labview You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. You need to measure tick count after loop timer returns and before your code executes. The. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW code Timed loop (expected results) YouTube Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. Timed loop structures are always sctls when. In below figure, there is two indicators: You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. Code parallel to. Loop Timer Fpga Labview.

From forums.ni.com

Pass array between FPGA loops NI Community Loop Timer Fpga Labview Code parallel to the loop timer will execute twice at startup without a wait in between, but code in a. The only difference i've found is this: Using the loop timer express vi to enforce proper simulated timing. The below figure shows the use of feedback. How to fix the problem: You can obtain the iteration time of the loop. Loop Timer Fpga Labview.

From www.youtube.com

How to Program an FPGA with LabVIEW FPGA YouTube Loop Timer Fpga Labview Timed loop structures are always sctls when. How to fix the problem: Using the loop timer express vi to enforce proper simulated timing. You need to measure tick count after loop timer returns and before your code executes. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. The below. Loop Timer Fpga Labview.

From www.youtube.com

how to create a timer in labview YouTube Loop Timer Fpga Labview I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. You can obtain the iteration time of the loop by subtracting the calculated tick count from the previous loop and the current tick count. In below figure, there is two indicators: Timed loop structures are always sctls when. The only. Loop Timer Fpga Labview.

From www.youtube.com

LabVIEW procedure Make your first FPGA application YouTube Loop Timer Fpga Labview I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. You need to measure tick count after loop timer returns and before your code executes. The only difference i've found is this: Code parallel to the loop timer will execute twice at startup without a wait in between, but code. Loop Timer Fpga Labview.

From forums.ni.com

Pass value between while loops using FIFO in LabView FPGA NI Community Loop Timer Fpga Labview Using the loop timer express vi to enforce proper simulated timing. Timed loop structures are always sctls when. I fixed the control values for each loop timer 100us, but you can find the e_loop_time value is not 100us. In below figure, there is two indicators: Code parallel to the loop timer will execute twice at startup without a wait in. Loop Timer Fpga Labview.