Clock Gating Design . Can you figure out why? The clock gating method stops the clock for those elements in the design whose data is not toggling. Often, the clock signal drives a large capacitive load,. The clock gating technique is one of the widely used techniques for low power design. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. In this article, we’ll discuss the. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique.

from www.semanticscholar.org

Can you figure out why? In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. In this article, we’ll discuss the. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating technique is one of the widely used techniques for low power design. The clock gating method stops the clock for those elements in the design whose data is not toggling. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Often, the clock signal drives a large capacitive load,.

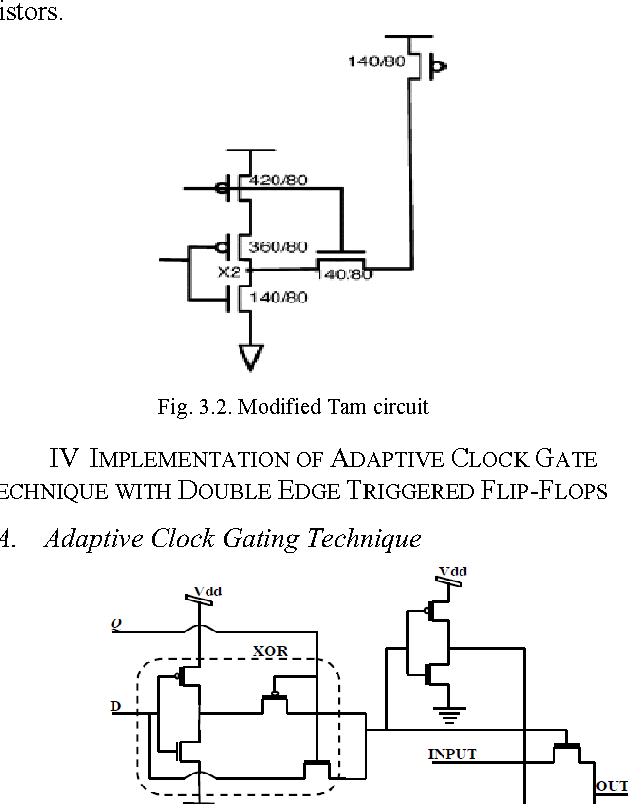

Figure 3.2 from Design and implementation of adaptive clock gating technique with double edge

Clock Gating Design Integrated clock gating (icg) cell is a specially designed cell that is used for clock. The clock gating method stops the clock for those elements in the design whose data is not toggling. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. The clock gating technique is one of the widely used techniques for low power design. Often, the clock signal drives a large capacitive load,. Can you figure out why? In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. In this article, we’ll discuss the.

From zhuanlan.zhihu.com

低功耗设计基础:Clock Gating 知乎 Clock Gating Design Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Can you figure out why? Integrated clock gating (icg) cell is a specially designed cell that is used for clock. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using. Clock Gating Design.

From soc-asic-design.blogspot.com

All you need to know about SoC Design, Methodologies and Techniques Low Power Techniques Clock Gating Design In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. In this article, we’ll discuss the. Can you figure out why? Because a high on ‘en’ signal allows the clock cycle. Clock Gating Design.

From www.semanticscholar.org

Figure 2 from Design of ALU with LFSR Using Clock Gating Semantic Scholar Clock Gating Design Can you figure out why? The clock gating method stops the clock for those elements in the design whose data is not toggling. The clock gating technique is one of the widely used techniques for low power design. In this article, we’ll discuss the. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Often,. Clock Gating Design.

From www.researchgate.net

Example of GatedClock Design Download Scientific Diagram Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Often, the clock signal drives a large capacitive load,. The clock gating technique is one of the widely used techniques for low power. Clock Gating Design.

From www.youtube.com

Low Power VLSI Design Clock Gating Circuits Integrated Clock Gating (ICG) Power Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Often, the clock signal drives a large capacitive load,. The clock gating technique is one of the widely used techniques for low power design. The clock gating method stops the clock for those elements in the design whose data. Clock Gating Design.

From www.researchgate.net

Clock gating scheme Adapted from Hsu & Lin, 2011. Download Scientific Diagram Clock Gating Design In this article, we’ll discuss the. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. The clock gating method stops the clock for those elements in the design whose data is not toggling. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus.. Clock Gating Design.

From www.researchgate.net

(PDF) A Novel Clock Gating Approach for the Design of LowPower Linear Feedback Shift Registers Clock Gating Design In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. In most designs, data is loaded into. Clock Gating Design.

From www.researchgate.net

Waveforms showing edge combinations due to DET clock gating and example... Download Scientific Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. The clock gating technique is one of the widely used techniques for low power design. In this article, we will discuss the use of. Clock Gating Design.

From teamvlsi.blogspot.com

Team VLSI Clock Gating Design The clock gating technique is one of the widely used techniques for low power design. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. In this article, we’ll discuss the. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. Clock Gating Design.

From www.semanticscholar.org

Figure 3.2 from Design and implementation of adaptive clock gating technique with double edge Clock Gating Design Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. In this article, we’ll discuss the. Can you figure out why? The clock gating technique is one of the widely used techniques for low power design. Often, the clock signal drives a large capacitive load,. This technique of using an ‘and’ gate is referred to. Clock Gating Design.

From www.researchgate.net

Conventional ClockGating Scheme. Download Scientific Diagram Clock Gating Design Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Can you figure out why? In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. The clock gating method stops the clock for those elements in the design whose data is not. Clock Gating Design.

From semiengineering.com

Clock Gating Semiconductor Engineering Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. The clock gating technique is one of the. Clock Gating Design.

From www.slideserve.com

PPT L17 Logic Level Design PowerPoint Presentation, free download ID4138592 Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Can you figure out why? This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Because a high. Clock Gating Design.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Based Clock Gating Clock Gating Design Integrated clock gating (icg) cell is a specially designed cell that is used for clock. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating technique is one. Clock Gating Design.

From www.youtube.com

Clock Gating Based Energy Efficient ALU Design and Implementation on FPGA YouTube Clock Gating Design Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Often, the clock signal drives a large capacitive load,. The clock gating method stops the clock for those elements in the design whose data is not toggling. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at. Clock Gating Design.

From www.semanticscholar.org

Figure 3 from Clock Gating Based Low Power ALU Design Semantic Scholar Clock Gating Design This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Can you figure out why? Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Often, the clock signal drives a large capacitive load,. The clock gating technique is one of the widely used techniques for low power design.. Clock Gating Design.

From www.slideserve.com

PPT EE 587 SoC Design & Test PowerPoint Presentation, free download ID2400041 Clock Gating Design In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. The clock gating method stops the clock for those elements in the design whose data is. Clock Gating Design.

From pdfaqs.blogspot.com

Physical Design Clock Gating Clock Gating Design In this article, we’ll discuss the. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. The clock gating method stops the clock for those elements in the design whose data is. Clock Gating Design.

From logicsense.wordpress.com

Clock gating Techworld Clock Gating Design Integrated clock gating (icg) cell is a specially designed cell that is used for clock. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating technique is one of the widely used techniques for low power design. In this article, we’ll discuss the. The clock gating method stops the clock for. Clock Gating Design.

From www.elecfans.com

低功耗设计基础:Clock Gating电子发烧友网 Clock Gating Design Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. The clock gating technique is one of the widely used techniques for low power design. The clock gating method stops the clock for those elements in the design whose data. Clock Gating Design.

From mungfali.com

Clock Gating VLSI Clock Gating Design The clock gating technique is one of the widely used techniques for low power design. Can you figure out why? Often, the clock signal drives a large capacitive load,. In this article, we’ll discuss the. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. The clock. Clock Gating Design.

From www.slideshare.net

Clock gating Clock Gating Design Can you figure out why? In this article, we’ll discuss the. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using an. Clock Gating Design.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Design Often, the clock signal drives a large capacitive load,. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Can you figure out why? The clock gating method stops the clock for those elements. Clock Gating Design.

From www.vrogue.co

Vlsi Soc Design Clock Gating Integrated Cell vrogue.co Clock Gating Design In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. In this article, we’ll discuss the. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using an ‘and’ gate is referred to. Clock Gating Design.

From www.electronicsforu.com

Clock Gating for the of Things Design Guide Clock Gating Design Often, the clock signal drives a large capacitive load,. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Can you figure out why? The clock gating technique is one of the widely used techniques for low power design. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. In. Clock Gating Design.

From www.researchgate.net

3 Clock gating of the main clock to some component Download Scientific Diagram Clock Gating Design In this article, we’ll discuss the. Often, the clock signal drives a large capacitive load,. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. Because a high on ‘en’ signal allows the clock. Clock Gating Design.

From docslib.org

Clock Gating for Power Optimization in ASIC Design Cycle Theory & Practice DocsLib Clock Gating Design In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. The clock gating method stops the clock for those elements in the design whose data is not toggling. Can you figure out. Clock Gating Design.

From pdfaqs.blogspot.com

Physical Design Clock Gating Clock Gating Design Often, the clock signal drives a large capacitive load,. The clock gating technique is one of the widely used techniques for low power design. The clock gating method stops the clock for those elements in the design whose data is not toggling. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock. Clock Gating Design.

From www.slideserve.com

PPT Lecture 7 Power PowerPoint Presentation, free download ID4495903 Clock Gating Design This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. The clock gating technique is one. Clock Gating Design.

From www.semanticscholar.org

Figure 3 from Clock Gating Based Low Power ALU Design Semantic Scholar Clock Gating Design Often, the clock signal drives a large capacitive load,. Can you figure out why? In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Because a high on ‘en’ signal allows the. Clock Gating Design.

From www.slideserve.com

PPT Alexander Gnusin PowerPoint Presentation, free download ID3739809 Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating method stops the clock for those elements in the design whose data is not toggling. The clock gating technique is. Clock Gating Design.

From vlsi-soc.blogspot.com

VLSI SoC Design Integrated Clock and Power Gating Clock Gating Design The clock gating technique is one of the widely used techniques for low power design. Integrated clock gating (icg) cell is a specially designed cell that is used for clock. Often, the clock signal drives a large capacitive load,. In this article, we’ll discuss the. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus.. Clock Gating Design.

From www.researchgate.net

1 Traditional clockgating methodology for HLS based design flow Download Scientific Diagram Clock Gating Design In most designs, data is loaded into registers very infrequently, but the clock signal continues to toggle at every clock cycle. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. In this article, we’ll discuss the. The clock gating method stops the clock for those elements in the design whose data is not. Clock Gating Design.

From www.slideshare.net

Clock gating Clock Gating Design In this article, we will discuss the use of clock gating techniques with design examples for achieving lower power and also highlight the. The clock gating technique is one of the widely used techniques for low power design. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Integrated clock gating (icg) cell is a. Clock Gating Design.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Design Often, the clock signal drives a large capacitive load,. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Can you figure out why? The clock gating method stops the clock for those elements in the design whose data is not toggling. In this article, we will discuss the use of clock gating techniques. Clock Gating Design.