Clock Generator Without Using Always Block . So i would say a synth module would be using a simple counter. Write a clock generator without using always block. The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. Forever # (cycle/2) clk = ~clk. D flip flop) the code we write for the always block part is:. 2) second assign to always. Always@(clk) begin clk = 1; 1) convert first assign into initial begin clk = 0; In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. In general, if we are working on a sequential circuit, say a flip flop (e.g. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. If you want to model a clock you can: To give you an idea: End it will only run when clk is high, since you have. The problem is with this block:

from www.electronicecircuits.com

Always@(clk) begin clk = 1; So i would say a synth module would be using a simple counter. In general, if we are working on a sequential circuit, say a flip flop (e.g. 1) convert first assign into initial begin clk = 0; The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. If you want to model a clock you can: To give you an idea: 2) second assign to always. End it will only run when clk is high, since you have.

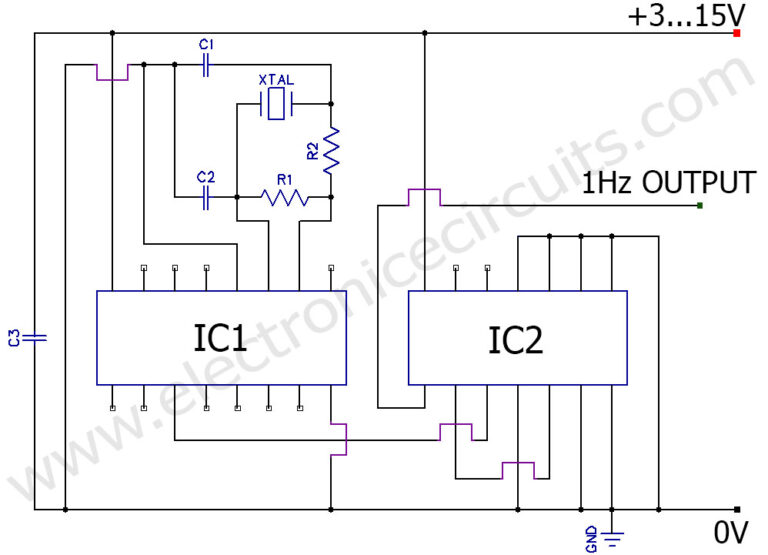

Precision 1Hz clock generator circuit Electronic Circuits

Clock Generator Without Using Always Block In general, if we are working on a sequential circuit, say a flip flop (e.g. 1) convert first assign into initial begin clk = 0; In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. If you want to model a clock you can: End it will only run when clk is high, since you have. So i would say a synth module would be using a simple counter. To give you an idea: Always@(clk) begin clk = 1; Forever # (cycle/2) clk = ~clk. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. In general, if we are working on a sequential circuit, say a flip flop (e.g. 2) second assign to always. The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. Write a clock generator without using always block. D flip flop) the code we write for the always block part is:. The problem is with this block:

From bestengineeringprojects.com

Clock Signal Generator Circuit Engineering Projects Clock Generator Without Using Always Block The problem is with this block: The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. End it will only run when clk is high, since you have. In general, if we are working on a sequential circuit, say a flip flop (e.g. Forever # (cycle/2) clk. Clock Generator Without Using Always Block.

From gieskes.nl

Gijs's Master Clock Generator Clock Generator Without Using Always Block Forever # (cycle/2) clk = ~clk. 1) convert first assign into initial begin clk = 0; Always@(clk) begin clk = 1; Write a clock generator without using always block. To give you an idea: End it will only run when clk is high, since you have. In general, if we are working on a sequential circuit, say a flip flop. Clock Generator Without Using Always Block.

From onlinedocs.microchip.com

Quadrature Clock Generator Clock Generator Without Using Always Block 1) convert first assign into initial begin clk = 0; The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. If you want to model a clock you can: 2) second assign to always. The following verilog clock generator module has three parameters to tweak the three. Clock Generator Without Using Always Block.

From www.edaboard.com

4 Phases NonOverlapping Clock Generator Forum for Electronics Clock Generator Without Using Always Block If you want to model a clock you can: End it will only run when clk is high, since you have. 1) convert first assign into initial begin clk = 0; Forever # (cycle/2) clk = ~clk. 2) second assign to always. So i would say a synth module would be using a simple counter. In verilog, a clock generator. Clock Generator Without Using Always Block.

From www.engineerlive.com

6 and 8 output 3.3V clock generators Engineer Live Clock Generator Without Using Always Block 2) second assign to always. In general, if we are working on a sequential circuit, say a flip flop (e.g. If you want to model a clock you can: The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. Always@(clk) begin clk = 1; D flip flop). Clock Generator Without Using Always Block.

From www.youtube.com

555 timer pulse Generator, 555 projects Circuit Diagram YouTube Clock Generator Without Using Always Block Always@(clk) begin clk = 1; Forever # (cycle/2) clk = ~clk. Write a clock generator without using always block. The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. In general, if we are working on a sequential circuit, say a flip flop (e.g. If you want. Clock Generator Without Using Always Block.

From www.eeweb.com

14 Ultra Low Jitter CrystalIn Clock Generator EE Clock Generator Without Using Always Block In general, if we are working on a sequential circuit, say a flip flop (e.g. If you want to model a clock you can: In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The following verilog clock generator module has three parameters to tweak the three different properties. Clock Generator Without Using Always Block.

From www.hpcwire.com

Renesas Unveils New Programmable Clock Generator Clock Generator Without Using Always Block In general, if we are working on a sequential circuit, say a flip flop (e.g. To give you an idea: Always@(clk) begin clk = 1; End it will only run when clk is high, since you have. 2) second assign to always. The difference between forever and always is that always can exist as a module item, which is the. Clock Generator Without Using Always Block.

From www.electronicecircuits.com

Precision 1Hz clock generator circuit Electronic Circuits Clock Generator Without Using Always Block In general, if we are working on a sequential circuit, say a flip flop (e.g. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. End it will only run when clk is high, since you have. D flip flop) the code we write for the always block part. Clock Generator Without Using Always Block.

From www.researchgate.net

4phase interleaving clock generator (a) schematic; (b) clock phases Clock Generator Without Using Always Block Write a clock generator without using always block. 1) convert first assign into initial begin clk = 0; So i would say a synth module would be using a simple counter. 2) second assign to always. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. The difference between forever and always. Clock Generator Without Using Always Block.

From www.youtube.com

Nonoverlapping Clock Generator with Optimized Falling/Rising EDGE Delay Clock Generator Without Using Always Block End it will only run when clk is high, since you have. 1) convert first assign into initial begin clk = 0; The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. In general, if we are working on a sequential circuit, say a flip flop (e.g. To give you an idea:. Clock Generator Without Using Always Block.

From learn.sparkfun.com

SparkFun Clock Generator 5P49V60 (Qwiic) Hookup Guide SparkFun Learn Clock Generator Without Using Always Block So i would say a synth module would be using a simple counter. In general, if we are working on a sequential circuit, say a flip flop (e.g. D flip flop) the code we write for the always block part is:. If you want to model a clock you can: Forever # (cycle/2) clk = ~clk. The following verilog clock. Clock Generator Without Using Always Block.

From learn.sparkfun.com

SparkFun Clock Generator 5P49V60 (Qwiic) Hookup Guide SparkFun Learn Clock Generator Without Using Always Block End it will only run when clk is high, since you have. Write a clock generator without using always block. 1) convert first assign into initial begin clk = 0; So i would say a synth module would be using a simple counter. The following verilog clock generator module has three parameters to tweak the three different properties as discussed. Clock Generator Without Using Always Block.

From bestengineeringprojects.com

Clock Signal Generator Circuit Best Engineering Projects Clock Generator Without Using Always Block Forever # (cycle/2) clk = ~clk. 1) convert first assign into initial begin clk = 0; 2) second assign to always. Always@(clk) begin clk = 1; So i would say a synth module would be using a simple counter. In general, if we are working on a sequential circuit, say a flip flop (e.g. In verilog, a clock generator is. Clock Generator Without Using Always Block.

From www.multisim.com

Copy of 555 clock generator Multisim Live Clock Generator Without Using Always Block The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. In general, if we are working on a sequential circuit, say a flip flop (e.g. Forever # (cycle/2) clk = ~clk. 1) convert first assign into initial begin clk = 0; End it will only run when clk is high, since you. Clock Generator Without Using Always Block.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Generator Without Using Always Block The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. To give you an idea: In general, if we are working on a sequential circuit, say a flip flop (e.g. Always@(clk) begin clk = 1; The difference between forever and always is that always can exist as a module item, which is. Clock Generator Without Using Always Block.

From gamma.app

Pin Diagram of 8284 Clock Generator Clock Generator Without Using Always Block D flip flop) the code we write for the always block part is:. Write a clock generator without using always block. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. In general, if we are working on a sequential circuit, say a flip flop (e.g. So i would. Clock Generator Without Using Always Block.

From www.electroniclinic.com

How to design digital clock using counters decoders and displays Clock Generator Without Using Always Block Always@(clk) begin clk = 1; D flip flop) the code we write for the always block part is:. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Forever # (cycle/2) clk = ~clk. The difference between forever and always is that always can exist as a module item, which is the. Clock Generator Without Using Always Block.

From www.mdpi.com

Electronics Free FullText A 6Bit 20 GS/s TimeInterleaved Two Clock Generator Without Using Always Block 2) second assign to always. Write a clock generator without using always block. Always@(clk) begin clk = 1; The problem is with this block: The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. End it will only run when clk is high, since you have. 1). Clock Generator Without Using Always Block.

From learn.sparkfun.com

SparkFun Clock Generator 5P49V60 (Qwiic) Hookup Guide SparkFun Learn Clock Generator Without Using Always Block End it will only run when clk is high, since you have. D flip flop) the code we write for the always block part is:. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. In general, if we are working on a sequential circuit, say a flip flop (e.g. The difference. Clock Generator Without Using Always Block.

From www.mdpi.com

A 500 kHz to 150 MHz MultiOutput Clock Generator Using Analog PLL and Clock Generator Without Using Always Block Write a clock generator without using always block. Forever # (cycle/2) clk = ~clk. In general, if we are working on a sequential circuit, say a flip flop (e.g. 1) convert first assign into initial begin clk = 0; So i would say a synth module would be using a simple counter. The following verilog clock generator module has three. Clock Generator Without Using Always Block.

From www.instructables.com

Clock Generator With Si5351 and Blue Pill 6 Steps (with Pictures Clock Generator Without Using Always Block In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Always@(clk) begin clk = 1; If you want to model a clock you can: 2) second assign to always. Write a clock generator without using always block. The problem is with this block: 1) convert first assign into initial. Clock Generator Without Using Always Block.

From bestengineeringprojects.com

Clock Signal Generator Circuit Engineering Projects Clock Generator Without Using Always Block 1) convert first assign into initial begin clk = 0; In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Forever # (cycle/2) clk = ~clk. If you want to model a clock you can: In general, if we are working on a sequential circuit, say a flip flop. Clock Generator Without Using Always Block.

From www.youtube.com

rangkaian clock generator ic ne555 1hz YouTube Clock Generator Without Using Always Block In general, if we are working on a sequential circuit, say a flip flop (e.g. 2) second assign to always. If you want to model a clock you can: 1) convert first assign into initial begin clk = 0; Forever # (cycle/2) clk = ~clk. The difference between forever and always is that always can exist as a module item,. Clock Generator Without Using Always Block.

From www.youtube.com

How to generate PWM waveform using 555 timer Gate Pulse Generator Clock Generator Without Using Always Block So i would say a synth module would be using a simple counter. End it will only run when clk is high, since you have. 2) second assign to always. Forever # (cycle/2) clk = ~clk. Always@(clk) begin clk = 1; To give you an idea: The following verilog clock generator module has three parameters to tweak the three different. Clock Generator Without Using Always Block.

From www.researchgate.net

Schematic of the clock generator. Download Scientific Diagram Clock Generator Without Using Always Block If you want to model a clock you can: 2) second assign to always. The problem is with this block: Forever # (cycle/2) clk = ~clk. 1) convert first assign into initial begin clk = 0; So i would say a synth module would be using a simple counter. The following verilog clock generator module has three parameters to tweak. Clock Generator Without Using Always Block.

From www.mdpi.com

Electronics Free FullText A 500 kHz to 150 MHz MultiOutput Clock Clock Generator Without Using Always Block The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. D flip flop) the code we write for the always block part is:. Forever # (cycle/2) clk = ~clk. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above.. Clock Generator Without Using Always Block.

From www.youtube.com

Clock generator key parameters and specifications YouTube Clock Generator Without Using Always Block Always@(clk) begin clk = 1; To give you an idea: In general, if we are working on a sequential circuit, say a flip flop (e.g. Forever # (cycle/2) clk = ~clk. D flip flop) the code we write for the always block part is:. 1) convert first assign into initial begin clk = 0; The difference between forever and always. Clock Generator Without Using Always Block.

From www.youtube.com

How to install the Clock Generator on the GBS8200 YouTube Clock Generator Without Using Always Block So i would say a synth module would be using a simple counter. In general, if we are working on a sequential circuit, say a flip flop (e.g. D flip flop) the code we write for the always block part is:. Forever # (cycle/2) clk = ~clk. If you want to model a clock you can: To give you an. Clock Generator Without Using Always Block.

From circuitscheme.com

1 Hz Clock Generator Circuit Document Circuit Scheme Clock Generator Without Using Always Block The problem is with this block: 2) second assign to always. If you want to model a clock you can: Forever # (cycle/2) clk = ~clk. Always@(clk) begin clk = 1; The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. So i would say a synth. Clock Generator Without Using Always Block.

From learn.sparkfun.com

SparkFun Clock Generator 5P49V60 (Qwiic) Hookup Guide SparkFun Learn Clock Generator Without Using Always Block If you want to model a clock you can: D flip flop) the code we write for the always block part is:. The problem is with this block: The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. In general, if we are working on a sequential. Clock Generator Without Using Always Block.

From www.prnewswire.com

IDT Launches UltraLowPower Miniature Programmable Clock Generator for Clock Generator Without Using Always Block End it will only run when clk is high, since you have. In general, if we are working on a sequential circuit, say a flip flop (e.g. If you want to model a clock you can: 1) convert first assign into initial begin clk = 0; The difference between forever and always is that always can exist as a module. Clock Generator Without Using Always Block.

From miscircuitos.com

Clock Generator in a FPGA Full code Clock Generator Without Using Always Block The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. In general, if we are working on a sequential circuit, say a flip flop (e.g. The problem is with this block: 1) convert first assign into initial begin clk = 0; The following verilog clock generator module. Clock Generator Without Using Always Block.

From blog.tindie.com

Tindie Blog Beginner Friendly Clock Generator Kit Offers an Clock Generator Without Using Always Block The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. 1) convert first assign into initial begin clk = 0; The problem is with this block: In general, if we are working on a sequential circuit, say a flip flop (e.g. The following verilog clock generator module. Clock Generator Without Using Always Block.

From guidepartgainsays.z21.web.core.windows.net

Clock Generator Using 555 Timer Clock Generator Without Using Always Block Write a clock generator without using always block. End it will only run when clk is high, since you have. The difference between forever and always is that always can exist as a module item, which is the name that the verilog spec. So i would say a synth module would be using a simple counter. To give you an. Clock Generator Without Using Always Block.