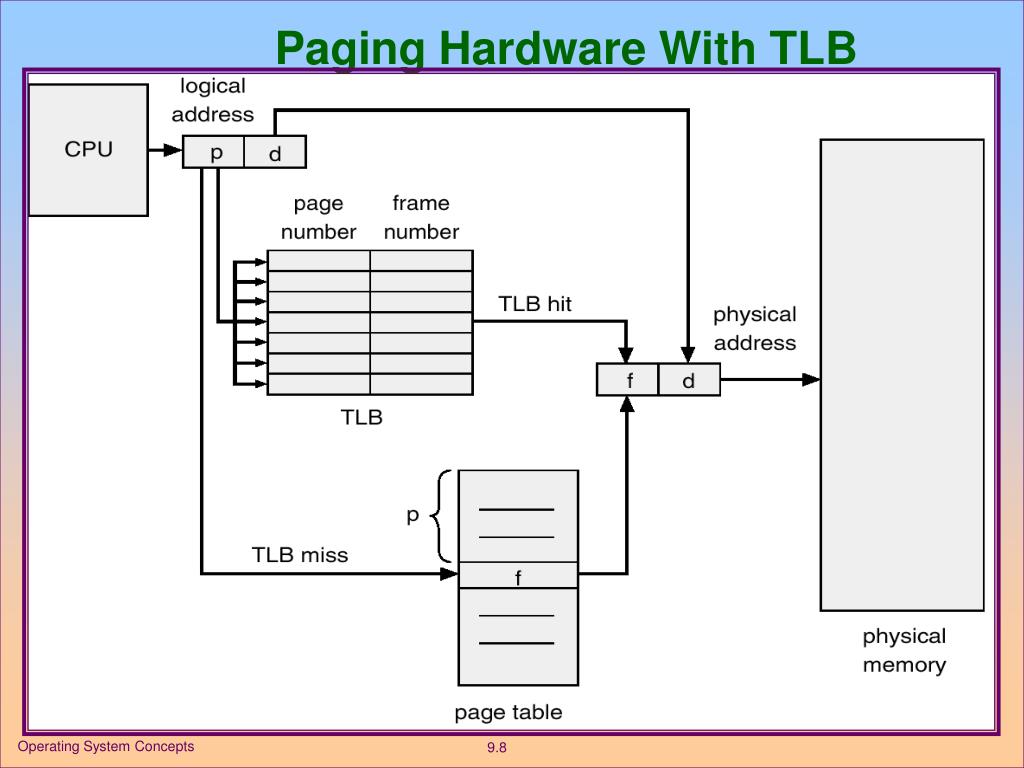

Explain Paging Hardware With Tlb . translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. paging hardware with tlb. Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. Memory protection implemented by associating protection bit with each. “load cr3” (load page table base) flushes tlb. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. what happens to tlb on context switches? It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Tlb contains page table entries that have been most recently used.

from www.slideserve.com

Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. what happens to tlb on context switches? Memory protection implemented by associating protection bit with each. Tlb contains page table entries that have been most recently used. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. “load cr3” (load page table base) flushes tlb. paging hardware with tlb. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again.

PPT Paging Example PowerPoint Presentation, free download ID4740759

Explain Paging Hardware With Tlb translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. paging hardware with tlb. Memory protection implemented by associating protection bit with each. Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. Tlb contains page table entries that have been most recently used. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. what happens to tlb on context switches? figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. “load cr3” (load page table base) flushes tlb. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again.

From www.slideserve.com

PPT Chapter 8 MemoryManagement Strategies PowerPoint Presentation Explain Paging Hardware With Tlb a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. “load. Explain Paging Hardware With Tlb.

From www.cs.uic.edu

Operating Systems Main Memory Explain Paging Hardware With Tlb It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. “load cr3” (load page table base) flushes tlb. Memory protection implemented by associating protection bit with each. paging hardware with tlb. translation lookaside buffer (tlb) is a special cache. Explain Paging Hardware With Tlb.

From www.youtube.com

CST 206 MOD 4 PART 13 Paging Hardware with TLB YouTube Explain Paging Hardware With Tlb Tlb contains page table entries that have been most recently used. Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. It is a. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb “load cr3” (load page table base) flushes tlb. what happens to tlb on context switches? Tlb contains page table entries that have been most recently used. Memory protection implemented by associating protection bit with each. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb what happens to tlb on context switches? a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Tlb contains page table entries that have been most recently used. paging hardware with tlb. It is a memory cache which. Explain Paging Hardware With Tlb.

From jhi93.github.io

Memory Management2 HAEIN Explain Paging Hardware With Tlb a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Tlb contains page table entries that have been most recently used. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Translation Lookaside Buffer(TLB) PowerPoint Presentation, free Explain Paging Hardware With Tlb paging hardware with tlb. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Tlb contains page table entries that have been most recently used. “load cr3” (load page table base) flushes tlb. translation lookaside buffer (tlb) is a. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. Tlb contains page table entries that have been most recently used. Given a virtual. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. paging hardware with tlb. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. paging hardware with tlb. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. Memory protection implemented by associating protection bit with each. Tlb contains page table entries that have been. Explain Paging Hardware With Tlb.

From www.gatevidyalay.com

Translation Lookaside Buffer TLB Paging Gate Vidyalay Explain Paging Hardware With Tlb Tlb contains page table entries that have been most recently used. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. what happens to tlb on context switches? Given a virtual address, the processor examines the tlb if a page. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging PowerPoint Presentation, free download ID4800002 Explain Paging Hardware With Tlb a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Tlb contains page table entries that have been most recently used. what happens to tlb on context switches? paging hardware with tlb. figure 19.1 shows a rough. Explain Paging Hardware With Tlb.

From www.youtube.com

Memory management Part 4 Hardware Support for Paging TLB YouTube Explain Paging Hardware With Tlb translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. “load cr3” (load page table base) flushes tlb. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. paging hardware with tlb. Tlb contains page table entries that have been most. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Example PowerPoint Presentation, free download ID4740759 Explain Paging Hardware With Tlb Memory protection implemented by associating protection bit with each. what happens to tlb on context switches? translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. “load cr3” (load page table base) flushes tlb. Tlb contains page table entries that have been most recently used. figure 19.1 shows a rough sketch. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging PowerPoint Presentation, free download ID4800002 Explain Paging Hardware With Tlb Memory protection implemented by associating protection bit with each. what happens to tlb on context switches? paging hardware with tlb. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Memory management PowerPoint Presentation, free download ID6165500 Explain Paging Hardware With Tlb “load cr3” (load page table base) flushes tlb. paging hardware with tlb. Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. what happens to tlb on context switches? figure 19.1 shows a rough sketch of how hardware. Explain Paging Hardware With Tlb.

From t4tutorials.com

What is TLB? Translation Lookaside Buffer in Paging Explain Paging Hardware With Tlb translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. Memory protection implemented by associating protection bit with each. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. a translation look aside. Explain Paging Hardware With Tlb.

From www.youtube.com

L43 Paging with Translation LookAside Buffer(TLB) Architecture Explain Paging Hardware With Tlb Memory protection implemented by associating protection bit with each. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. Tlb contains page table entries that have been most recently used. a translation look aside buffer can be defined as a memory cache which can be used to reduce. Explain Paging Hardware With Tlb.

From slidetodoc.com

COMP 3500 Introduction to Operating Systems Paging Basic Explain Paging Hardware With Tlb paging hardware with tlb. “load cr3” (load page table base) flushes tlb. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. what happens to tlb on context switches? a translation look aside buffer can be defined as. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Memory Management PowerPoint Presentation, free download ID6028478 Explain Paging Hardware With Tlb “load cr3” (load page table base) flushes tlb. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. Given a virtual address, the processor. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb paging hardware with tlb. Tlb contains page table entries that have been most recently used. Memory protection implemented by associating protection bit with each. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. “load cr3” (load page table base) flushes tlb. It is a memory cache which is closer to the. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb Tlb contains page table entries that have been most recently used. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. “load cr3” (load page table base) flushes tlb. a translation look aside buffer can be defined as a memory. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. paging hardware with tlb. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to. Explain Paging Hardware With Tlb.

From operating-os-system.blogspot.com

OS การจัดการหน่วยความจำ (memory management) Explain Paging Hardware With Tlb what happens to tlb on context switches? “load cr3” (load page table base) flushes tlb. translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. Memory protection implemented by associating protection bit with each. It is a memory cache which is closer to the cpu and the time taken by cpu to. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. “load cr3” (load page table base) flushes tlb. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. paging. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Chapter 8 Virtual Memory PowerPoint Presentation, free download Explain Paging Hardware With Tlb what happens to tlb on context switches? figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. . Explain Paging Hardware With Tlb.

From www.slideshare.net

Implementation of page table Explain Paging Hardware With Tlb translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. what happens to tlb on context switches? “load cr3” (load page table base) flushes tlb. Tlb contains page table entries that have been most recently used. a translation look aside buffer can be defined as a memory cache which can be. Explain Paging Hardware With Tlb.

From cs4118.github.io

Translation Lookaside Buffer (TLB) COMS W4118 Operating Systems I Explain Paging Hardware With Tlb “load cr3” (load page table base) flushes tlb. Memory protection implemented by associating protection bit with each. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. figure 19.1 shows a rough sketch of how hardware might handle a. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb what happens to tlb on context switches? Memory protection implemented by associating protection bit with each. It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. figure 19.1 shows a rough sketch of how hardware might handle a virtual. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. “load cr3” (load page table base) flushes tlb. a. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. Memory protection implemented by associating protection bit with each. “load cr3” (load page table base) flushes tlb. figure 19.1 shows a rough sketch of how hardware might handle a virtual. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Chapter 8 Main Memory PowerPoint Presentation, free download Explain Paging Hardware With Tlb figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again. Given a virtual address, the processor examines the tlb. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb It is a memory cache which is closer to the cpu and the time taken by cpu to access tlb is lesser then that taken to access main memory. paging hardware with tlb. Tlb contains page table entries that have been most recently used. what happens to tlb on context switches? figure 19.1 shows a rough sketch. Explain Paging Hardware With Tlb.

From www.youtube.com

Paging Hardware With TLB Translation Lookaside Buffer L6 Unit 4 Explain Paging Hardware With Tlb Memory protection implemented by associating protection bit with each. figure 19.1 shows a rough sketch of how hardware might handle a virtual address translation, assuming a simple linear page. a translation look aside buffer can be defined as a memory cache which can be used to reduce the time taken to access the page table again and again.. Explain Paging Hardware With Tlb.

From www.slideserve.com

PPT Paging Hardware With TLB PowerPoint Presentation, free download Explain Paging Hardware With Tlb translation lookaside buffer (tlb) is a special cache used to keep track of recently used transactions. Given a virtual address, the processor examines the tlb if a page table entry is present (tlb hit), the frame number is retrieved and the real address is formed. paging hardware with tlb. Tlb contains page table entries that have been most. Explain Paging Hardware With Tlb.