Load And Store Instructions In Risc . The specification now allows visible misaligned address traps in. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. •changed description of misaligned load and store behavior. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. • amos and lr/sc can. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. All internal cpu units use registers for input and. Aimed at software developers, it groups instructions by purpose and includes.

from cepdnaclk.github.io

•changed description of misaligned load and store behavior. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. Aimed at software developers, it groups instructions by purpose and includes. All internal cpu units use registers for input and. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. • amos and lr/sc can. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The specification now allows visible misaligned address traps in.

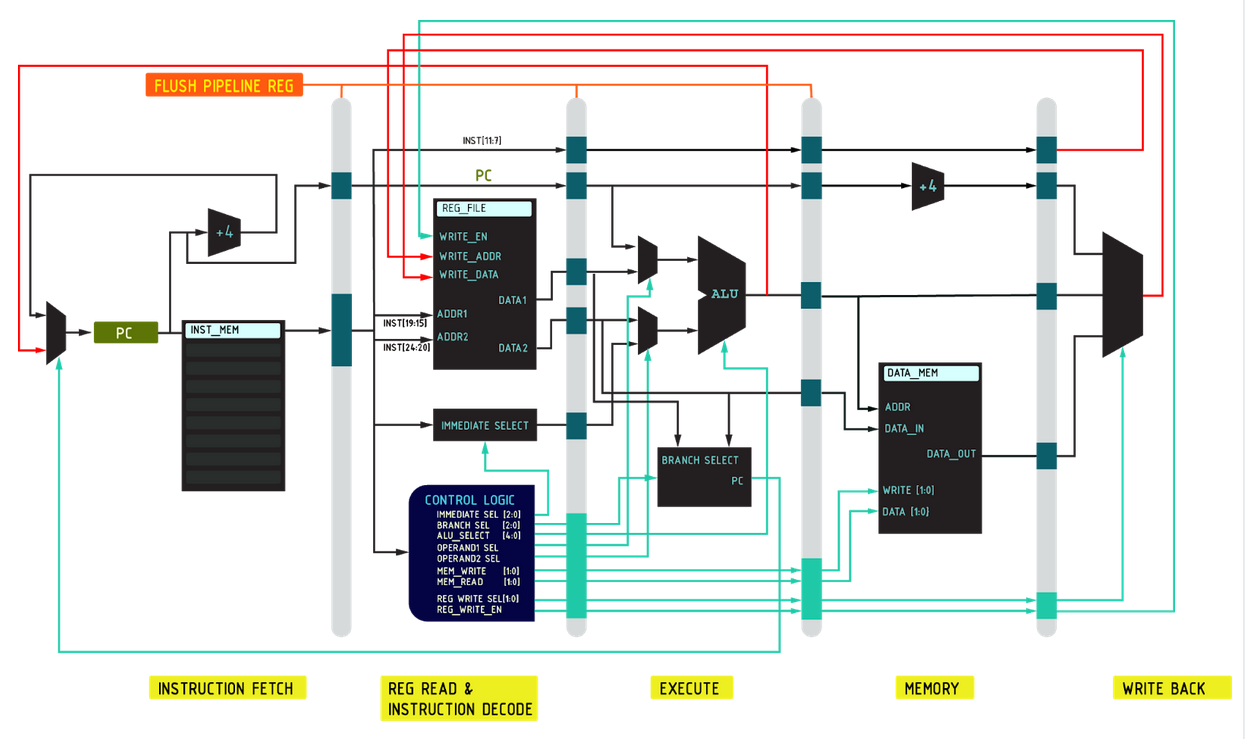

RISCV 32 bit CPU

Load And Store Instructions In Risc The specification now allows visible misaligned address traps in. Aimed at software developers, it groups instructions by purpose and includes. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. • amos and lr/sc can. •changed description of misaligned load and store behavior. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. All internal cpu units use registers for input and. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. The specification now allows visible misaligned address traps in.

From cepdnaclk.github.io

RISCV 32 bit CPU Load And Store Instructions In Risc • amos and lr/sc can. •changed description of misaligned load and store behavior. All internal cpu units use registers for input and. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. Aimed at software developers, it groups instructions by purpose and includes. Load / store operations. Load And Store Instructions In Risc.

From www.slideserve.com

PPT Reduced Instruction Set Computer (RISC) PowerPoint Presentation Load And Store Instructions In Risc The specification now allows visible misaligned address traps in. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Aimed at software developers, it groups instructions by purpose and includes. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. All internal cpu units. Load And Store Instructions In Risc.

From itnext.io

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT Load And Store Instructions In Risc Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. •changed description of misaligned load and store behavior. The specification now allows visible misaligned address traps in. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. •. Load And Store Instructions In Risc.

From electronics.stackexchange.com

store word assembly instruction in riscv Electrical Engineering Load And Store Instructions In Risc Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. •changed description of misaligned load and store behavior. • amos and lr/sc can. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. All internal cpu units use registers for. Load And Store Instructions In Risc.

From www.researchgate.net

(PDF) Adding Explicit LoadAcquire and StoreRelease Instructions to Load And Store Instructions In Risc All internal cpu units use registers for input and. Aimed at software developers, it groups instructions by purpose and includes. • amos and lr/sc can. The specification now allows visible misaligned address traps in. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. •changed description of. Load And Store Instructions In Risc.

From www.slideserve.com

PPT Reduced Instruction Set Computer (RISC) PowerPoint Presentation Load And Store Instructions In Risc All internal cpu units use registers for input and. Aimed at software developers, it groups instructions by purpose and includes. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Risc instruction set computers. Load And Store Instructions In Risc.

From www.slideserve.com

PPT Reduced Instruction Set Computer (RISC) PowerPoint Presentation Load And Store Instructions In Risc Aimed at software developers, it groups instructions by purpose and includes. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. • amos and lr/sc can. •changed description of misaligned load and store behavior. The load/store unit (lsu) is responsible for deciding when to fire memory operations. Load And Store Instructions In Risc.

From www.chegg.com

Solved Compile C to RISCV assembly code. Instructions that Load And Store Instructions In Risc All internal cpu units use registers for input and. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The specification now allows visible misaligned address traps in. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers.. Load And Store Instructions In Risc.

From www.youtube.com

Lecture 23. Load and Store Instructions YouTube Load And Store Instructions In Risc Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. • amos and lr/sc can. The specification now allows visible misaligned address traps in. Aimed at software developers, it groups instructions by purpose and includes. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory. Load And Store Instructions In Risc.

From www.mdpi.com

Electronics Free FullText RISCVlim, a RISCV Framework for Logic Load And Store Instructions In Risc Aimed at software developers, it groups instructions by purpose and includes. All internal cpu units use registers for input and. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data. Load And Store Instructions In Risc.

From projectf.io

RISCV Assembler Load Store Project F Load And Store Instructions In Risc The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Aimed at software developers, it groups instructions by purpose and includes. The specification now allows visible misaligned address traps in. •changed description of misaligned load and store behavior. • amos and lr/sc can. Risc instruction set computers do not allow all instructions to. Load And Store Instructions In Risc.

From www.slideserve.com

PPT The RISCV Processor PowerPoint Presentation, free download ID Load And Store Instructions In Risc The specification now allows visible misaligned address traps in. All internal cpu units use registers for input and. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. • amos and lr/sc can. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Risc. Load And Store Instructions In Risc.

From itnext.io

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT Load And Store Instructions In Risc Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. •changed description of misaligned load and store behavior. Aimed at software developers, it groups instructions by purpose and includes. All internal cpu units use registers for input and. Load / store operations mnemonic instruction type description ld. Load And Store Instructions In Risc.

From www.chegg.com

Solved Consider the execution of a program that results in Load And Store Instructions In Risc The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Aimed at software developers, it groups instructions by purpose and includes. All internal cpu units use registers for input and. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers.. Load And Store Instructions In Risc.

From www.scribd.com

Load, Store, and Pseudo Instructions for the RISCV Instruction Set Load And Store Instructions In Risc Aimed at software developers, it groups instructions by purpose and includes. The specification now allows visible misaligned address traps in. •changed description of misaligned load and store behavior. All internal cpu units use registers for input and. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Load / store operations mnemonic instruction. Load And Store Instructions In Risc.

From www.youtube.com

03 ARM CortexM Load/Store Instructions YouTube Load And Store Instructions In Risc Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. •changed description of misaligned load and store behavior. The load/store unit (lsu) is responsible for deciding when to. Load And Store Instructions In Risc.

From slideplayer.com

ARM Load/Store Instructions ppt download Load And Store Instructions In Risc All internal cpu units use registers for input and. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. Aimed at software developers, it groups instructions by purpose and includes.. Load And Store Instructions In Risc.

From docs.openhwgroup.org

Introduction — COREV CV32E40P User Manual v1.8.3 documentation Load And Store Instructions In Risc All internal cpu units use registers for input and. The specification now allows visible misaligned address traps in. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers.. Load And Store Instructions In Risc.

From slideplayer.com

Electrical and Computer Engineering ppt download Load And Store Instructions In Risc All internal cpu units use registers for input and. •changed description of misaligned load and store behavior. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Aimed at software developers, it groups instructions. Load And Store Instructions In Risc.

From devopedia.org

RISCV Instruction Sets Load And Store Instructions In Risc The specification now allows visible misaligned address traps in. Aimed at software developers, it groups instructions by purpose and includes. All internal cpu units use registers for input and. •changed description of misaligned load and store behavior. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The load/store unit (lsu). Load And Store Instructions In Risc.

From www.researchgate.net

LOAD/STORE instruction scheduling (LSQueue and LSBuffer) Download Load And Store Instructions In Risc The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. •changed description of misaligned load and store behavior. Aimed at software developers, it groups instructions by purpose and includes. •. Load And Store Instructions In Risc.

From eng.libretexts.org

4.4 Load and Store Architecture Engineering LibreTexts Load And Store Instructions In Risc All internal cpu units use registers for input and. Aimed at software developers, it groups instructions by purpose and includes. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The specification now allows visible misaligned address traps in. Risc instruction set computers do not allow all instructions to access memory,. Load And Store Instructions In Risc.

From www.youtube.com

Implementing Store Instructions RISCV part 4 YouTube Load And Store Instructions In Risc •changed description of misaligned load and store behavior. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. All internal cpu units use registers for input and. The specification now allows visible misaligned address. Load And Store Instructions In Risc.

From www.slideserve.com

PPT Lecture 4 Load/Store Architectures PowerPoint Presentation, free Load And Store Instructions In Risc Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The specification now allows visible misaligned address traps in. • amos and lr/sc can. •changed description of misaligned load and store behavior. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and. Load And Store Instructions In Risc.

From exoxjvzws.blob.core.windows.net

Risc V Architecture Block Diagram at Susan Hornbeck blog Load And Store Instructions In Risc All internal cpu units use registers for input and. •changed description of misaligned load and store behavior. The specification now allows visible misaligned address traps in. • amos and lr/sc can. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. Load / store operations mnemonic instruction. Load And Store Instructions In Risc.

From rumble.com

RiscV Load Store Instructions Load And Store Instructions In Risc The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. •. Load And Store Instructions In Risc.

From www.slideserve.com

PPT RISC / CISC Architecture PowerPoint Presentation, free download Load And Store Instructions In Risc • amos and lr/sc can. All internal cpu units use registers for input and. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. The specification now allows visible misaligned address traps in. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. •changed. Load And Store Instructions In Risc.

From semiwiki.com

Is your career at RISK without RISCV? SemiWiki Load And Store Instructions In Risc Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The specification now allows visible misaligned address traps in. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. All internal cpu units use registers for input and. • amos and lr/sc can. Aimed. Load And Store Instructions In Risc.

From electronics.stackexchange.com

memory RISCV byte load and store Electrical Engineering Stack Exchange Load And Store Instructions In Risc •changed description of misaligned load and store behavior. • amos and lr/sc can. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. All internal cpu units use registers for. Load And Store Instructions In Risc.

From joijinrko.blob.core.windows.net

Store Instruction Vs Load at Nelson McClellan blog Load And Store Instructions In Risc The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. All internal cpu units use registers for input and. • amos and lr/sc can. Risc instruction set computers do not allow all instructions to. Load And Store Instructions In Risc.

From itnext.io

RISCV InstructionSet Cheatsheet by Erik Engheim ITNEXT Load And Store Instructions In Risc The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. • amos and lr/sc can. Risc instruction set computers do not allow all instructions to access memory, but have special operations to load and store data to registers. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd. Load And Store Instructions In Risc.

From deepai.org

Adding Explicit LoadAcquire and StoreRelease Instructions to the RISC Load And Store Instructions In Risc All internal cpu units use registers for input and. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. Aimed at software developers, it groups instructions by purpose and includes. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. • amos and lr/sc. Load And Store Instructions In Risc.

From www.slideserve.com

PPT The RISCV Processor PowerPoint Presentation, free download ID Load And Store Instructions In Risc Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. •changed description of misaligned load and store behavior. The specification now allows visible misaligned address traps in. Risc instruction set computers do not allow. Load And Store Instructions In Risc.

From docs.boom-core.org

The Load/Store Unit (LSU) — RISCVBOOM documentation Load And Store Instructions In Risc Aimed at software developers, it groups instructions by purpose and includes. All internal cpu units use registers for input and. The load/store unit (lsu) is responsible for deciding when to fire memory operations to the memory system. • amos and lr/sc can. •changed description of misaligned load and store behavior. Risc instruction set computers do not allow all instructions to. Load And Store Instructions In Risc.

From www.slideserve.com

PPT The RISCV Processor PowerPoint Presentation, free download ID Load And Store Instructions In Risc •changed description of misaligned load and store behavior. Load / store operations mnemonic instruction type description ld rd, imm12(rs1) load doubleword i rd ← mem[rs1 + imm12]. The specification now allows visible misaligned address traps in. Aimed at software developers, it groups instructions by purpose and includes. Risc instruction set computers do not allow all instructions to access memory, but. Load And Store Instructions In Risc.