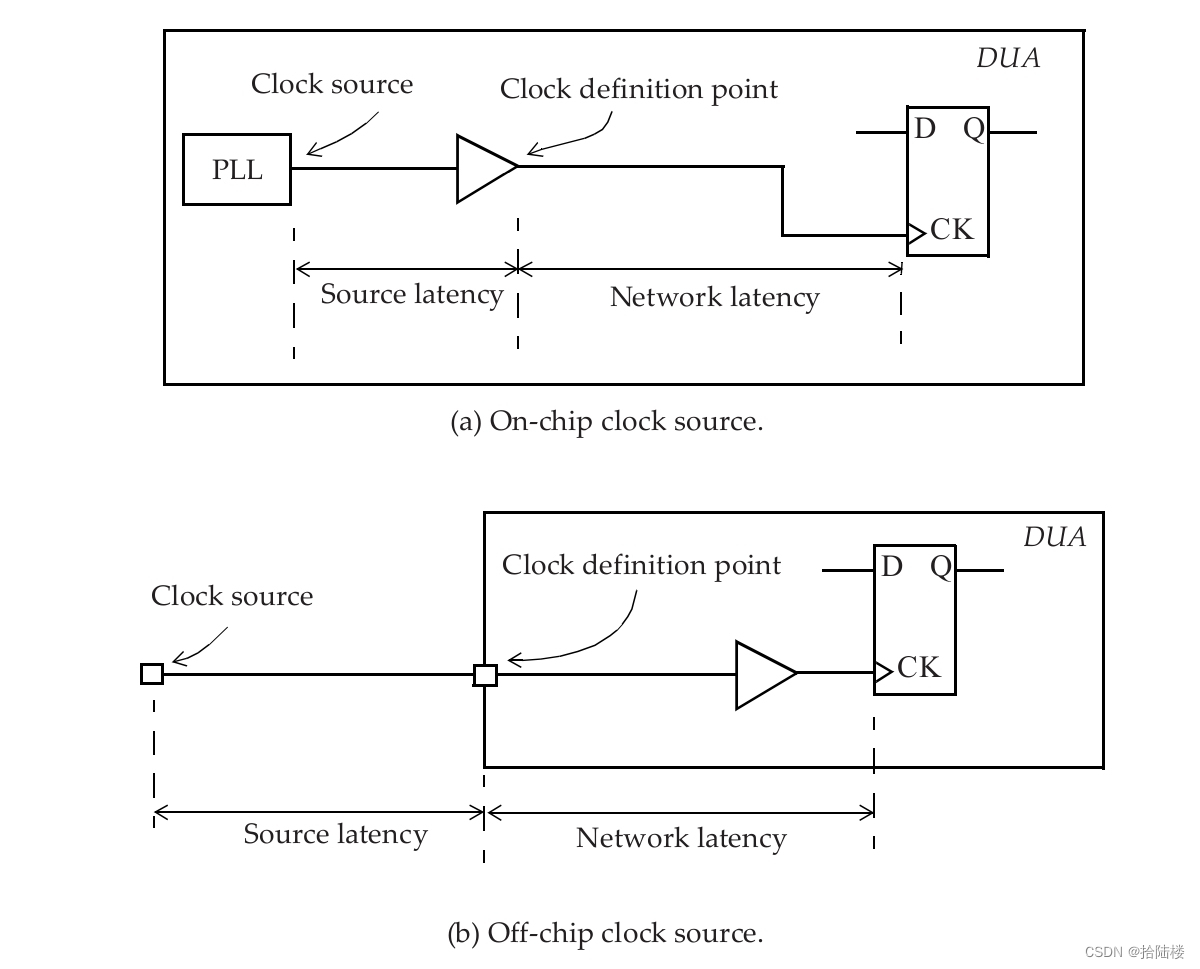

Open Edge Clock Latency . The time borrowing technique, is also called cycle stealing, occurs at a latch. What is timing borrowing concept? Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. In a latch, one edge of the clock makes the latch. Factors affecting edge positions of capture clock. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. Open vs close edge clock network. Library setup constraint of endpoint latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Clock skew can also be termed as the difference between the.

from blog.csdn.net

Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. In a latch, one edge of the clock makes the latch. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Library setup constraint of endpoint latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. The time borrowing technique, is also called cycle stealing, occurs at a latch. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. Clock skew can also be termed as the difference between the. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Factors affecting edge positions of capture clock.

静态时序分析—时钟延时(Clock Latency)CSDN博客

Open Edge Clock Latency The time borrowing technique, is also called cycle stealing, occurs at a latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. What is timing borrowing concept? Factors affecting edge positions of capture clock. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. Clock skew can also be termed as the difference between the. The time borrowing technique, is also called cycle stealing, occurs at a latch. Open vs close edge clock network. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Library setup constraint of endpoint latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. In a latch, one edge of the clock makes the latch.

From edupepper.com

How does edge computing reduce latency for end user? Open Edge Clock Latency Open vs close edge clock network. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. The time borrowing technique, is also called cycle stealing, occurs at a latch. Clock latency is the time delay seen between the clock edges of the clock signal at. Open Edge Clock Latency.

From siliconvlsi.com

Difference Between Clock Skew and Uncertainty Siliconvlsi Open Edge Clock Latency Library setup constraint of endpoint latch. What is timing borrowing concept? The time borrowing technique, is also called cycle stealing, occurs at a latch. Clock skew can also be termed as the difference between the. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Factors affecting edge. Open Edge Clock Latency.

From kkinsider.com

How Does Edge Computing Reduce Latency for End Users? KKinsider Open Edge Clock Latency In a latch, one edge of the clock makes the latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Open vs close edge clock network. Clock skew can also be termed as the difference between the. Experience the orbit ddr memory controller's exceptional performance,. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency What is timing borrowing concept? The time borrowing technique, is also called cycle stealing, occurs at a latch. Clock skew can also be termed as the difference between the. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. The launch edge of the clock signal. Open Edge Clock Latency.

From vercel.com

Regional execution for ultralow latency rendering at the edge Vercel Open Edge Clock Latency The time borrowing technique, is also called cycle stealing, occurs at a latch. What is timing borrowing concept? In a latch, one edge of the clock makes the latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Factors affecting edge positions of capture clock.. Open Edge Clock Latency.

From blogs.cuit.columbia.edu

Check clock gating Open Edge Clock Latency Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Clock skew can also be termed as the difference between the. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Factors affecting edge positions of capture clock. What is timing borrowing concept? Open vs. Open Edge Clock Latency.

From www.hitbrother.com

Edge Computing Real Time Extension In Processing Data HitBrother Open Edge Clock Latency Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Factors affecting edge positions of capture clock. Library setup constraint of endpoint latch. In a latch, one edge of the clock makes the latch. What is timing borrowing concept? Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to. Open Edge Clock Latency.

From rebeccajosephblogs.blogspot.com

how does edge computing reduce latency for end users Open Edge Clock Latency The time borrowing technique, is also called cycle stealing, occurs at a latch. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Library setup constraint of endpoint latch. In a latch, one edge of the clock makes the latch. What is timing borrowing concept? Open vs close edge clock network. The time taken by clock signal. Open Edge Clock Latency.

From www.youtube.com

Clock Latency Slew Constraints YouTube Open Edge Clock Latency Factors affecting edge positions of capture clock. The time borrowing technique, is also called cycle stealing, occurs at a latch. Open vs close edge clock network. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Clock latency, also known as clock insertion delay, refers to the time. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency In a latch, one edge of the clock makes the latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Clock latency is the time delay seen between. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. In a latch, one edge of the clock makes the latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Open vs close. Open Edge Clock Latency.

From github.com

GitHub LatencyAware Edge Open Edge Clock Latency Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. What is timing borrowing concept? In a latch, one edge of the clock makes the latch. Factors affecting edge positions of capture clock. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the.. Open Edge Clock Latency.

From blogs.cuit.columbia.edu

Clock Tree Latency Skew Uncertainty Open Edge Clock Latency Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Library setup constraint of endpoint latch. Clock skew can also be termed as the difference between the. The time borrowing technique, is also called cycle stealing, occurs at a latch. Experience the orbit ddr memory controller's. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Library setup constraint of endpoint latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Clock skew. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency The time borrowing technique, is also called cycle stealing, occurs at a latch. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Library setup constraint of endpoint latch. In a latch, one edge of. Open Edge Clock Latency.

From www.edgeir.com

Wiwynn to show low latency edge applications for 5G on Open Compute Open Edge Clock Latency Open vs close edge clock network. Library setup constraint of endpoint latch. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Clock skew can also be termed as. Open Edge Clock Latency.

From www.researchgate.net

2 Active level gating with clockedge interrupt latency of 9 to 40 µs Open Edge Clock Latency What is timing borrowing concept? The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. In a latch,. Open Edge Clock Latency.

From www.omgkrk.com

Apply For Hubraum Low Latency Prototyping Program Edge Computing and Open Edge Clock Latency Library setup constraint of endpoint latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. The time borrowing technique,. Open Edge Clock Latency.

From www.pinterest.com

Reduce latency and increase network efficiency with MultiAccess Edge Open Edge Clock Latency Open vs close edge clock network. In a latch, one edge of the clock makes the latch. Factors affecting edge positions of capture clock. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Library. Open Edge Clock Latency.

From www.slideserve.com

PPT STATIC TIMING ANALYSIS PowerPoint Presentation, free download Open Edge Clock Latency The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. Experience the orbit ddr memory controller's exceptional. Open Edge Clock Latency.

From www.heavy.ai

What is Edge Network? Definition and FAQs HEAVY.AI Open Edge Clock Latency In a latch, one edge of the clock makes the latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its. Open Edge Clock Latency.

From github.com

GitHub LinkedInLearning/achievinglowlatencydatawithedge Open Edge Clock Latency Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. The time borrowing technique, is also called cycle. Open Edge Clock Latency.

From vercel.com

Regional execution for ultralow latency rendering at the edge Vercel Open Edge Clock Latency In a latch, one edge of the clock makes the latch. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. What is timing borrowing concept? The launch edge of the clock. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency In a latch, one edge of the clock makes the latch. Library setup constraint of endpoint latch. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Clock skew can also be termed as the difference between the. Factors affecting edge positions of capture clock. The time borrowing. Open Edge Clock Latency.

From www.chtips.com

How Does Edge Computing Reduce Latency For End Users 4 Types Open Edge Clock Latency Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Factors affecting edge positions of capture clock. What is timing borrowing concept? Library setup constraint of endpoint latch. Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. The launch edge of the clock signal. Open Edge Clock Latency.

From www.reply.com

Low Latency what makes 5G different Reply Open Edge Clock Latency In a latch, one edge of the clock makes the latch. Library setup constraint of endpoint latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Factors affecting edge positions of capture clock. Open vs close edge clock network. Experience the orbit ddr memory controller's. Open Edge Clock Latency.

From blog.csdn.net

PT的一些setting_open edge clock latencyCSDN博客 Open Edge Clock Latency What is timing borrowing concept? The time borrowing technique, is also called cycle stealing, occurs at a latch. Clock skew can also be termed as the difference between the. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Open vs close. Open Edge Clock Latency.

From www.researchgate.net

Latency optimization in a positive edge triggered Dflip flop (1 Open Edge Clock Latency Library setup constraint of endpoint latch. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. In a latch, one edge of the clock makes the latch. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Open vs. Open Edge Clock Latency.

From copyprogramming.com

Synthesis SDC constraints for source clock and derived clock Open Edge Clock Latency Library setup constraint of endpoint latch. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. In a latch, one edge of the clock makes the latch. Factors affecting edge positions of capture clock. Clock latency is the time delay seen between the clock edges. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency The time borrowing technique, is also called cycle stealing, occurs at a latch. Open vs close edge clock network. Library setup constraint of endpoint latch. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. In a latch, one edge of the clock makes the latch.. Open Edge Clock Latency.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Open Edge Clock Latency The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as a source for. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel. Open Edge Clock Latency.

From asicpd.blogspot.com

ASIC Physical design Static Timing Analysis Open Edge Clock Latency The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. What is timing borrowing concept? Library setup constraint of endpoint latch. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. Clock latency is the time delay seen between the clock edges. Open Edge Clock Latency.

From capalearning.com

How Does Edge Computing Reduce Latency? Capa Learning Open Edge Clock Latency Clock latency, also known as clock insertion delay, refers to the time taken by the clock signal to travel from its source to the. Clock skew can also be termed as the difference between the. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency.. Open Edge Clock Latency.

From siliconvlsi.com

What do you mean by clock Jitter? Siliconvlsi Open Edge Clock Latency Open vs close edge clock network. Clock skew can also be termed as the difference between the. In a latch, one edge of the clock makes the latch. The time taken by clock signal to reach from clock source to the clock pin of a particular flip flop is called as clock latency. The time borrowing technique, is also called. Open Edge Clock Latency.

From blog.csdn.net

静态时序分析—时钟延时(Clock Latency)CSDN博客 Open Edge Clock Latency Clock latency is the time delay seen between the clock edges of the clock signal at its source of generation and the. Experience the orbit ddr memory controller's exceptional performance, high utilization, and low latency. The launch edge of the clock signal is the clock edge that sends data out of a register or other sequential element, and acts as. Open Edge Clock Latency.