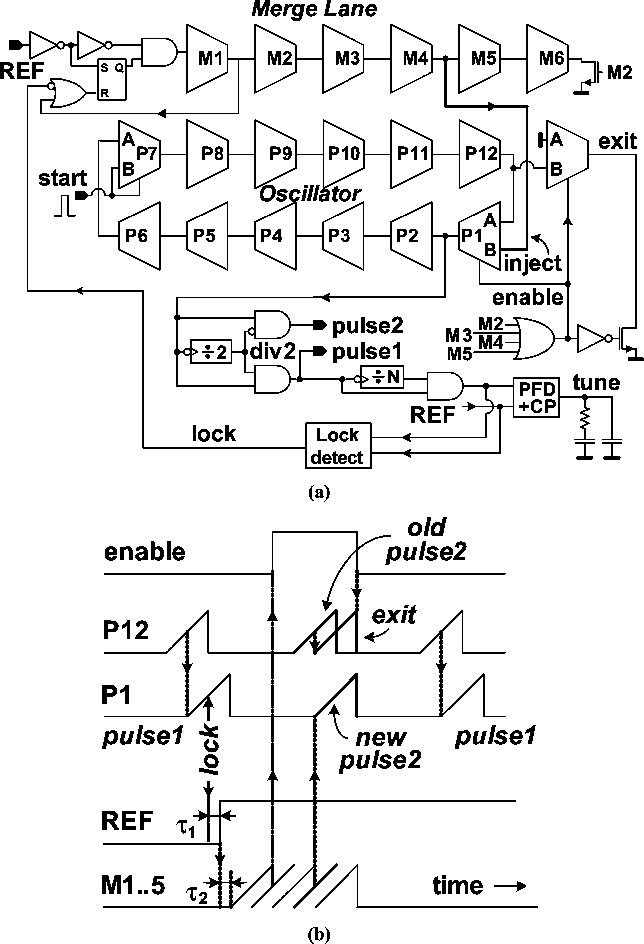

Clock Multiplier Concept . Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. The dll is used to “delay” synchronize the system clock to a reference clock. The clock multiplier is a clock signal with a frequency ×𝑓. A cpu multiplier of 46 and a base clock of 100. •the output clock will have. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. •where is the multiplication factor of the clock multiplier. For instance, a cpu running at 2.66. A clock multiplier was designed in the topology given in figure 4. Some high performance systems use a.

from www.semanticscholar.org

•the output clock will have. The dll is used to “delay” synchronize the system clock to a reference clock. For instance, a cpu running at 2.66. •where is the multiplication factor of the clock multiplier. Some high performance systems use a. A clock multiplier was designed in the topology given in figure 4. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. A cpu multiplier of 46 and a base clock of 100. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. The clock multiplier is a clock signal with a frequency ×𝑓.

Figure 1 from LowSpur, LowPhaseNoise Clock Multiplier Based on a

Clock Multiplier Concept The dll is used to “delay” synchronize the system clock to a reference clock. For instance, a cpu running at 2.66. The dll is used to “delay” synchronize the system clock to a reference clock. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. Some high performance systems use a. A clock multiplier was designed in the topology given in figure 4. The clock multiplier is a clock signal with a frequency ×𝑓. A cpu multiplier of 46 and a base clock of 100. •where is the multiplication factor of the clock multiplier. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. •the output clock will have.

From www.semanticscholar.org

A LowJitter and FractionalResolution InjectionLocked Clock Clock Multiplier Concept •the output clock will have. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. Some high performance systems use a. The dll is used to “delay” synchronize the system clock to a reference clock. A clock multiplier was designed in the topology given in figure 4.. Clock Multiplier Concept.

From www.bummbummgarage.com

Clock Multiplier Bumm Bumm Garage Clock Multiplier Concept The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. •the output clock will have. A cpu multiplier of 46 and a base clock. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 3 from A Digital Clock Multiplier for Globally Asynchronous Clock Multiplier Concept For instance, a cpu running at 2.66. •where is the multiplication factor of the clock multiplier. The dll is used to “delay” synchronize the system clock to a reference clock. A clock multiplier was designed in the topology given in figure 4. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal. Clock Multiplier Concept.

From www.researchgate.net

Conceptual MDLL clock multiplier and impact of tuning voltage on its Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. A clock multiplier was designed in the topology given in figure 4. A cpu multiplier of 46 and a base clock of 100. Some high performance systems use a. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 1 from AllDigital Baseband 65 nm PLL / FPLL Clock Multiplier Clock Multiplier Concept The clock multiplier is a clock signal with a frequency ×𝑓. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. The dll is used to “delay” synchronize the system clock to a reference clock. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance. Clock Multiplier Concept.

From www.mdpi.com

Electronics Free FullText A Fast LockIn Time, Capacitive FIR Clock Multiplier Concept Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. •where is the multiplication factor of the clock multiplier. A clock multiplier was designed in the topology given in figure 4. Some high performance systems use a. •the output clock will have. The dll. Clock Multiplier Concept.

From www.youtube.com

DIY Clock Multiplier ️(модуль на основе Attiny85) своими руками YouTube Clock Multiplier Concept The clock multiplier is a clock signal with a frequency ×𝑓. For instance, a cpu running at 2.66. •the output clock will have. A cpu multiplier of 46 and a base clock of 100. Some high performance systems use a. The dll is used to “delay” synchronize the system clock to a reference clock. •where is the multiplication factor of. Clock Multiplier Concept.

From www.youtube.com

Shuffling Clock Multiplier YouTube Clock Multiplier Concept Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. The clock multiplier is a clock signal with a frequency ×𝑓. For instance, a cpu running at 2.66. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of. Clock Multiplier Concept.

From www.researchgate.net

(PDF) Lowjitter clock multiplication A comparison between PLLs and DLLs Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. For instance, a cpu running at 2.66. A clock multiplier was designed in the topology given in figure 4. •the output clock will have. The clock multiplier is a clock signal with a frequency ×𝑓. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares. Clock Multiplier Concept.

From www.academia.edu

(PDF) A 33mW 8Gb/s CMOS clock multiplier and CDR for highly integrated Clock Multiplier Concept The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. •the output clock will have. •where is the multiplication factor of the clock multiplier. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the. Clock Multiplier Concept.

From www.researchgate.net

(PDF) Lowjitter clock multiplication A comparison between PLLs and DLLs Clock Multiplier Concept A cpu multiplier of 46 and a base clock of 100. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. A clock multiplier was designed in the topology given in figure 4. •the output clock will have. Also known as the clock ratio, cpu core ratio,. Clock Multiplier Concept.

From eureka.patsnap.com

Clock multiplier Eureka wisdom buds develop intelligence library Clock Multiplier Concept Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. For instance, a cpu running at 2.66. •where is the multiplication. Clock Multiplier Concept.

From www.semanticscholar.org

Table 1 from DLLbased programmable clock multiplier using differential Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. A cpu multiplier of 46 and a base clock of 100. Some high performance systems use a. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. •the output clock will have. The cpu multiplier (sometimes called the. Clock Multiplier Concept.

From www.semanticscholar.org

A 1.3cycle lock time, nonPLL/DLL clock multiplier based on direct Clock Multiplier Concept Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. For instance, a cpu running at 2.66. A cpu multiplier of 46 and a base clock of 100. •where is the multiplication factor of the clock multiplier. The cpu multiplier (sometimes called the “cpu. Clock Multiplier Concept.

From github.com

GitHub akilm/ClockMultiplier Clock Multiplier Concept Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. •where is the multiplication factor of the clock multiplier. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. •the output. Clock Multiplier Concept.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Multiplier Concept Some high performance systems use a. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. •where is the multiplication factor of the clock multiplier. A clock multiplier was designed in the topology given in figure 4. Also known as the clock ratio, cpu core ratio, or. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 2 from PLLless clock multiplier with selfadjusting phase Clock Multiplier Concept The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. The dll is used to “delay” synchronize the system clock to a reference clock. A clock multiplier was designed in the topology given in figure 4. In computing, the clock multiplier (or cpu multiplier or bus/core ratio). Clock Multiplier Concept.

From www.researchgate.net

Conceptual MDLL clock multiplier and impact of tuning voltage on its Clock Multiplier Concept Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. A clock multiplier was designed in the topology given in figure 4. The clock multiplier is a clock signal with a frequency ×𝑓. •the output clock will have. The cpu multiplier (sometimes called the. Clock Multiplier Concept.

From www.researchgate.net

Architecture of the clock multiplier unit. Download Scientific Diagram Clock Multiplier Concept The dll is used to “delay” synchronize the system clock to a reference clock. A clock multiplier was designed in the topology given in figure 4. •the output clock will have. The clock multiplier is a clock signal with a frequency ×𝑓. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 10 from A Highly Digital MDLLBased Clock Multiplier That Clock Multiplier Concept The dll is used to “delay” synchronize the system clock to a reference clock. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 1 from A HighPerformance Low Complexity AllDigital Fractional Clock Multiplier Concept A clock multiplier was designed in the topology given in figure 4. For instance, a cpu running at 2.66. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. The clock multiplier is a clock signal with a frequency ×𝑓. Some high performance systems use a. •the. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 1 from A Portable Clock Multiplier Generator using Digital CMOS Clock Multiplier Concept •the output clock will have. For instance, a cpu running at 2.66. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. The dll is used to “delay” synchronize the system clock to a reference clock. Also known as the clock ratio, cpu core ratio, or simply. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 1 from LowSpur, LowPhaseNoise Clock Multiplier Based on a Clock Multiplier Concept The dll is used to “delay” synchronize the system clock to a reference clock. A clock multiplier was designed in the topology given in figure 4. The clock multiplier is a clock signal with a frequency ×𝑓. •where is the multiplication factor of the clock multiplier. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio. Clock Multiplier Concept.

From dqydj.com

How to Multiply The Frequency of Digital Logic Clocks Using a PLL Clock Multiplier Concept The clock multiplier is a clock signal with a frequency ×𝑓. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. A cpu multiplier of 46 and a base clock of 100. A clock multiplier was designed in the topology given in figure 4. For instance, a. Clock Multiplier Concept.

From reverb.com

Doepfer A1605 Voltage Controlled Clock Multiplier / Reverb Clock Multiplier Concept The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. The dll is used to “delay” synchronize the system clock to a reference clock. A clock multiplier was designed in the topology given in figure 4. The clock multiplier is a clock signal with a frequency ×𝑓.. Clock Multiplier Concept.

From www.researchgate.net

Efficient design of QCA based hybrid multiplier using clock zone based Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. Some high performance systems use a. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. A cpu multiplier of 46 and a base clock of 100. For instance, a cpu running at 2.66. •the output clock will. Clock Multiplier Concept.

From blog.csdn.net

Chapter 6 Generated Clocks生成时钟_时钟乘法器CSDN博客 Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. The dll is used to “delay” synchronize the system clock to a reference clock. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a. Clock Multiplier Concept.

From www.bummbummgarage.com

Clock Multiplier Bumm Bumm Garage Clock Multiplier Concept For instance, a cpu running at 2.66. The dll is used to “delay” synchronize the system clock to a reference clock. •where is the multiplication factor of the clock multiplier. A clock multiplier was designed in the topology given in figure 4. Some high performance systems use a. Also known as the clock ratio, cpu core ratio, or simply the. Clock Multiplier Concept.

From itecnotes.com

Electronic Hall Effect pulse multiplier circuit Valuable Tech Notes Clock Multiplier Concept •the output clock will have. For instance, a cpu running at 2.66. The clock multiplier is a clock signal with a frequency ×𝑓. A clock multiplier was designed in the topology given in figure 4. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. •where is. Clock Multiplier Concept.

From www.youtube.com

Sequencing Clock Multiplier Demo YouTube Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. The clock. Clock Multiplier Concept.

From eureka.patsnap.com

Clock multiplier Eureka wisdom buds develop intelligence library Clock Multiplier Concept A cpu multiplier of 46 and a base clock of 100. The clock multiplier is a clock signal with a frequency ×𝑓. Some high performance systems use a. For instance, a cpu running at 2.66. The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. In computing,. Clock Multiplier Concept.

From lookmumnocomputer.discourse.group

Working Clock Multiplier/Divider/Phase Shifter with tolerance for Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. The dll is used to “delay” synchronize the system clock to a reference clock. The clock multiplier is a clock signal with a frequency ×𝑓. Some high performance systems use a. For instance, a cpu running at 2.66. A clock multiplier was designed in the topology given in figure 4. Also. Clock Multiplier Concept.

From www.semanticscholar.org

Figure 10 from A 2.510GHz clock multiplier unit with 0.22ps RMS Clock Multiplier Concept The cpu multiplier (sometimes called the “cpu ratio”) expresses the cpu’s performance as a multiplier of the cpu base clock (or bclk) speed. A clock multiplier was designed in the topology given in figure 4. •where is the multiplication factor of the clock multiplier. A cpu multiplier of 46 and a base clock of 100. In computing, the clock multiplier. Clock Multiplier Concept.

From vlsimaster.com

Generated Clock and Virtual Clock VLSI Master Clock Multiplier Concept The dll is used to “delay” synchronize the system clock to a reference clock. •the output clock will have. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. The clock multiplier is a clock signal with a frequency ×𝑓. For instance, a cpu. Clock Multiplier Concept.

From www.youtube.com

DIY EURORACK CLOCK DIVIDER&MULTIPLIER YouTube Clock Multiplier Concept •where is the multiplication factor of the clock multiplier. Also known as the clock ratio, cpu core ratio, or simply the multiplier, this metric compares the internal cpu clock rate to the external clock speed. In computing, the clock multiplier (or cpu multiplier or bus/core ratio) sets the ratio of an internal cpu clock rate to the externally. The dll. Clock Multiplier Concept.