Clock Generator Without Using Always Block . If you want to model a clock you can: So you can only create digital dividers with verilog. The problem is with this block: You can't create generator without external reference clock signal. Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. End it will only run when clk is high, since you have. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Always@(clk) begin clk = 1; 2) second assign to always. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. 1) convert first assign into initial begin clk = 0;

from www.mdpi.com

Always@(clk) begin clk = 1; 2) second assign to always. Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. 1) convert first assign into initial begin clk = 0; The problem is with this block: The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. End it will only run when clk is high, since you have. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes.

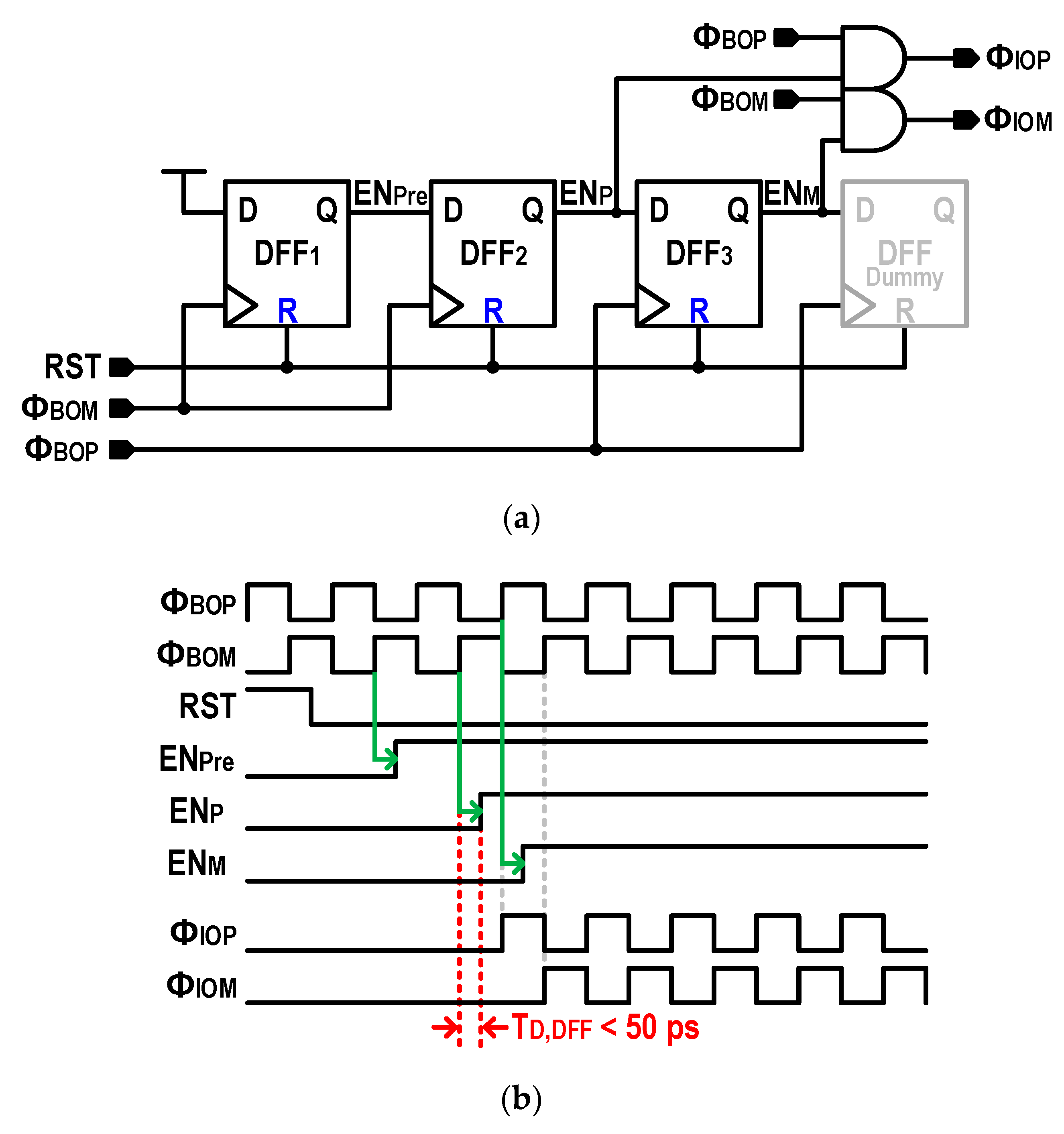

Electronics Free FullText A 6Bit 20 GS/s TimeInterleaved Two

Clock Generator Without Using Always Block End it will only run when clk is high, since you have. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. So you can only create digital dividers with verilog. Always@(clk) begin clk = 1; 2) second assign to always. Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The problem is with this block: You can't create generator without external reference clock signal. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. 1) convert first assign into initial begin clk = 0; If you want to model a clock you can: End it will only run when clk is high, since you have. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above.

From www.circuitdiagram.co

Clock Generator Schematic Diagram Circuit Diagram Clock Generator Without Using Always Block Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. The problem is with this block: End it will only run when clk is high, since you have. 1) convert first assign into initial begin clk = 0; You can't create generator without external reference clock signal. I have used following code to generate. Clock Generator Without Using Always Block.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Clock Generator Without Using Always Block If you want to model a clock you can: 1) convert first assign into initial begin clk = 0; 2) second assign to always. Always@(clk) begin clk = 1; You can't create generator without external reference clock signal. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code.. Clock Generator Without Using Always Block.

From www.renesas.cn

Renesas’ New Programmable Clock Generator Delivers Industry’s Best Clock Generator Without Using Always Block Always@(clk) begin clk = 1; 2) second assign to always. End it will only run when clk is high, since you have. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. The problem is with this block: So you can only create digital dividers with verilog. When you use a blocking. Clock Generator Without Using Always Block.

From www.eeweb.com

14 Ultra Low Jitter CrystalIn Clock Generator EE Clock Generator Without Using Always Block Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. So you can only create digital dividers with verilog. End it will only run when clk is high, since you have. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. The. Clock Generator Without Using Always Block.

From bestengineeringprojects.com

Clock Signal Generator Circuit Clock Generator Without Using Always Block I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Always@(clk) begin clk = 1; If you want to model a clock you can: So you can only create digital. Clock Generator Without Using Always Block.

From www.researchgate.net

4phase interleaving clock generator (a) schematic; (b) clock phases Clock Generator Without Using Always Block If you want to model a clock you can: So you can only create digital dividers with verilog. 2) second assign to always. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In verilog, a clock generator is a module or block of code that produces clock. Clock Generator Without Using Always Block.

From www.lightwaveonline.com

Maxim launches new clock generator series Lightwave Clock Generator Without Using Always Block If you want to model a clock you can: I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Always blocks are repeated, whereas initial blocks are. Clock Generator Without Using Always Block.

From shop.pimoroni.com

SparkFun Clock Generator Breakout 5P49V60 (Qwiic) Clock Generator Without Using Always Block End it will only run when clk is high, since you have. Always@(clk) begin clk = 1; I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. If you want to model a clock you can: 2) second assign to always. 1) convert first assign into initial begin. Clock Generator Without Using Always Block.

From blog.tindie.com

Tindie Blog Beginner Friendly Clock Generator Kit Offers an Clock Generator Without Using Always Block When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. End it will only run when clk is high, since you have. Always@(clk) begin clk = 1; The following verilog clock generator. Clock Generator Without Using Always Block.

From www.eeweb.com

Clock Generator with 14 Outputs EE Clock Generator Without Using Always Block I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The following verilog clock generator module has three parameters to tweak the three different properties as discussed. Clock Generator Without Using Always Block.

From ap170210.blogspot.com

Arduino Project AD9850 Clock Generator with Arduino Clock Generator Without Using Always Block In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The problem is with this block: Always@(clk) begin clk = 1; End it will only run when clk is high, since you have. When you use a blocking assignment, the change to clk has already happened before the @(clk). Clock Generator Without Using Always Block.

From gamma.app

Pin Diagram of 8284 Clock Generator Clock Generator Without Using Always Block In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. If you want to model a clock you can: 2) second assign to always. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Always@(clk) begin clk. Clock Generator Without Using Always Block.

From shop.pimoroni.com

SparkFun Clock Generator Breakout 5P49V60 (Qwiic) Clock Generator Without Using Always Block When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. Always@(clk) begin clk = 1; 2) second assign to always. You can't create generator without external reference clock signal. The problem is with this block: End it will only run when clk is high, since you have. So you can only create digital. Clock Generator Without Using Always Block.

From www.circuitdiagram.co

Clock Generator Schematic Diagram Circuit Diagram Clock Generator Without Using Always Block Always@(clk) begin clk = 1; If you want to model a clock you can: The problem is with this block: So you can only create digital dividers with verilog. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. You can't create generator without external reference clock signal. When. Clock Generator Without Using Always Block.

From www.youtube.com

How to generate clock in Verilog HDL Verilog code of clock generator Clock Generator Without Using Always Block Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. 2) second assign to always. End it will only run when clk is high, since you have. So you can only create digital dividers with verilog. I have used following code to generate clock (whichever value i pass through task it will create that. Clock Generator Without Using Always Block.

From www.youtube.com

21 Verilog Clock Generator YouTube Clock Generator Without Using Always Block Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. Always@(clk) begin clk = 1; 2) second assign to always. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. You can't create generator without external reference clock signal. The following verilog clock. Clock Generator Without Using Always Block.

From www.researchgate.net

Block diagram of a conventional secondorder PLLbased clock generator Clock Generator Without Using Always Block In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. End it will only run when clk is high, since you have. Always@(clk) begin clk = 1; 2) second assign to always.. Clock Generator Without Using Always Block.

From bestengineeringprojects.com

Clock Signal Generator Circuit Best Engineering Projects Clock Generator Without Using Always Block 2) second assign to always. You can't create generator without external reference clock signal. 1) convert first assign into initial begin clk = 0; Always@(clk) begin clk = 1; If you want to model a clock you can: Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. End it will only run when. Clock Generator Without Using Always Block.

From itecnotes.com

Electronic Clock generation of 9 phases of clock Valuable Tech Notes Clock Generator Without Using Always Block End it will only run when clk is high, since you have. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. 1) convert first assign into initial begin clk = 0; Always@(clk) begin clk. Clock Generator Without Using Always Block.

From www.analog.com

EasytoUse Spread Spectrum Clock Generator Reduces EMI and More Clock Generator Without Using Always Block End it will only run when clk is high, since you have. The problem is with this block: You can't create generator without external reference clock signal. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I have used following code to generate clock (whichever value i pass. Clock Generator Without Using Always Block.

From www.youtube.com

555 timer pulse Generator, 555 projects Circuit Diagram YouTube Clock Generator Without Using Always Block You can't create generator without external reference clock signal. 1) convert first assign into initial begin clk = 0; In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but. Clock Generator Without Using Always Block.

From learn.sparkfun.com

SparkFun Clock Generator 5P49V60 (Qwiic) Hookup Guide SparkFun Learn Clock Generator Without Using Always Block Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. So you can only create digital dividers with verilog. The problem is with this block: 2) second assign to always. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. 1) convert first. Clock Generator Without Using Always Block.

From www.renesas.cn

5P49V5913 VersaClock® 5 Low Power Programmable Clock Generator Renesas Clock Generator Without Using Always Block End it will only run when clk is high, since you have. The problem is with this block: 2) second assign to always. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. 1) convert first assign into initial begin clk = 0; I have used following code to generate clock (whichever value. Clock Generator Without Using Always Block.

From circuitscheme.com

1 Hz Clock Generator Circuit Document Circuit Scheme Clock Generator Without Using Always Block 2) second assign to always. So you can only create digital dividers with verilog. 1) convert first assign into initial begin clk = 0; Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and. Clock Generator Without Using Always Block.

From www.researchgate.net

Block diagram of a conventional secondorder PLLbased clock generator Clock Generator Without Using Always Block You can't create generator without external reference clock signal. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. 2) second assign to always. The problem is with this block: When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. Always blocks are repeated, whereas. Clock Generator Without Using Always Block.

From www.slowroom.be

ARDUINO CLOCK GENERATOR SLOWROOM Clock Generator Without Using Always Block Always@(clk) begin clk = 1; If you want to model a clock you can: 1) convert first assign into initial begin clk = 0; 2) second assign to always. You can't create generator without external reference clock signal. So you can only create digital dividers with verilog. In verilog, a clock generator is a module or block of code that. Clock Generator Without Using Always Block.

From www.renesas.com

Clock Generation Renesas Clock Generator Without Using Always Block In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. Always@(clk) begin clk = 1; Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. If. Clock Generator Without Using Always Block.

From www.mdpi.com

Electronics Free FullText A 6Bit 20 GS/s TimeInterleaved Two Clock Generator Without Using Always Block Always@(clk) begin clk = 1; End it will only run when clk is high, since you have. You can't create generator without external reference clock signal. 1) convert first assign into initial begin clk = 0; In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. When you use. Clock Generator Without Using Always Block.

From www.eetasia.com

Skyworks Launches Ultralow Jitter Clock Generator EE Times Asia Clock Generator Without Using Always Block Always@(clk) begin clk = 1; 2) second assign to always. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The following verilog clock generator module has. Clock Generator Without Using Always Block.

From www.researchgate.net

Block diagrams of the clock generator (a) and the TFF as a resettable T Clock Generator Without Using Always Block The problem is with this block: Always@(clk) begin clk = 1; So you can only create digital dividers with verilog. End it will only run when clk is high, since you have. The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. I have used following code to generate clock (whichever value. Clock Generator Without Using Always Block.

From www.newelectronics.co.uk

Online first for customisable clock generator Clock Generator Without Using Always Block End it will only run when clk is high, since you have. I have used following code to generate clock (whichever value i pass through task it will create that frequency), but the code. Always@(clk) begin clk = 1; When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. 1) convert first assign. Clock Generator Without Using Always Block.

From www.researchgate.net

Clock generator architecture. Download Scientific Diagram Clock Generator Without Using Always Block So you can only create digital dividers with verilog. End it will only run when clk is high, since you have. If you want to model a clock you can: When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. The problem is with this block: The following verilog clock generator module has. Clock Generator Without Using Always Block.

From www.slideserve.com

PPT Verilog PowerPoint Presentation, free download ID5709023 Clock Generator Without Using Always Block 1) convert first assign into initial begin clk = 0; The problem is with this block: The following verilog clock generator module has three parameters to tweak the three different properties as discussed above. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. If you want to model a clock you can:. Clock Generator Without Using Always Block.

From ramapcsx2.github.io

Si5351 Clock Generator install notes · GBS Control Clock Generator Without Using Always Block When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Always@(clk) begin clk = 1; Always blocks are repeated, whereas initial blocks are run once at the start of the simulation. 1). Clock Generator Without Using Always Block.

From www.mdpi.com

Electronics Free FullText A 6Bit 20 GS/s TimeInterleaved Two Clock Generator Without Using Always Block So you can only create digital dividers with verilog. When you use a blocking assignment, the change to clk has already happened before the @(clk) executes. 2) second assign to always. If you want to model a clock you can: The problem is with this block: Always@(clk) begin clk = 1; End it will only run when clk is high,. Clock Generator Without Using Always Block.