Continuous Time Linear Equalizer Circuit . — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least.

from www.semanticscholar.org

continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle).

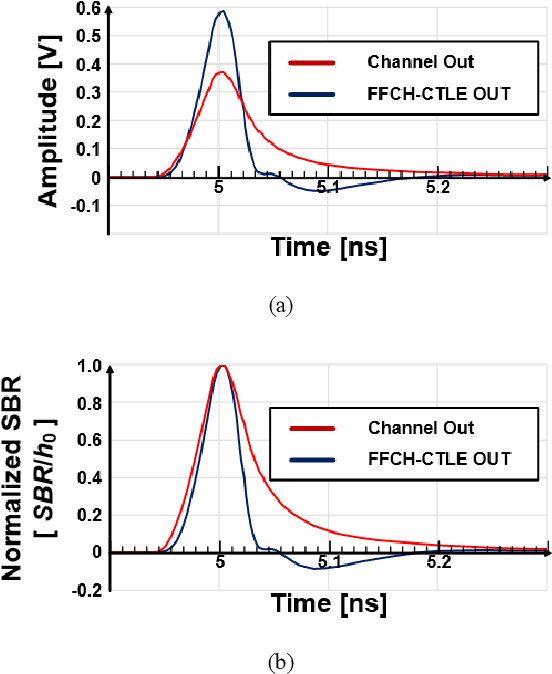

Figure 5 from Feedforward CherryHooper Continuous Time Linear

Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be.

From www.bilibili.com

[芯片设计]CTLE (Continuous Time Linear Equalizer) HIGH SPEED SERDES_哔哩哔哩 Continuous Time Linear Equalizer Circuit continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 2 from A ContinuousTime Linear Equalizer With Ultrafine Gain Continuous Time Linear Equalizer Circuit In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

1V continuoustime linear equalizer for up to 2 Gb/s over 50m SIPOF Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 5 from Feedforward CherryHooper Continuous Time Linear Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Table II from An Active CopperCable Supporting 56Gbit/s PAM4 and 28 Continuous Time Linear Equalizer Circuit continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 1 from A 56Gb/s PAM4 ContinuousTime Linear Equalizer with Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 5 from Feedforward CherryHooper Continuous Time Linear Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.mdpi.com

Electronics Free FullText Receiver Analog FrontEnd Cascading Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 9 from Flexible Transversal ContinuousTime Linear Equalizer Continuous Time Linear Equalizer Circuit In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). Continuous Time Linear Equalizer Circuit.

From www.scribd.com

Design of A Continuous Time Equalizer Circuit (CTLE) PDF Continuous Time Linear Equalizer Circuit continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Design of Receiver Continuous Time Linear Equalizer for High Gain Continuous Time Linear Equalizer Circuit In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). Continuous Time Linear Equalizer Circuit.

From www.mdpi.com

Electronics Free FullText Receiver Analog FrontEnd Cascading Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 1 from An ActiveCopperCable with ContinuousTimeLinear Continuous Time Linear Equalizer Circuit In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.google.com

Patent US8810319 Dualstage continuoustime linear equalizer Google Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.mdpi.com

Electronics Free FullText Receiver Analog FrontEnd Cascading Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From blog.teledynelecroy.com

Test Happens Teledyne LeCroy Blog Continuous Time Linear Equalization Continuous Time Linear Equalizer Circuit continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. Continuous Time Linear Equalizer Circuit.

From www.slideserve.com

PPT HighSpeed and LowPower OnChip Global Link Using Continuous Continuous Time Linear Equalizer Circuit continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.mdpi.com

Electronics Free FullText Receiver Analog FrontEnd Cascading Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.google.com

Patent US8810319 Dualstage continuoustime linear equalizer Google Continuous Time Linear Equalizer Circuit continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). Continuous Time Linear Equalizer Circuit.

From www.slideserve.com

PPT HighSpeed and LowPower OnChip Global Link Using Continuous Continuous Time Linear Equalizer Circuit continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 1 from Energyefficient continuoustime linear equalizer for Continuous Time Linear Equalizer Circuit continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. Continuous Time Linear Equalizer Circuit.

From eureka.patsnap.com

Continuous time linear equalization circuit with programmable gains Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 7 from Design of Receiver Continuous Time Linear Equalizer for Continuous Time Linear Equalizer Circuit continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 1 from A 520 Gb/s power scalable adaptive linear equalizer Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.vpiphotonics.com

VPIphotonics Subsystem Continuous Time Linear Equalizer Circuit continuous time linear equalizer. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 10 from Comparison of receiver equalization using firstorder Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 1 from A continuoustime equalizer adopting a clock attenuation Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.intel.com

5.1.2.1.3. Continuous Time Linear Equalization (CTLE) Continuous Time Linear Equalizer Circuit continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 1 from A 10Gb/s lowpower adaptive continuoustime linear Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From eureka.patsnap.com

Continuous time linear equalization circuit with programmable gains Continuous Time Linear Equalizer Circuit In order to recover data, it is necessary to have bandwidth at least. a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. — one of those ways is to implement continuous time linear equalization (ctle). continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 5 from Feedforward CherryHooper Continuous Time Linear Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.slideserve.com

PPT HighSpeed and LowPower OnChip Global Link Using Continuous Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. In order to recover data, it is necessary to have bandwidth at least. — one of those ways is to implement continuous time linear equalization (ctle). Continuous Time Linear Equalizer Circuit.

From eureka.patsnap.com

Methods and apparatus for continuous time linear equalizer tuning using Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.

From www.semanticscholar.org

Figure 6 from Design of Receiver Continuous Time Linear Equalizer for Continuous Time Linear Equalizer Circuit a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. continuous time linear equalizer. — one of those ways is to implement continuous time linear equalization (ctle). In order to recover data, it is necessary to have bandwidth at least. Continuous Time Linear Equalizer Circuit.

From www.researchgate.net

Summer circuit of the DFE Download Scientific Diagram Continuous Time Linear Equalizer Circuit — one of those ways is to implement continuous time linear equalization (ctle). a continuous time linear equaliser (ctle) with a transversal architecture features variable dc gain and two zeros that can be. In order to recover data, it is necessary to have bandwidth at least. continuous time linear equalizer. Continuous Time Linear Equalizer Circuit.