Kickback In Comparator . See examples of offset cancellation, kickback. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. It is basically the noise from the switching first stage on the input of your comparator. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Offset voltage, random noise and kickback noise. If the output of the first stage.

from www.semanticscholar.org

Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. It is basically the noise from the switching first stage on the input of your comparator. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. If the output of the first stage. See examples of offset cancellation, kickback. Offset voltage, random noise and kickback noise. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch.

Figure 1 from A Fully Synthesizable Dynamic Latched Comparator with

Kickback In Comparator This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. If the output of the first stage. See examples of offset cancellation, kickback. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Offset voltage, random noise and kickback noise. It is basically the noise from the switching first stage on the input of your comparator. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages.

From www.semanticscholar.org

A lowkickbacknoise and lowvoltage latched comparator for highspeed Kickback In Comparator Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Offset voltage, random noise and kickback noise. See examples of offset cancellation, kickback. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the. Kickback In Comparator.

From www.slideshare.net

KICKBACK NOISE ANALYSIS OF LOW POWER COMPARATOR Kickback In Comparator Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. See examples of offset cancellation, kickback. If the output of the first stage. This article reviews and proposes solutions to minimize the. Kickback In Comparator.

From eureka.patsnap.com

Reduction in kickback effect in comparators Eureka Patsnap develop Kickback In Comparator Offset voltage, random noise and kickback noise. See examples of offset cancellation, kickback. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. If the output of the first. Kickback In Comparator.

From www.researchgate.net

Proposed low‐offset low‐kickback dynamic comparator Download Kickback In Comparator See examples of offset cancellation, kickback. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Offset voltage, random noise and kickback noise. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the. Kickback In Comparator.

From www.semanticscholar.org

Figure 1 from A Novel Dynamic Comparator with Reduced Kickback Noise Kickback In Comparator Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. Offset voltage, random noise and kickback noise. See examples of offset cancellation, kickback. This article reviews and proposes solutions to minimize the kickback noise in. Kickback In Comparator.

From www.researchgate.net

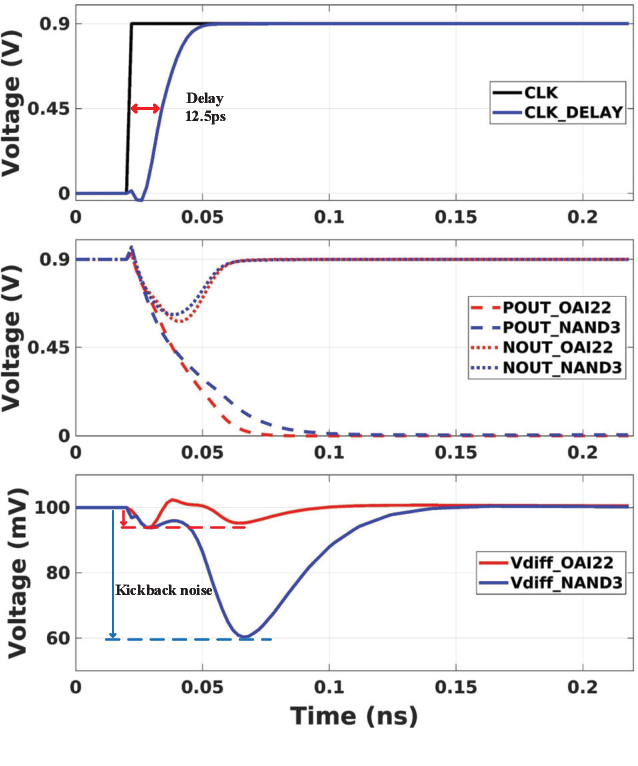

Simulation results of the kickback noise in the latched comparator Kickback In Comparator Offset voltage, random noise and kickback noise. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched. Kickback In Comparator.

From www.researchgate.net

Proposed low‐offset low‐kickback dynamic comparator Download Kickback In Comparator Offset voltage, random noise and kickback noise. See examples of offset cancellation, kickback. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Learn the basic concepts, parameters and design issues of cmos. Kickback In Comparator.

From www.semanticscholar.org

Figure 17 from A 0.3V 10b 3MS/s SAR ADC With Comparator Calibration and Kickback In Comparator Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. It is basically the noise from the switching first stage on the input of your comparator. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. If the output of the first stage. Learn the basic concepts,. Kickback In Comparator.

From www.researchgate.net

Kickback effect of the four dynamic comparators for k=1. A, This work Kickback In Comparator Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. Offset voltage, random noise and kickback noise.. Kickback In Comparator.

From www.slideshare.net

KICKBACK NOISE ANALYSIS OF LOW POWER COMPARATOR Kickback In Comparator If the output of the first stage. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Offset voltage, random noise and kickback noise. This article reviews and proposes solutions to minimize the. Kickback In Comparator.

From www.semanticscholar.org

Figure 1 from A Design of Kickback Noise Suppression Comparator for Kickback In Comparator It is basically the noise from the switching first stage on the input of your comparator. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. If the output of the first stage. This article. Kickback In Comparator.

From www.semanticscholar.org

A lowpower, highresolution, 1 GHz differential comparator with low Kickback In Comparator If the output of the first stage. Offset voltage, random noise and kickback noise. See examples of offset cancellation, kickback. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. Learn. Kickback In Comparator.

From www.semanticscholar.org

A lowkickbacknoise and lowvoltage latched comparator for highspeed Kickback In Comparator It is basically the noise from the switching first stage on the input of your comparator. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. See examples of offset cancellation, kickback.. Kickback In Comparator.

From www.youtube.com

A Three Stage Comparator and Its Modified Version With Fast Speed and Kickback In Comparator Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. Offset voltage, random noise and kickback noise. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. If the output of the first stage. This paper reviews existing solutions to minimize the kickback noise, a. Kickback In Comparator.

From www.semanticscholar.org

A low kick back noise latched comparator for high speed folding and Kickback In Comparator Offset voltage, random noise and kickback noise. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. It is basically the noise from the switching first stage on the input of your comparator. If the output of the first stage. Learn how to design a cmos comparator with. Kickback In Comparator.

From www.semanticscholar.org

Figure 1 from A 0.3V 10b 3MS/s SAR ADC With Comparator Calibration and Kickback In Comparator Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. See examples of offset cancellation, kickback. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. It is. Kickback In Comparator.

From www.semanticscholar.org

Figure 1 from A Fully Synthesizable Dynamic Latched Comparator with Kickback In Comparator Offset voltage, random noise and kickback noise. It is basically the noise from the switching first stage on the input of your comparator. If the output of the first stage. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Learn the basic concepts, parameters and design issues of cmos comparators, such. Kickback In Comparator.

From www.researchgate.net

(PDF) Systematic analysis and cancellation of kickback noise in a Kickback In Comparator Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. See examples of offset cancellation, kickback. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. If the output of the first stage. It is basically the noise from the switching. Kickback In Comparator.

From www.researchgate.net

3 The low kickback noise comparator. Download Scientific Diagram Kickback In Comparator This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. If the output of the first stage. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the. Kickback In Comparator.

From www.semanticscholar.org

Figure 4 from A Novel Dynamic Comparator with Reduced Kickback Noise Kickback In Comparator Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. If the output of the first stage. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched. Kickback In Comparator.

From www.researchgate.net

A comparator with low kickback noise. Download Scientific Diagram Kickback In Comparator If the output of the first stage. See examples of offset cancellation, kickback. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. It is basically the noise from the switching first stage on the input of. Kickback In Comparator.

From www.semanticscholar.org

A 1GS/s lowpower lowkickback noise comparator in CMOS process Kickback In Comparator Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Offset voltage, random noise and kickback. Kickback In Comparator.

From www.semanticscholar.org

Figure 2 from Impact of Kickback Noise of Comparator in Single Slope Kickback In Comparator Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. See examples of offset cancellation, kickback. Offset voltage, random noise and kickback noise. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset,. Kickback In Comparator.

From www.semanticscholar.org

Figure 3 from A 1GS/s lowpower lowkickback noise comparator in CMOS Kickback In Comparator This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. It is basically the noise from the switching first stage on the input of your comparator. This paper reviews existing solutions to minimize. Kickback In Comparator.

From www.researchgate.net

Kickback effect of the four dynamic comparators for k=1. A, This work Kickback In Comparator Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Offset voltage, random noise and kickback noise. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. If the output of the first stage. Learn the basic concepts, parameters and design issues of cmos comparators, such as. Kickback In Comparator.

From www.semanticscholar.org

Figure 6 from A Design of Kickback Noise Suppression Comparator for Kickback In Comparator It is basically the noise from the switching first stage on the input of your comparator. See examples of offset cancellation, kickback. If the output of the first stage. Offset voltage, random noise and kickback noise. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Learn the basic concepts, parameters and design issues of. Kickback In Comparator.

From www.semanticscholar.org

Figure 1 from A 0.3V 10b 3MS/s SAR ADC With Comparator Calibration and Kickback In Comparator Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. It is basically the noise from the switching first stage on the input of your comparator. See examples of offset cancellation, kickback. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator. Kickback In Comparator.

From www.semanticscholar.org

Figure 1 from A Design of Kickback Noise Suppression Comparator for Kickback In Comparator Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Learn. Kickback In Comparator.

From www.researchgate.net

Set‐up used to simulate the kickback noise Download Scientific Diagram Kickback In Comparator It is basically the noise from the switching first stage on the input of your comparator. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Offset voltage, random. Kickback In Comparator.

From www.researchgate.net

Proposed low‐offset low‐kickback dynamic comparator Download Kickback In Comparator See examples of offset cancellation, kickback. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. If the output of the first stage. It is basically the noise from the switching first stage. Kickback In Comparator.

From www.semanticscholar.org

Figure 7 from A 0.3V 10b 3MS/s SAR ADC With Comparator Calibration and Kickback In Comparator See examples of offset cancellation, kickback. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Addressing the pervasive issue of kickback noise in dynamic comparators has the potential to reshape the adc technology. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input. Kickback In Comparator.

From www.semanticscholar.org

Figure 7 from A Fully Synthesizable Dynamic Latched Comparator with Kickback In Comparator This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. If the output. Kickback In Comparator.

From www.researchgate.net

(a) Schematic of the comparator in SAR ADC. (b) Simulation results of Kickback In Comparator Offset voltage, random noise and kickback noise. This paper reviews existing solutions to minimize the kickback noise, a disturbance in the input voltage of a latched comparator caused by. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. It is basically the noise from the switching first stage on. Kickback In Comparator.

From www.semanticscholar.org

Figure 7 from A Fully Synthesizable Dynamic Latched Comparator with Kickback In Comparator See examples of offset cancellation, kickback. If the output of the first stage. It is basically the noise from the switching first stage on the input of your comparator. This article reviews and proposes solutions to minimize the kickback noise in latched comparators, which are widely used in. Offset voltage, random noise and kickback noise. Learn the basic concepts, parameters. Kickback In Comparator.

From www.researchgate.net

Highspeed current comparator with reduced kickback noise Download Kickback In Comparator Offset voltage, random noise and kickback noise. Learn how to design a cmos comparator with preamp, reference subtraction, latch, and regeneration stages. If the output of the first stage. Learn the basic concepts, parameters and design issues of cmos comparators, such as offset, speed, power, input range and mismatch. This article reviews and proposes solutions to minimize the kickback noise. Kickback In Comparator.