Why We Use Clock Gating . Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Can you figure out why? Clock gating reduces power dissipation for the following reasons: In this article, we will go. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating method stops the clock for those elements in the design whose data is not toggling.

from webdocs.cs.ualberta.ca

In this article, we will go. Clock gating reduces power dissipation for the following reasons: This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Can you figure out why? Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus.

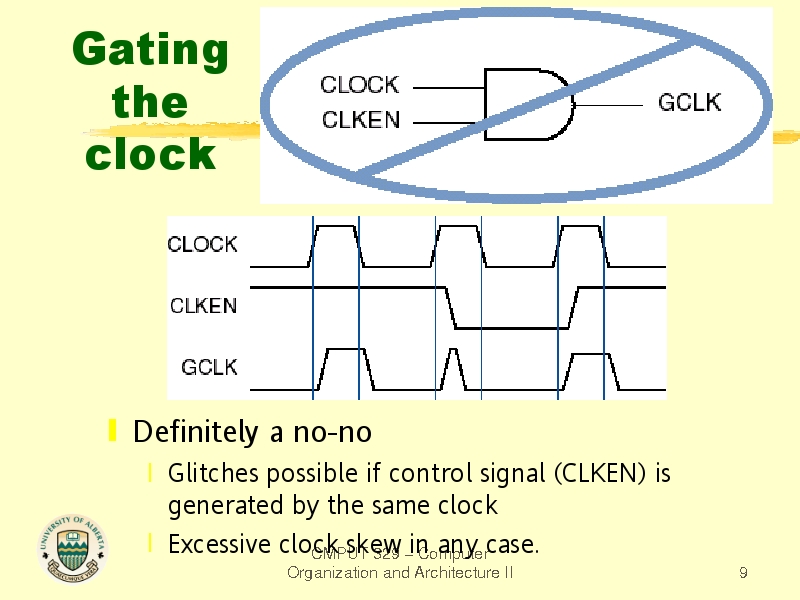

Gating the clock

Why We Use Clock Gating Can you figure out why? Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Clock gating reduces power dissipation for the following reasons: This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating method stops the clock for those elements in the design whose data is not toggling. Can you figure out why?

From www.slideserve.com

PPT Overview PowerPoint Presentation, free download ID6347919 Why We Use Clock Gating Clock gating reduces power dissipation for the following reasons: The clock gating method stops the clock for those elements in the design whose data is not toggling. Can you figure out why? This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. In this article, we will go. Clock gating is one of the. Why We Use Clock Gating.

From www.researchgate.net

Fine grained clock gating. Download Scientific Diagram Why We Use Clock Gating This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Can you figure out why? Clock gating reduces power dissipation for the following reasons: In this article, we will go. Integrated clock gating (icg) cell is a. Why We Use Clock Gating.

From www.researchgate.net

Flowchart of clock gating. The proposed clock gating circuit is shown Why We Use Clock Gating This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Clock gating reduces power dissipation for the following reasons: Can you figure out why? Because a high on ‘en’ signal allows the clock cycle to hit register. Why We Use Clock Gating.

From mungfali.com

Clock Gating VLSI Why We Use Clock Gating This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. In this article, we will go. Clock gating reduces power dissipation for the following reasons: Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Because a high on ‘en’ signal allows the clock cycle to hit. Why We Use Clock Gating.

From www.researchgate.net

Power gating scheme with clock gating controlAMPG Adapted from Jun Why We Use Clock Gating Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Can you figure out why? The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating reduces power dissipation. Why We Use Clock Gating.

From vlsihq.com

Clock Gating technique for Power Saving vlsiHQ Why We Use Clock Gating Can you figure out why? This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Clock gating reduces power dissipation. Why We Use Clock Gating.

From soc-asic-design.blogspot.com

All you need to know about SoC Design, Methodologies and Techniques Why We Use Clock Gating Can you figure out why? This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. In this article, we. Why We Use Clock Gating.

From www.researchgate.net

Conventional ClockGating Scheme. Download Scientific Diagram Why We Use Clock Gating This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Can you figure out why? The clock gating method stops the clock for those elements in the design whose data is not toggling. Because a high on. Why We Use Clock Gating.

From semiengineering.com

Clock Gating Semiconductor Engineering Why We Use Clock Gating Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. The clock gating method stops the clock for those elements in the design whose data is not toggling. In this article, we will go. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Because a. Why We Use Clock Gating.

From www.slideserve.com

PPT Power Management PowerPoint Presentation, free download ID4638257 Why We Use Clock Gating Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Clock gating reduces power dissipation for the following reasons: Can you figure out why? Clock gating is one of the most popular techniques used in many synchronous. Why We Use Clock Gating.

From www.slideserve.com

PPT 32bit parallel load register with clock gating PowerPoint Why We Use Clock Gating The clock gating method stops the clock for those elements in the design whose data is not toggling. Can you figure out why? Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Clock gating reduces power dissipation for the following reasons: Because a high on ‘en’ signal allows the clock cycle to. Why We Use Clock Gating.

From www.slideshare.net

Clock gating Why We Use Clock Gating The clock gating method stops the clock for those elements in the design whose data is not toggling. Can you figure out why? In this article, we will go. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. This technique of using an ‘and’ gate is referred to as ‘active high’ clock. Why We Use Clock Gating.

From www.researchgate.net

A simplified gated clock network consisting of five sinks, an Why We Use Clock Gating Clock gating reduces power dissipation for the following reasons: Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. This technique of using an ‘and’ gate is referred to as ‘active high’. Why We Use Clock Gating.

From www.electronicsforu.com

Clock Gating for the of Things Design Guide Why We Use Clock Gating In this article, we will go. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. The clock gating method stops the clock for those elements in the design whose data is not toggling. Can you figure. Why We Use Clock Gating.

From vlsi-soc.blogspot.com

VLSI SoC Design Integrated Clock and Power Gating Why We Use Clock Gating In this article, we will go. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Clock gating reduces power dissipation for the following reasons: Can you figure out why? Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. The clock gating method stops the clock for. Why We Use Clock Gating.

From medium.com

Let’s talk about Clock Gating!. Clock gating is a technique that… by Why We Use Clock Gating Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Can you figure out why? Clock gating reduces power dissipation for the following reasons: Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. This technique of using an ‘and’ gate is referred to as ‘active high’ clock. Why We Use Clock Gating.

From www.youtube.com

Clock Gating Basics Basics of Clock Gating Clock Gating Techniques Why We Use Clock Gating In this article, we will go. Clock gating reduces power dissipation for the following reasons: The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. This technique of using an ‘and’ gate is referred to. Why We Use Clock Gating.

From www.slideserve.com

PPT Lecture 7 Power PowerPoint Presentation, free download ID4495903 Why We Use Clock Gating The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating reduces power dissipation for the following reasons: Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Can you figure out why? This technique of using an ‘and’ gate is referred to as. Why We Use Clock Gating.

From www.researchgate.net

Timing sequencing and overhead of adaptive clock gating. Download Why We Use Clock Gating Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. The clock gating method stops the clock for those elements in the design whose data is not toggling. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Can you figure out why? Clock gating is one of. Why We Use Clock Gating.

From vlsimaster.com

Clock Gating VLSI Master Why We Use Clock Gating Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Can you figure out why? The clock gating method stops the clock for those elements in the design whose data is not toggling. In this article, we will go. This technique of using an ‘and’ gate is referred to as ‘active high’ clock. Why We Use Clock Gating.

From www.researchgate.net

Timing sequencing and overhead of adaptive clock gating. Download Why We Use Clock Gating Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. The clock gating method stops the clock for those elements in the. Why We Use Clock Gating.

From www.youtube.com

Clock gating technique in VLSI Integrated Clock Gating (ICG) Latch Why We Use Clock Gating Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating reduces power dissipation for the following reasons: Can. Why We Use Clock Gating.

From tech.tdzire.com

Clock Gating checks and Clock Gating Cell TechnologyTdzire Why We Use Clock Gating This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go. Clock gating reduces power dissipation for the following reasons: Because a high on ‘en’ signal allows the clock cycle to hit. Why We Use Clock Gating.

From www.slideserve.com

PPT Power Optimization for Clock Network with Clock Gate Cloning and Why We Use Clock Gating Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Clock gating reduces power dissipation for the following reasons: Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. The clock gating method stops the clock for those elements in the design whose data is not toggling. In. Why We Use Clock Gating.

From webdocs.cs.ualberta.ca

Gating the clock Why We Use Clock Gating Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock gating (icg) cell is a specially designed cell that is. Why We Use Clock Gating.

From vlsimaster.com

Clock Gating VLSI Master Why We Use Clock Gating This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Can you figure out why? Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating reduces power. Why We Use Clock Gating.

From www.researchgate.net

3 Clock gating of the main clock to some component Download Why We Use Clock Gating Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating reduces power dissipation for the following reasons: Can you figure out why? Because a high on ‘en’ signal allows the clock cycle to. Why We Use Clock Gating.

From www.researchgate.net

Clock gating scheme Adapted from Hsu & Lin, 2011. Download Scientific Why We Use Clock Gating Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Can you figure out why? Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic.. Why We Use Clock Gating.

From www.researchgate.net

5 Finegrained clock gating. Download Scientific Diagram Why We Use Clock Gating In this article, we will go. Can you figure out why? Clock gating reduces power dissipation for the following reasons: This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Clock gating is one of the most. Why We Use Clock Gating.

From www.slideserve.com

PPT The clock PowerPoint Presentation, free download ID2403529 Why We Use Clock Gating The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. In this article, we will go. Can you figure out why? Integrated clock gating (icg) cell is a specially designed cell that is used for. Why We Use Clock Gating.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation Why We Use Clock Gating Clock gating reduces power dissipation for the following reasons: Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. In this article, we will go. Clock gating is one of the most popular techniques used in many. Why We Use Clock Gating.

From www.youtube.com

Clock Gating Based Energy Efficient ALU Design and Implementation on Why We Use Clock Gating In this article, we will go. Clock gating reduces power dissipation for the following reasons: Can you figure out why? Because a high on ‘en’ signal allows the clock cycle to hit register bank, thus. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. This technique of using an ‘and’ gate is. Why We Use Clock Gating.

From www.slideshare.net

Clock gating Why We Use Clock Gating Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. In this article, we will go. Clock gating reduces power dissipation for the following reasons: The clock gating method stops the clock for those elements in the design whose data is not toggling. Because a high on ‘en’ signal allows the clock cycle. Why We Use Clock Gating.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI Why We Use Clock Gating Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. This technique of using an ‘and’ gate is referred to as ‘active high’ clock gating technique. Integrated clock gating (icg) cell is a specially designed cell that is used for clock gating techniques. Because a high on ‘en’ signal allows the clock cycle. Why We Use Clock Gating.

From logicsense.wordpress.com

Clock gating Techworld Why We Use Clock Gating The clock gating method stops the clock for those elements in the design whose data is not toggling. Clock gating is one of the most popular techniques used in many synchronous circuits for reducing dynamic. Clock gating reduces power dissipation for the following reasons: Can you figure out why? In this article, we will go. Integrated clock gating (icg) cell. Why We Use Clock Gating.