Vhdl Testbench Clock Example . First, edit the constant for the clock period definition. This allows you to easily change the pattern of the waveform that you want to feed… All concurrent assignments can be. Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Process begin clk <= '0'; This example shows how to generate a clock, and give inputs and assert outputs for. We would like this to match the 50 mhz clock that is coming into the test bench to. How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In many test benches i see the following pattern for clock generation:

from surf-vhdl.com

First, edit the constant for the clock period definition. All concurrent assignments can be. This example shows how to generate a clock, and give inputs and assert outputs for. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). This allows you to easily change the pattern of the waveform that you want to feed… In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In many test benches i see the following pattern for clock generation: Process begin clk <= '0'; How to use a clock and do assertions.

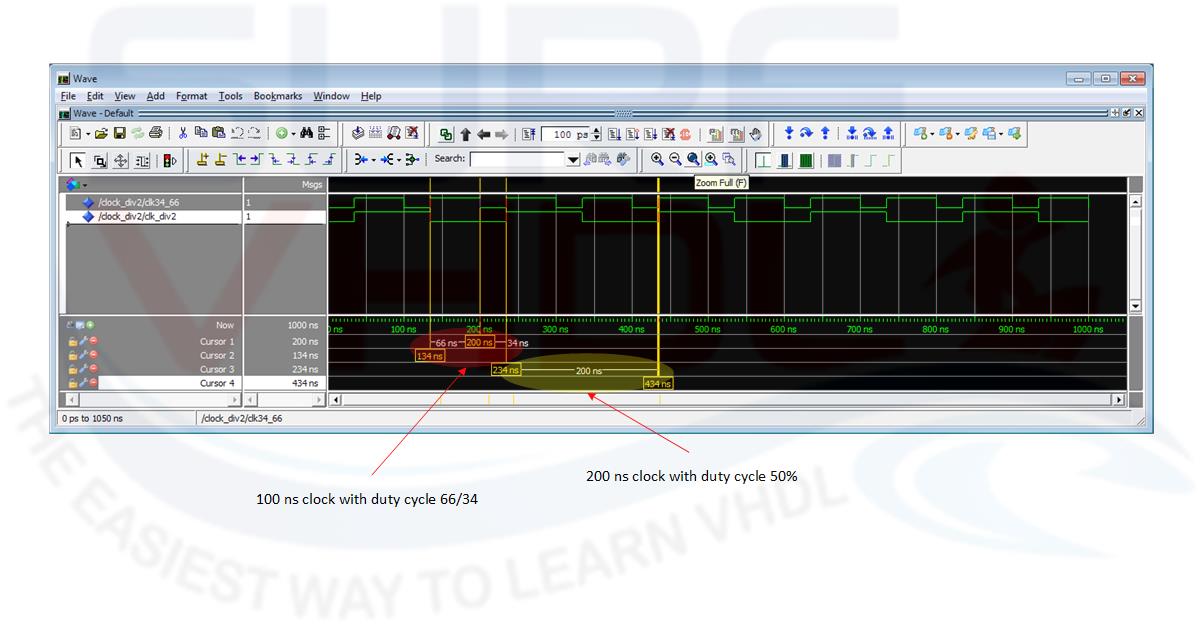

How To Implement Clock Divider in VHDL SurfVHDL

Vhdl Testbench Clock Example This example shows how to generate a clock, and give inputs and assert outputs for. This allows you to easily change the pattern of the waveform that you want to feed… In many test benches i see the following pattern for clock generation: In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. First, edit the constant for the clock period definition. This example shows how to generate a clock, and give inputs and assert outputs for. All concurrent assignments can be. We would like this to match the 50 mhz clock that is coming into the test bench to. How to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Process begin clk <= '0'; Reading signal values from file is an alternative way of generating stimuli for the device on test (dut).

From www.chegg.com

Describe the clock divider circuit in VHDL using the Vhdl Testbench Clock Example How to use a clock and do assertions. This example shows how to generate a clock, and give inputs and assert outputs for. All concurrent assignments can be. First, edit the constant for the clock period definition. We would like this to match the 50 mhz clock that is coming into the test bench to. Process begin clk <= '0';. Vhdl Testbench Clock Example.

From www.youtube.com

VHDL Lecture 23 Lab 8 Clock Dividers and Counters YouTube Vhdl Testbench Clock Example This allows you to easily change the pattern of the waveform that you want to feed… Process begin clk <= '0'; In many test benches i see the following pattern for clock generation: In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. First, edit the constant for the clock period. Vhdl Testbench Clock Example.

From vipwood.blogspot.com

Portable Topic Simple test bench vhdl Vhdl Testbench Clock Example We would like this to match the 50 mhz clock that is coming into the test bench to. In many test benches i see the following pattern for clock generation: In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. All concurrent assignments can be. Process begin clk <= '0'; First,. Vhdl Testbench Clock Example.

From www.youtube.com

Create a simple VHDL test bench using Xilinx ISE. YouTube Vhdl Testbench Clock Example In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This example shows how to generate a clock, and give inputs and assert outputs for. This allows you to easily change the pattern of the waveform that you want to feed… In many test benches i see the following. Vhdl Testbench Clock Example.

From www.youtube.com

Electronics VHDL testbench variable clock/wave generation (2 Solutions Vhdl Testbench Clock Example How to use a clock and do assertions. First, edit the constant for the clock period definition. Process begin clk <= '0'; This example shows how to generate a clock, and give inputs and assert outputs for. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This allows. Vhdl Testbench Clock Example.

From vhdltb.blogspot.com

VHDL Test Bench for FPGA/ASIC Verification VHDL Test Bench Usage Tips Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Process begin clk <= '0'; In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. How to use a clock and do assertions. This example shows how to generate a. Vhdl Testbench Clock Example.

From amberandconnorshakespeare.blogspot.com

Vhdl Test Bench Code amberandconnorshakespeare Vhdl Testbench Clock Example Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In many test benches i see the following pattern for clock generation: All concurrent assignments can be. We would like this. Vhdl Testbench Clock Example.

From www.youtube.com

Mod04 Lec22 VHDL Examples, FSM Clock YouTube Vhdl Testbench Clock Example This example shows how to generate a clock, and give inputs and assert outputs for. All concurrent assignments can be. We would like this to match the 50 mhz clock that is coming into the test bench to. How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal. Vhdl Testbench Clock Example.

From www.youtube.com

VHDL BASIC Tutorial TESTBENCH YouTube Vhdl Testbench Clock Example How to use a clock and do assertions. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Process begin clk <= '0'; All concurrent assignments can be. This allows you to easily change the pattern of the waveform that you want to feed… We would like this to match the. Vhdl Testbench Clock Example.

From www.youtube.com

Electronics clock in testbench VHDL (2 Solutions!!) YouTube Vhdl Testbench Clock Example Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). This example shows how to generate a clock, and give inputs and assert outputs for. In many test benches i see the following pattern for clock generation: We would like this to match the 50 mhz clock that is coming into the. Vhdl Testbench Clock Example.

From vhdlguru.blogspot.com

VHDL coding tips and tricks VHDL Simple Digital Clock with Testbench Vhdl Testbench Clock Example How to use a clock and do assertions. All concurrent assignments can be. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. First, edit the constant for the clock period definition. We would like this to match the 50 mhz clock that is coming into the test bench to. This. Vhdl Testbench Clock Example.

From allmodernbenches.blogspot.com

Modern Storage Benches and Dining Benches Vhdl Test Bench Clock Vhdl Testbench Clock Example How to use a clock and do assertions. This example shows how to generate a clock, and give inputs and assert outputs for. In many test benches i see the following pattern for clock generation: In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This allows you to. Vhdl Testbench Clock Example.

From www.numerade.com

Text Part b, /15 Question 5 (15 points) Write a VHDL testbench (for Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. We would like this to match the 50 mhz clock that is coming into the test bench to. All concurrent assignments can be. Reading signal values from file is an alternative way of generating stimuli for the device on test (dut).. Vhdl Testbench Clock Example.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. First, edit the constant for the clock period definition. This example shows. Vhdl Testbench Clock Example.

From surf-vhdl.com

How To Implement Clock Divider in VHDL SurfVHDL Vhdl Testbench Clock Example This example shows how to generate a clock, and give inputs and assert outputs for. Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. All concurrent assignments can be. How to use. Vhdl Testbench Clock Example.

From www.embeddedrelated.com

VHDL tutorial part 2 Testbench Gene Breniman Vhdl Testbench Clock Example How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This allows you to easily change the pattern of the waveform that you want to feed… First, edit the constant for the clock period definition. Reading signal values from file is. Vhdl Testbench Clock Example.

From www.embeddedrelated.com

VHDL tutorial combining clocked and sequential logic Gene Breniman Vhdl Testbench Clock Example In many test benches i see the following pattern for clock generation: First, edit the constant for the clock period definition. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This example shows how to generate a clock, and give inputs and assert outputs for. How to use a clock. Vhdl Testbench Clock Example.

From www.youtube.com

Lecture 11 VHDL Testbench part 2 YouTube Vhdl Testbench Clock Example We would like this to match the 50 mhz clock that is coming into the test bench to. All concurrent assignments can be. First, edit the constant for the clock period definition. This allows you to easily change the pattern of the waveform that you want to feed… Process begin clk <= '0'; Reading signal values from file is an. Vhdl Testbench Clock Example.

From www.technobyte.org

Testbenches in VHDL A complete guide with steps Vhdl Testbench Clock Example In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. All concurrent assignments can be. We would like this to match the 50 mhz clock that is coming into the test bench to. How to use a clock and do assertions. This allows you to easily change the pattern. Vhdl Testbench Clock Example.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Vhdl Testbench Clock Example We would like this to match the 50 mhz clock that is coming into the test bench to. This allows you to easily change the pattern of the waveform that you want to feed… How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure and check. Vhdl Testbench Clock Example.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. Process begin clk <= '0'; In many test benches i see the following pattern for clock generation: All concurrent assignments can be. We would like this to match the 50 mhz clock that is coming into the test bench to. This. Vhdl Testbench Clock Example.

From electronics.stackexchange.com

vhdl How to drive a counter with clock in testbench Electrical Vhdl Testbench Clock Example In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This allows you to easily change the pattern of the waveform that you want to feed… How to use a. Vhdl Testbench Clock Example.

From electronics.stackexchange.com

vhdl How to drive a counter with clock in testbench Electrical Vhdl Testbench Clock Example In many test benches i see the following pattern for clock generation: We would like this to match the 50 mhz clock that is coming into the test bench to. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. First, edit the constant for the clock period definition.. Vhdl Testbench Clock Example.

From www.youtube.com

Writing a Testbench with a Clock in VHDL 2 Of Testbench Series YouTube Vhdl Testbench Clock Example In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This example shows how to generate a clock, and give inputs and assert outputs for. Reading signal values from file. Vhdl Testbench Clock Example.

From miscircuitos.com

How to create a testbench in Vivado to learn Verilog or VHDL Vhdl Testbench Clock Example First, edit the constant for the clock period definition. Process begin clk <= '0'; This allows you to easily change the pattern of the waveform that you want to feed… All concurrent assignments can be. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In many test benches. Vhdl Testbench Clock Example.

From technobyte.org

Testbenches in VHDL A complete guide with steps Vhdl Testbench Clock Example How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. In many test benches i see the following pattern for clock generation: This allows you to easily change the pattern of the waveform that you want to feed… Reading signal values. Vhdl Testbench Clock Example.

From embdev.net

vhdl input clock to output Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. We would like this to match the 50 mhz clock that is coming into the test bench to. This example shows how to generate a clock, and give inputs and assert outputs for. Reading signal values from file is an alternative. Vhdl Testbench Clock Example.

From www.youtube.com

How to create a timer in VHDL YouTube Vhdl Testbench Clock Example We would like this to match the 50 mhz clock that is coming into the test bench to. All concurrent assignments can be. In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. How to use a clock and do assertions. This allows you to easily change the pattern of the. Vhdl Testbench Clock Example.

From www.youtube.com

[Part 2] Synthesizable Digital Clock with 7 segment Display Decoder and Vhdl Testbench Clock Example All concurrent assignments can be. Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). This example shows how to generate a clock, and give inputs and assert outputs for. First, edit the constant for the clock period definition. In many test benches i see the following pattern for clock generation: In. Vhdl Testbench Clock Example.

From www.slideserve.com

PPT VHDL PowerPoint Presentation, free download ID226593 Vhdl Testbench Clock Example Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This allows you to easily change the pattern of the waveform that you. Vhdl Testbench Clock Example.

From www.youtube.com

VHDL BASIC Tutorial Clock Divider YouTube Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This allows you to easily change the pattern of the waveform that you want to feed… In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This example shows how. Vhdl Testbench Clock Example.

From www.embeddedrelated.com

VHDL tutorial A practical example part 3 VHDL testbench Gene Vhdl Testbench Clock Example Process begin clk <= '0'; In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. All concurrent assignments can be. How to use a clock and do assertions. Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). In almost any. Vhdl Testbench Clock Example.

From www.youtube.com

Writing Basic Testbench Code in Verilog HDL ModelSim Tutorial Vhdl Testbench Clock Example Reading signal values from file is an alternative way of generating stimuli for the device on test (dut). We would like this to match the 50 mhz clock that is coming into the test bench to. How to use a clock and do assertions. In this testbench you can have processes which are sensitive to a clock signal and measure. Vhdl Testbench Clock Example.

From www.youtube.com

VHDL tutorial for OR with Test Bench YouTube Vhdl Testbench Clock Example In this testbench you can have processes which are sensitive to a clock signal and measure and check the time between. This allows you to easily change the pattern of the waveform that you want to feed… First, edit the constant for the clock period definition. In many test benches i see the following pattern for clock generation: Reading signal. Vhdl Testbench Clock Example.

From www.youtube.com

generating clock signal for testbench in VHDL YouTube Vhdl Testbench Clock Example In almost any testbench, a clock signal is usually required in order to synchronise stimulus signals within the testbench. This allows you to easily change the pattern of the waveform that you want to feed… We would like this to match the 50 mhz clock that is coming into the test bench to. Process begin clk <= '0'; All concurrent. Vhdl Testbench Clock Example.