Clock Skew Formula . on practical chips, the rc delay of the wire resistance and gate load is very long. Skew can be defined as positive if the receiving. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. Variations in this delay cause. clock skew in synchronous digital circuit systems. Any signal takes some time to. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. In synchronous circuits where all the logic elements share the same. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network.

from www.slideserve.com

Any signal takes some time to. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. Variations in this delay cause. on practical chips, the rc delay of the wire resistance and gate load is very long. Skew can be defined as positive if the receiving. clock skew in synchronous digital circuit systems. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. In synchronous circuits where all the logic elements share the same. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects.

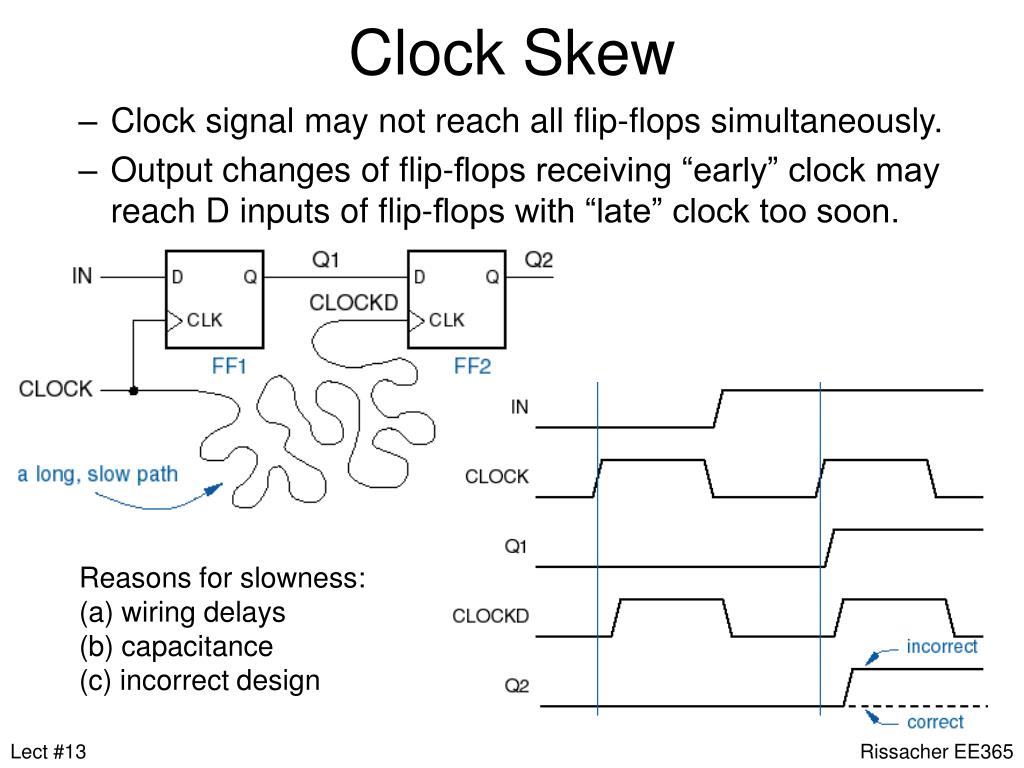

PPT EE365 Adv. Digital Circuit Design Clarkson University Lecture 13

Clock Skew Formula clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. clock skew in synchronous digital circuit systems. Any signal takes some time to. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. Skew can be defined as positive if the receiving. on practical chips, the rc delay of the wire resistance and gate load is very long. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. Variations in this delay cause. In synchronous circuits where all the logic elements share the same.

From www.slideserve.com

PPT CS 140 Lecture 11 Sequential Networks Timing and Retiming Clock Skew Formula Skew can be defined as positive if the receiving. Any signal takes some time to. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop. Clock Skew Formula.

From www.slideserve.com

PPT Clock Network Synthesis PowerPoint Presentation, free download Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. . Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID1132940 Clock Skew Formula Skew can be defined as positive if the receiving. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Formula In synchronous circuits where all the logic elements share the same. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. clock skew in synchronous digital circuit systems. in a practical clock driver there are many variables which can effect the. Clock Skew Formula.

From www.slideshare.net

Clock Skew 1 Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. on practical chips, the rc delay of the wire resistance and gate load is very long. In synchronous circuits where all the logic elements share the same. Skew can be defined as. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Formula Skew can be defined as positive if the receiving. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID1132940 Clock Skew Formula in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. Variations in this delay cause. Any signal takes some time to. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. in the simplest words, clock skew is the. Clock Skew Formula.

From www.youtube.com

Chapter13 Effect of Clock Skew on Setup & Hold Timing Equations Clock Skew Formula Variations in this delay cause. Any signal takes some time to. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. Skew can be defined as positive if the receiving. on practical chips, the rc delay of the wire resistance and gate. Clock Skew Formula.

From www.slideshare.net

Clock Skew 2 Clock Skew Formula clock skew in synchronous digital circuit systems. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. Variations in this delay cause. Any signal takes some. Clock Skew Formula.

From www.slideserve.com

PPT The clock PowerPoint Presentation, free download ID2403529 Clock Skew Formula in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. in a practical clock driver there are many variables which can. Clock Skew Formula.

From www.slideserve.com

PPT Time Synchronization using ReferenceBroadcast Synchronization Clock Skew Formula Variations in this delay cause. Skew can be defined as positive if the receiving. Any signal takes some time to. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. clock skew in synchronous digital circuit systems. on practical chips, the rc delay of. Clock Skew Formula.

From grindskills.com

How does positive and negative clock skew affect setup and hold time Clock Skew Formula Skew can be defined as positive if the receiving. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. on practical chips, the rc delay of the wire resistance and gate load is very long. clock skew in synchronous digital circuit systems. Any signal. Clock Skew Formula.

From www.slideserve.com

PPT Clock and Synchronization PowerPoint Presentation, free download Clock Skew Formula Skew can be defined as positive if the receiving. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. in a practical clock driver there are many variables which can effect the propagation delay when though paths. Clock Skew Formula.

From www.slideserve.com

PPT Chapter 10 PowerPoint Presentation, free download ID6062070 Clock Skew Formula Any signal takes some time to. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. Variations in this delay cause. on practical chips, the rc delay of the wire resistance and gate load is very long. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing. Clock Skew Formula.

From www.slideserve.com

PPT STATIC TIMING ANALYSIS PowerPoint Presentation, free download Clock Skew Formula clock skew in synchronous digital circuit systems. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the capture flop and launch flop. Any signal takes some time to. in a practical clock driver there are many variables which can effect the. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. on practical chips, the rc delay of the wire resistance and gate load is very long. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network.. Clock Skew Formula.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Clock Skewtolerant circuits Clock Skew Formula Any signal takes some time to. In synchronous circuits where all the logic elements share the same. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. Variations in this delay cause. Skew can be defined as positive if the receiving. clock. Clock Skew Formula.

From www.slideserve.com

PPT DELAY INSERTION METHOD IN CLOCK SKEW SCHEDULING PowerPoint Clock Skew Formula clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. Skew can be defined as positive if the receiving. In synchronous circuits where all the logic elements share the same. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Formula In synchronous circuits where all the logic elements share the same. Skew can be defined as positive if the receiving. on practical chips, the rc delay of the wire resistance and gate load is very long. Variations in this delay cause. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management. Clock Skew Formula.

From vlsimaster.com

Clock Skew VLSI Master Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. Variations in this delay cause. in the simplest. Clock Skew Formula.

From www.cuemath.com

Skewness Formula Learn the Formula for Skewness with Solved Examples Clock Skew Formula Skew can be defined as positive if the receiving. clock skew in synchronous digital circuit systems. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. on practical chips, the rc delay of the wire resistance and gate load is very long. In synchronous. Clock Skew Formula.

From www.slideserve.com

PPT EE365 Adv. Digital Circuit Design Clarkson University Lecture 13 Clock Skew Formula In synchronous circuits where all the logic elements share the same. Variations in this delay cause. Any signal takes some time to. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. Skew can be defined as positive if the receiving. in. Clock Skew Formula.

From www.youtube.com

Lecture2 Timing diagram for clock skew YouTube Clock Skew Formula Skew can be defined as positive if the receiving. on practical chips, the rc delay of the wire resistance and gate load is very long. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. In synchronous circuits where all the logic elements share the. Clock Skew Formula.

From www.slideshare.net

Clock Skew 2 Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. Skew can be defined as positive if the receiving. on practical chips, the rc delay of the wire resistance and gate load is very long. clock skew in synchronous digital circuit. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID3740926 Clock Skew Formula Any signal takes some time to. on practical chips, the rc delay of the wire resistance and gate load is very long. Skew can be defined as positive if the receiving. clock skew in synchronous digital circuit systems. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are. Clock Skew Formula.

From www.slideshare.net

Clock Skew 2 Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. Skew can be defined as positive if the receiving. in the simplest words, clock skew is. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Formula on practical chips, the rc delay of the wire resistance and gate load is very long. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. clock skew in synchronous digital circuit systems. Any signal takes some time to. In synchronous circuits where all. Clock Skew Formula.

From www.slideshare.net

Clock Skew 2 Clock Skew Formula Any signal takes some time to. In synchronous circuits where all the logic elements share the same. Variations in this delay cause. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. clock skew in synchronous digital circuit systems. on practical. Clock Skew Formula.

From studylib.net

Clock skew Clock Skew Formula in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. Skew can be defined as positive if the receiving. In synchronous circuits where all the logic elements share the same. clock skew is demonstrated by the insertion of a delay in the clock’s delivery network.. Clock Skew Formula.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Skew Formula clock skew in synchronous digital circuit systems. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. Any signal takes some time to. Skew can be defined as positive if the receiving. Variations in this delay cause. In synchronous circuits where all the logic elements. Clock Skew Formula.

From webdocs.cs.ualberta.ca

Clockskew calculation Clock Skew Formula Variations in this delay cause. In synchronous circuits where all the logic elements share the same. on practical chips, the rc delay of the wire resistance and gate load is very long. in the simplest words, clock skew is the time difference between arrival of the same edge of a clock signal at the clock pin of the. Clock Skew Formula.

From www.slideserve.com

PPT Signal and Timing Parameters I Common Clock Class 2 PowerPoint Clock Skew Formula understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. in a practical clock driver there are many variables which can effect the propagation delay when though paths are equivalent and these effects. In synchronous circuits where all the logic elements share. Clock Skew Formula.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Clock Skew Formula Any signal takes some time to. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. Skew can be defined as positive if the receiving. in the simplest words, clock skew is the time difference between arrival of the same edge of. Clock Skew Formula.

From www.slideshare.net

Clock Skew 2 Clock Skew Formula clock skew is demonstrated by the insertion of a delay in the clock’s delivery network. In synchronous circuits where all the logic elements share the same. Any signal takes some time to. Skew can be defined as positive if the receiving. clock skew in synchronous digital circuit systems. Variations in this delay cause. in the simplest words,. Clock Skew Formula.

From www.slideserve.com

PPT Clock Skew PowerPoint Presentation, free download ID515173 Clock Skew Formula In synchronous circuits where all the logic elements share the same. on practical chips, the rc delay of the wire resistance and gate load is very long. understanding the nuances of clock skew, differentiating between ideal and real clock trees, and employing effective management techniques are essential steps in creating robust and reliable. Any signal takes some time. Clock Skew Formula.