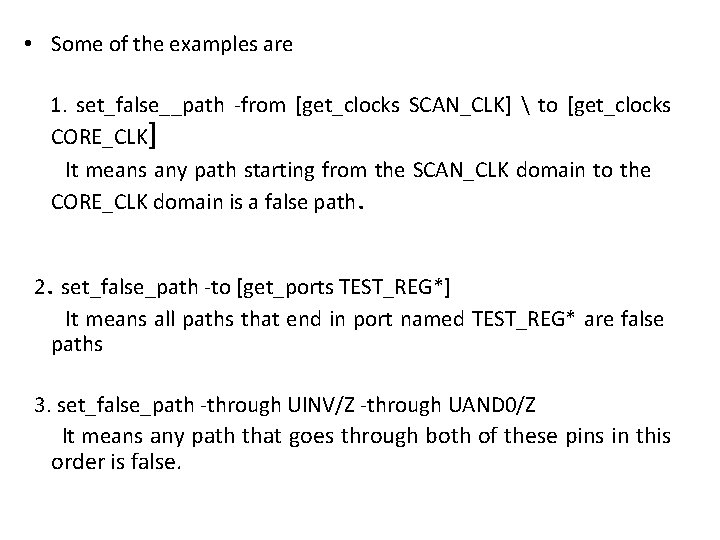

Clock Set False Path . it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. set_false_path is a timing constraints which is not required to be optimized for timing. hi, i have a question about why we need to set false path. For example, i can remove setup checks while keeping hold. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. It can be between keepers. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. set_false_path allows to remove specific constraints between clocks. you shouldn't need to use the set_false_path command, the clock groups features should be enough. We can use it for two flop synchronizer since it is not required to get. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. The tutorial writes a false path is a path that topologically exists in the design.

from slidetodoc.com

We can use it for two flop synchronizer since it is not required to get. set_false_path is a timing constraints which is not required to be optimized for timing. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. For example, i can remove setup checks while keeping hold. you shouldn't need to use the set_false_path command, the clock groups features should be enough. hi, i have a question about why we need to set false path. set_false_path allows to remove specific constraints between clocks. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. It can be between keepers.

FALSE PATH ANALYSIS AND CRITICAL PATH ANALYSIS Presented

Clock Set False Path it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. you shouldn't need to use the set_false_path command, the clock groups features should be enough. The tutorial writes a false path is a path that topologically exists in the design. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. For example, i can remove setup checks while keeping hold. set_false_path allows to remove specific constraints between clocks. set_false_path is a timing constraints which is not required to be optimized for timing. We can use it for two flop synchronizer since it is not required to get. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. hi, i have a question about why we need to set false path. It can be between keepers.

From blog.csdn.net

vivado 时序例外约束_vivado intraclock paths标红该怎么办CSDN博客 Clock Set False Path It can be between keepers. We can use it for two flop synchronizer since it is not required to get. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. hi, i have a question about why we need to set false path. For example, i. Clock Set False Path.

From www.youtube.com

SystemVerilog Asynchronous FIFO Timing Analysis, Clock Constraint Clock Set False Path hi, i have a question about why we need to set false path. set_false_path allows to remove specific constraints between clocks. you shouldn't need to use the set_false_path command, the clock groups features should be enough. The tutorial writes a false path is a path that topologically exists in the design. We can use it for two. Clock Set False Path.

From nanohub.org

Resources ECE 595Z Lecture 23 Timing Analysis and Clock Set False Path The tutorial writes a false path is a path that topologically exists in the design. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. set_false_path is a timing constraints which is not required to be optimized for timing. set_false_path allows to remove specific constraints between clocks. It can be between. Clock Set False Path.

From www.researchgate.net

Example circuit with 3 timing constraints. Download Scientific Diagram Clock Set False Path it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. It can be between keepers. hi, i have a question about why. Clock Set False Path.

From www.slideserve.com

PPT STATIC TIMING ANALYSIS PowerPoint Presentation, free download Clock Set False Path set_false_path is a timing constraints which is not required to be optimized for timing. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any. Clock Set False Path.

From zhuanlan.zhihu.com

false path和asynchronous的区别 知乎 Clock Set False Path The tutorial writes a false path is a path that topologically exists in the design. set_false_path allows to remove specific constraints between clocks. set_false_path is a timing constraints which is not required to be optimized for timing. hi, i have a question about why we need to set false path. you shouldn't need to use the. Clock Set False Path.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Clock Set False Path It can be between keepers. We can use it for two flop synchronizer since it is not required to get. set_false_path allows to remove specific constraints between clocks. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. it is essential to apply timing. Clock Set False Path.

From slidetodoc.com

FALSE PATH ANALYSIS AND CRITICAL PATH ANALYSIS Presented Clock Set False Path hi, i have a question about why we need to set false path. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any. Clock Set False Path.

From ee.mweda.com

低频时钟采高频时钟生成的脉冲 微波EDA网 Clock Set False Path The tutorial writes a false path is a path that topologically exists in the design. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. set_false_path allows to remove specific constraints between clocks. It can be between keepers. hi, i have a question about. Clock Set False Path.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Clock Set False Path the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. For example, i can remove setup checks while keeping hold. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. you. Clock Set False Path.

From www.techdesignforums.com

Symbolic simulation speeds timing closure Tech Design Forum Techniques Clock Set False Path the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. We can use it for two flop synchronizer since it is not required to get. For example, i can. Clock Set False Path.

From www.youtube.com

FALSE PATH explaination with detailed examples Static Timing Analysis Clock Set False Path The tutorial writes a false path is a path that topologically exists in the design. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any. Clock Set False Path.

From my.oschina.net

set_false_path的用法 osc_f5e60qdm的个人空间 OSCHINA 中文开源技术交流社区 Clock Set False Path We can use it for two flop synchronizer since it is not required to get. you shouldn't need to use the set_false_path command, the clock groups features should be enough. For example, i can remove setup checks while keeping hold. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test. Clock Set False Path.

From blog.csdn.net

【Time2】set_max_delay_set max delay的使用CSDN博客 Clock Set False Path it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. We can use it for two flop synchronizer since it is not required to get. It can be between keepers. The tutorial writes a false path is a path that topologically exists in the design. the. Clock Set False Path.

From ee.mweda.com

对FALSE PATH的理解 微波EDA网 Clock Set False Path you shouldn't need to use the set_false_path command, the clock groups features should be enough. The tutorial writes a false path is a path that topologically exists in the design. We can use it for two flop synchronizer since it is not required to get. the set false path (set_false_path) constraint allows you to exclude a path from. Clock Set False Path.

From blog.csdn.net

vivado 时序例外约束_vivado intraclock paths标红该怎么办CSDN博客 Clock Set False Path We can use it for two flop synchronizer since it is not required to get. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. set_false_path is a. Clock Set False Path.

From tech.tdzire.com

What are setup and hold timing checks ? What is setup and hold time Clock Set False Path For example, i can remove setup checks while keeping hold. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. hi, i. Clock Set False Path.

From www.youtube.com

sta lec22 timing exceptions part 1 false path Static Timing Clock Set False Path It can be between keepers. The tutorial writes a false path is a path that topologically exists in the design. For example, i can remove setup checks while keeping hold. you shouldn't need to use the set_false_path command, the clock groups features should be enough. hi, i have a question about why we need to set false path.. Clock Set False Path.

From blog.csdn.net

时序例外_Timing Exceptions_False Paths(set_false_path)_set false path仍然 Clock Set False Path For example, i can remove setup checks while keeping hold. We can use it for two flop synchronizer since it is not required to get. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. The tutorial writes a false path is a path that topologically exists in the design. It can be. Clock Set False Path.

From blog.csdn.net

false pathCSDN博客 Clock Set False Path hi, i have a question about why we need to set false path. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. set_false_path allows to remove specific constraints between clocks. the set_false_path command tells the timing analyzer not to analyze a path. Clock Set False Path.

From www.slideserve.com

PPT The Automatic Generation of MergedMode Design Constraints Clock Set False Path hi, i have a question about why we need to set false path. set_false_path allows to remove specific constraints between clocks. set_false_path is a timing constraints which is not required to be optimized for timing. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then. Clock Set False Path.

From www.techdesignforums.com

Identify false positive and real clock domain crossing violations Clock Set False Path it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. It can be between keepers. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. We can use it for two flop synchronizer since it is not required to get.. Clock Set False Path.

From www.youtube.com

False Path in VLSI Examples of false path Write false path Clock Set False Path you shouldn't need to use the set_false_path command, the clock groups features should be enough. We can use it for two flop synchronizer since it is not required to get. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. the set false path (set_false_path) constraint allows you to exclude a. Clock Set False Path.

From www.skfwe.cn

design compile 介绍 Clock Set False Path the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. set_false_path allows to remove specific constraints between clocks. hi, i. Clock Set False Path.

From shumin.co.kr

[Digital Logic] Static Timing Analysis (STA) Shumin Blog Clock Set False Path you shouldn't need to use the set_false_path command, the clock groups features should be enough. The tutorial writes a false path is a path that topologically exists in the design. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. it is essential to. Clock Set False Path.

From zhuanlan.zhihu.com

SDC(4)——时序特例(false_path、multicycle_path、max/min_delay) 知乎 Clock Set False Path We can use it for two flop synchronizer since it is not required to get. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. set_false_path allows to remove specific constraints between clocks. set_false_path is a timing constraints which is not required to be optimized. Clock Set False Path.

From www.skfwe.cn

design compile 介绍 Clock Set False Path It can be between keepers. set_false_path is a timing constraints which is not required to be optimized for timing. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. We can use it for two flop synchronizer since it is not required to get. For example, i can remove setup checks while. Clock Set False Path.

From ee.mweda.com

set_disable_timing 与 set_false_path 差别 微波EDA网 Clock Set False Path For example, i can remove setup checks while keeping hold. The tutorial writes a false path is a path that topologically exists in the design. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. the set_false_path command tells the timing analyzer not to analyze. Clock Set False Path.

From nanohub.org

Resources ECE 595Z Lecture 23 Timing Analysis and Clock Set False Path It can be between keepers. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. For example, i can remove setup checks while. Clock Set False Path.

From www.vrogue.co

What Are Setup And Hold Timing Checks What Is Setup A vrogue.co Clock Set False Path It can be between keepers. The tutorial writes a false path is a path that topologically exists in the design. hi, i have a question about why we need to set false path. set_false_path is a timing constraints which is not required to be optimized for timing. set_false_path allows to remove specific constraints between clocks. the. Clock Set False Path.

From www.skfwe.cn

design compile 介绍 Clock Set False Path it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. set_false_path is a timing constraints which is not required to be optimized for timing. hi, i have a question about why we need to set false path. the set false path (set_false_path) constraint allows. Clock Set False Path.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Clock Set False Path set_false_path allows to remove specific constraints between clocks. For example, i can remove setup checks while keeping hold. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test logic or any other path. hi, i have a question about why we need to set false path. We can use. Clock Set False Path.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Clock Set False Path set_false_path allows to remove specific constraints between clocks. it is essential to apply timing constraints to your multibit clock domain crossing, if this bus has a set_false_path constraint then the. For example, i can remove setup checks while keeping hold. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as. Clock Set False Path.

From shumin.co.kr

[Digital Logic] Static Timing Analysis (STA) Shumin Blog Clock Set False Path you shouldn't need to use the set_false_path command, the clock groups features should be enough. For example, i can remove setup checks while keeping hold. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. The tutorial writes a false path is a path that topologically exists in the design. the. Clock Set False Path.

From www.youtube.com

Introduction to SDC Timing Constraints YouTube Clock Set False Path It can be between keepers. the set_false_path command tells the timing analyzer not to analyze a path or group of paths. For example, i can remove setup checks while keeping hold. set_false_path allows to remove specific constraints between clocks. the set false path (set_false_path) constraint allows you to exclude a path from timing analysis, such as test. Clock Set False Path.