Example Of Clock Generator . This shows how to properly divide. Instead use a clock enable. How to generate a clock signal. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. This example shows how to generate a clock, and give inputs and assert outputs for. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. It basically separates the time related details from the structural, functional and procedural elements of a. With the arduino library installed, click on file > examples > sparkfun clock. The first example demonstrates the very basics of the sparkfun clock generator: A clocking block is a set of signals synchronised on a particular clock. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. How to use a clock and do assertions.

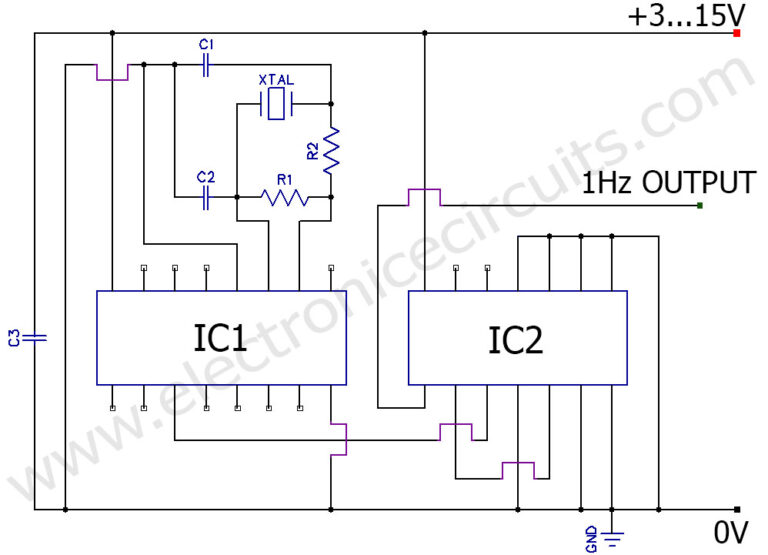

from www.electronicecircuits.com

Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. With the arduino library installed, click on file > examples > sparkfun clock. How to use a clock and do assertions. It basically separates the time related details from the structural, functional and procedural elements of a. This shows how to properly divide. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. The first example demonstrates the very basics of the sparkfun clock generator: How to generate a clock signal. Instead use a clock enable.

Precision 1Hz clock generator circuit Electronic Circuits

Example Of Clock Generator The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. How to generate a clock signal. It basically separates the time related details from the structural, functional and procedural elements of a. A clocking block is a set of signals synchronised on a particular clock. The first example demonstrates the very basics of the sparkfun clock generator: How to use a clock and do assertions. With the arduino library installed, click on file > examples > sparkfun clock. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. Instead use a clock enable. This example shows how to generate a clock, and give inputs and assert outputs for. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. This shows how to properly divide.

From www.researchgate.net

Block diagrams of the clock generator (a) and the TFF as a resettable T Example Of Clock Generator In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. With the arduino library installed, click on file > examples > sparkfun clock. Externally you can create a clock signal, but internally. Example Of Clock Generator.

From blog.tindie.com

Tindie Blog Beginner Friendly Clock Generator Kit Offers an Example Of Clock Generator In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to. Example Of Clock Generator.

From www.slideserve.com

PPT A Design Example PowerPoint Presentation, free download ID2209752 Example Of Clock Generator Instead use a clock enable. How to use a clock and do assertions. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. With the arduino library installed, click on file > examples > sparkfun clock. How to generate a clock signal. Simulations are required to operate on a given timescale that has. Example Of Clock Generator.

From www.researchgate.net

Schematic of the clock generator. Download Scientific Diagram Example Of Clock Generator A clocking block is a set of signals synchronised on a particular clock. How to generate a clock signal. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. With the arduino library installed, click on file > examples > sparkfun clock. Instead use a clock enable. This shows. Example Of Clock Generator.

From www.youtube.com

CLOCK BOX A DIY clock generator for synths, drum machines or Example Of Clock Generator Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. This shows how to properly divide. This example shows how to generate a clock, and give inputs and assert outputs for. A clocking block is a set of signals synchronised on a particular clock. The clock generator block generates a clock. Example Of Clock Generator.

From bestengineeringprojects.com

24 Hour Digital Clock and Timer Circuit Engineering Projects Example Of Clock Generator Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. A clocking block is a set of signals synchronised on a particular clock. The first example demonstrates the. Example Of Clock Generator.

From bestengineeringprojects.com

Clock Signal Generator Circuit Engineering Projects Example Of Clock Generator Instead use a clock enable. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. This example shows how to generate a clock, and give inputs and assert outputs for. In verilog, a clock. Example Of Clock Generator.

From www.researchgate.net

Clock generator architecture. Download Scientific Diagram Example Of Clock Generator It basically separates the time related details from the structural, functional and procedural elements of a. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Instead use a clock enable. A clocking block is a set of signals synchronised on a particular clock. The first example demonstrates the. Example Of Clock Generator.

From www.pinterest.fr

Free printable Clock face template for learning to tell the time Example Of Clock Generator Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. How to use a clock and do assertions. This example shows how to generate a clock, and give inputs and assert outputs for. Simulations are required to operate on a given timescale that has a. Example Of Clock Generator.

From bestengineeringprojects.com

Clock Signal Generator Circuit Engineering Projects Example Of Clock Generator Instead use a clock enable. This example shows how to generate a clock, and give inputs and assert outputs for. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. A clocking block is a set of signals synchronised on a particular clock. This shows. Example Of Clock Generator.

From miscircuitos.com

Clock generator Si5351 Example Of Clock Generator Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. How to generate a clock signal. How to use a clock and do assertions.. Example Of Clock Generator.

From 4gte.com

Stanford Research CG635 Synthesized Clock Generator Global Test Equipment Example Of Clock Generator Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. The first example demonstrates the very basics of the sparkfun clock generator: The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. This example shows how to generate a clock, and give inputs and. Example Of Clock Generator.

From www.youtube.com

How to generate clock in Verilog HDL Verilog code of clock generator Example Of Clock Generator How to use a clock and do assertions. A clocking block is a set of signals synchronised on a particular clock. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. How to generate a clock signal. The first example demonstrates the very basics of the sparkfun clock generator: In verilog, a clock. Example Of Clock Generator.

From www.learningaboutelectronics.com

How to Build a Clock Circuit with a 555 Timer Example Of Clock Generator This shows how to properly divide. Instead use a clock enable. How to generate a clock signal. A clocking block is a set of signals synchronised on a particular clock. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. It basically separates the time. Example Of Clock Generator.

From www.researchgate.net

Proposed alldigital clock generator. Download Scientific Diagram Example Of Clock Generator This shows how to properly divide. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. This example shows how to generate a clock, and give inputs and assert outputs for. A clocking block is a set of signals synchronised on a particular clock. It basically separates the time related details. Example Of Clock Generator.

From www.researchgate.net

Block diagram of the clock generator architecture used in the lpGBT Example Of Clock Generator This shows how to properly divide. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. How to generate a clock signal. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. The clock. Example Of Clock Generator.

From www.electronicecircuits.com

Precision 1Hz clock generator circuit Electronic Circuits Example Of Clock Generator How to use a clock and do assertions. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. This shows how to properly divide. This example shows how to generate a clock, and give inputs and assert outputs for. The clock generator block generates a clock signal with multiple. Example Of Clock Generator.

From www.instructables.com

Clock Generator With Si5351 and Blue Pill 6 Steps (with Pictures Example Of Clock Generator Instead use a clock enable. How to generate a clock signal. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. It basically separates the time related details from the structural, functional and procedural elements of a. This example shows how to generate a clock, and give inputs and assert outputs for. With. Example Of Clock Generator.

From www.youtube.com

Digital Clock in Quartus YouTube Example Of Clock Generator Instead use a clock enable. How to use a clock and do assertions. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. How to generate a clock signal. This shows how to properly divide. It basically separates the time related details from the structural,. Example Of Clock Generator.

From www.hpcwire.com

Renesas Unveils New Programmable Clock Generator Example Of Clock Generator How to use a clock and do assertions. The first example demonstrates the very basics of the sparkfun clock generator: It basically separates the time related details from the structural, functional and procedural elements of a. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. This example shows how to. Example Of Clock Generator.

From www.slideserve.com

PPT 8284 Clock Generator PowerPoint Presentation, free download ID Example Of Clock Generator The first example demonstrates the very basics of the sparkfun clock generator: It basically separates the time related details from the structural, functional and procedural elements of a. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. Instead use a clock enable. With the. Example Of Clock Generator.

From www.researchgate.net

The RC2NOT signal generator (a); complementary clock phases, Φ1 and Φ2 Example Of Clock Generator This shows how to properly divide. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. How to generate a clock signal. Instead use a clock enable. With the arduino library installed, click on file > examples > sparkfun clock. The clock generator block generates a clock signal with multiple output. Example Of Clock Generator.

From www.slowroom.be

ARDUINO CLOCK GENERATOR SLOWROOM Example Of Clock Generator How to generate a clock signal. It basically separates the time related details from the structural, functional and procedural elements of a. With the arduino library installed, click on file > examples > sparkfun clock. This example shows how to generate a clock, and give inputs and assert outputs for. How to use a clock and do assertions. Instead use. Example Of Clock Generator.

From www.researchgate.net

4phase interleaving clock generator (a) schematic; (b) clock phases Example Of Clock Generator It basically separates the time related details from the structural, functional and procedural elements of a. The first example demonstrates the very basics of the sparkfun clock generator: Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. In verilog, a clock generator is a module or block of code that. Example Of Clock Generator.

From www.eeweb.com

Clock Generator with 14 Outputs EE Example Of Clock Generator The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. This example shows how to generate a clock, and give inputs and assert outputs for. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Simulations are required to operate on a. Example Of Clock Generator.

From www.youtube.com

How to implement a Verilog testbench Clock Generator for sequential Example Of Clock Generator The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. How to generate a clock signal. With the arduino library installed, click on file > examples > sparkfun clock. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. It basically separates the time. Example Of Clock Generator.

From eureka.patsnap.com

Selfcalibrating quadrature clock generator and method thereof Eureka Example Of Clock Generator How to generate a clock signal. How to use a clock and do assertions. The first example demonstrates the very basics of the sparkfun clock generator: In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. This shows how to properly divide. A clocking block is a set of. Example Of Clock Generator.

From www.youtube.com

21 Verilog Clock Generator YouTube Example Of Clock Generator How to generate a clock signal. A clocking block is a set of signals synchronised on a particular clock. Instead use a clock enable. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling.. Example Of Clock Generator.

From bestengineeringprojects.com

Clock Signal Generator Circuit Engineering Projects Example Of Clock Generator Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. This shows how to properly divide. Instead use a clock enable. This example shows how to generate a clock, and give inputs and assert outputs for. It basically separates the time related details from the structural, functional and procedural elements of. Example Of Clock Generator.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale Example Of Clock Generator This shows how to properly divide. Instead use a clock enable. A clocking block is a set of signals synchronised on a particular clock. The first example demonstrates the very basics of the sparkfun clock generator: How to use a clock and do assertions. Simulations are required to operate on a given timescale that has a limited precision as specified. Example Of Clock Generator.

From learn.sparkfun.com

SparkFun Clock Generator 5P49V60 (Qwiic) Hookup Guide SparkFun Learn Example Of Clock Generator How to generate a clock signal. With the arduino library installed, click on file > examples > sparkfun clock. Instead use a clock enable. This shows how to properly divide. In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Simulations are required to operate on a given timescale. Example Of Clock Generator.

From www.youtube.com

Clock generator key parameters and specifications YouTube Example Of Clock Generator Instead use a clock enable. It basically separates the time related details from the structural, functional and procedural elements of a. Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. How to generate. Example Of Clock Generator.

From www.electroniclinic.com

How to design digital clock using counters decoders and displays Example Of Clock Generator This example shows how to generate a clock, and give inputs and assert outputs for. The clock generator block generates a clock signal with multiple output phases and detailed phase noise modeling. How to generate a clock signal. This shows how to properly divide. It basically separates the time related details from the structural, functional and procedural elements of a.. Example Of Clock Generator.

From circuitscheme.com

1 Hz Clock Generator Circuit Document Circuit Scheme Example Of Clock Generator Simulations are required to operate on a given timescale that has a limited precision as specified by the timescale. How to use a clock and do assertions. It basically separates the time related details from the structural, functional and procedural elements of a. The first example demonstrates the very basics of the sparkfun clock generator: In verilog, a clock generator. Example Of Clock Generator.

From gamma.app

Pin Diagram of 8284 Clock Generator Example Of Clock Generator In verilog, a clock generator is a module or block of code that produces clock signals for digital simulations and designs. Externally you can create a clock signal, but internally that output clock should not be used to drive the clock input to any flip flops. A clocking block is a set of signals synchronised on a particular clock. The. Example Of Clock Generator.