How To Use Clock In Systemverilog . If an input skew is mentioned for a. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is as follows (assuming you are using this in a testbench): signal directions inside a clocking block are with respect to the testbench and not the dut. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. Learn about the use and definition of. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above.

from www.youtube.com

to specify synchronization scheme and timing requirements for an interface, a clocking block is used. one way of implementing it is as follows (assuming you are using this in a testbench): clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Learn about the use and definition of. If an input skew is mentioned for a. signal directions inside a clocking block are with respect to the testbench and not the dut.

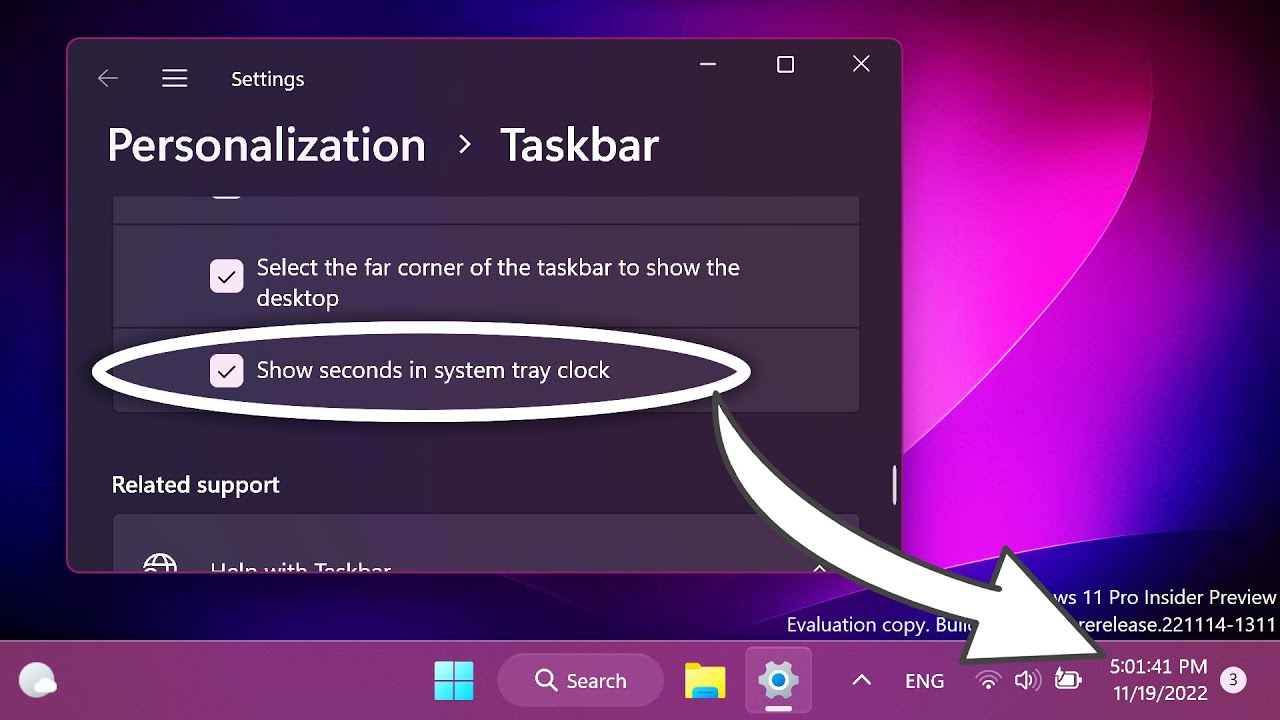

How to Enable Clock with Seconds in System Tray in Windows 11 25247

How To Use Clock In Systemverilog to specify synchronization scheme and timing requirements for an interface, a clocking block is used. If an input skew is mentioned for a. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Learn about the use and definition of. one way of implementing it is as follows (assuming you are using this in a testbench): clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. signal directions inside a clocking block are with respect to the testbench and not the dut.

From blog.csdn.net

验证systemVerilog中激励的时序(clocking)_verilog clockingCSDN博客 How To Use Clock In Systemverilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. signal directions inside a clocking block are with respect to the testbench and not the dut. systemverilog clocking block synchronize dut and testbench,. How To Use Clock In Systemverilog.

From blog.csdn.net

Clock Domain Crossing (CDC) Design & VerificationTechniques Using How To Use Clock In Systemverilog Learn about the use and definition of. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is as follows (assuming you are using this in a testbench): systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. to. How To Use Clock In Systemverilog.

From www.youtube.com

How to generate a clock in verilog testbench and syntax for timescale How To Use Clock In Systemverilog systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. signal directions inside a clocking block are with respect to the testbench and not the dut. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. clocking blocks provide a structured way to. How To Use Clock In Systemverilog.

From dokumen.tips

(PDF) SystemVerilog Assertions for ClockDomainCrossing … 2015 How To Use Clock In Systemverilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. one way of implementing it is as follows (assuming you are using this in a testbench): systemverilog clocking block synchronize dut and testbench,. How To Use Clock In Systemverilog.

From www.maven-silicon.com

What is the use of SystemVerilog assertion? Maven Silicon How To Use Clock In Systemverilog Learn about the use and definition of. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. signal directions inside a clocking block are with respect to the testbench and not the dut. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. one. How To Use Clock In Systemverilog.

From blog.csdn.net

Clock Domain Crossing (CDC) Design & VerificationTechniques Using How To Use Clock In Systemverilog If an input skew is mentioned for a. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. signal directions inside a clocking block are with respect to the testbench and not the dut. one way of implementing it is as follows (assuming you are using this in a testbench): clocking. How To Use Clock In Systemverilog.

From hdlwizard.com

How to Design a 7Segment Display in SystemVerilog HDL Wizard How To Use Clock In Systemverilog systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. signal directions inside a clocking block are with respect to the testbench and not the dut. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. Learn about the use and definition of. If. How To Use Clock In Systemverilog.

From verificationacademy.com

How to write SVA when the antecedent is changing at the same time when How To Use Clock In Systemverilog one way of implementing it is as follows (assuming you are using this in a testbench): clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. signal directions inside a clocking. How To Use Clock In Systemverilog.

From electronics.stackexchange.com

fpga FSM implementation using single always block in Verilog How To Use Clock In Systemverilog Learn about the use and definition of. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. If an input skew is mentioned for a. signal directions inside a clocking block are with respect to the testbench and not the dut. clocking blocks provide a structured way to handle clock domains and. How To Use Clock In Systemverilog.

From www.youtube.com

21 Verilog Clock Generator YouTube How To Use Clock In Systemverilog Learn about the use and definition of. one way of implementing it is as follows (assuming you are using this in a testbench): to specify synchronization scheme and timing requirements for an interface, a clocking block is used. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. systemverilog. How To Use Clock In Systemverilog.

From verificationacademy.com

Multi clock domain ,assertion SystemVerilog Verification Academy How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. Learn about the use and definition of. If an input skew is mentioned for a. the following verilog clock generator module has three parameters to. How To Use Clock In Systemverilog.

From stackoverflow.com

system verilog How to verify frequency with UVM/Systemverilog Stack How To Use Clock In Systemverilog Learn about the use and definition of. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. signal directions inside a clocking block are with respect to the testbench and not the dut. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. the following verilog. How To Use Clock In Systemverilog.

From www.researchgate.net

The SystemVerilog Event Queue with Regions Download Scientific Diagram How To Use Clock In Systemverilog If an input skew is mentioned for a. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. Learn about the use and definition of. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. one way of implementing it is as follows (assuming you. How To Use Clock In Systemverilog.

From verificationacademy.com

Testbench signal driving right at clock edge, how does the simulator How To Use Clock In Systemverilog signal directions inside a clocking block are with respect to the testbench and not the dut. one way of implementing it is as follows (assuming you are using this in a testbench): clocking blocks provide a structured way to handle clock domains and the associated timing constraints. to specify synchronization scheme and timing requirements for an. How To Use Clock In Systemverilog.

From www.scribd.com

1.given An Input Clock of 1Mhz, Convert It To 1Hz For Timer. Please How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is as follows (assuming you are using this in a testbench): If an input skew is mentioned for a. Learn about the use and definition of. systemverilog clocking block synchronize dut and testbench, ensuring signal. How To Use Clock In Systemverilog.

From blog.csdn.net

跨时钟域处理解析(一)(Clock Domain Crossing (CDC) Design & Verification How To Use Clock In Systemverilog Learn about the use and definition of. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is as follows (assuming you are using this in a testbench): to specify synchronization scheme and timing requirements for an interface, a clocking block is used. systemverilog. How To Use Clock In Systemverilog.

From www.youtube.com

Clocking Multiple Audio Interfaces with a Mastering Clock YouTube How To Use Clock In Systemverilog systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. If an input skew is mentioned for a. Learn about the use and definition of. one way of implementing it is as follows (assuming you are using this in a testbench): signal directions inside a clocking block are with respect to the. How To Use Clock In Systemverilog.

From courses.cs.washington.edu

Structural Verilog How To Use Clock In Systemverilog to specify synchronization scheme and timing requirements for an interface, a clocking block is used. one way of implementing it is as follows (assuming you are using this in a testbench): Learn about the use and definition of. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. the. How To Use Clock In Systemverilog.

From www.reddit.com

Systemverilog Assertion Default Clock statement r/FPGA How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. Learn about the use and definition of. one way of implementing it is as follows (assuming you are using this in a testbench): signal. How To Use Clock In Systemverilog.

From verificationguide.com

SystemVerilog Scheduling Semantics Verification Guide How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. Learn about the use and definition of. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. If an input skew is mentioned for a. clocking blocks provide a structured way to. How To Use Clock In Systemverilog.

From laxener.weebly.com

Timeformat Systemverilog laxener How To Use Clock In Systemverilog signal directions inside a clocking block are with respect to the testbench and not the dut. Learn about the use and definition of. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. systemverilog. How To Use Clock In Systemverilog.

From slideplayer.com

Lecture 2 Continuation of SystemVerilog ppt download How To Use Clock In Systemverilog If an input skew is mentioned for a. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. one way of implementing it is as follows (assuming you are using this in a testbench):. How To Use Clock In Systemverilog.

From www.cnblogs.com

systemverilog testbench wudayemen 博客园 How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is as follows (assuming you are using this in a testbench): signal directions inside a clocking block are with respect to the testbench and not the dut. clocking blocks provide a structured way to. How To Use Clock In Systemverilog.

From www.programmersought.com

Synchronous FIFO memory verilog implementation Programmer Sought How To Use Clock In Systemverilog Learn about the use and definition of. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. signal directions inside a clocking block are with respect to the testbench and not the dut. If an input skew is mentioned for a. clocking blocks allow inputs to be sampled and outputs to be. How To Use Clock In Systemverilog.

From stackoverflow.com

verilog How to understand which SystemVerilog is supported by Cadence How To Use Clock In Systemverilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. If an input skew is mentioned for a. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock. How To Use Clock In Systemverilog.

From www.researchgate.net

UVMBased Verification of a MixedSignal Design Using SystemVerilog How To Use Clock In Systemverilog systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. to specify synchronization scheme and timing. How To Use Clock In Systemverilog.

From blog.csdn.net

Clock Domain Crossing (CDC) Design & VerificationTechniques Using How To Use Clock In Systemverilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is. How To Use Clock In Systemverilog.

From www.youtube.com

Course Systemverilog Verification 2 L4.1 Clocking Blocks in How To Use Clock In Systemverilog clocking blocks provide a structured way to handle clock domains and the associated timing constraints. If an input skew is mentioned for a. Learn about the use and definition of. clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. the following verilog clock generator module has three parameters to. How To Use Clock In Systemverilog.

From www.academia.edu

(PDF) Clock Domain Crossing (CDC) Design & Verification Techniques How To Use Clock In Systemverilog clocking blocks provide a structured way to handle clock domains and the associated timing constraints. Learn about the use and definition of. the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. If an. How To Use Clock In Systemverilog.

From www.youtube.com

Course Systemverilog Foundations10.3 Clock and Reset Generation How To Use Clock In Systemverilog the following verilog clock generator module has three parameters to tweak the three different properties as discussed above. signal directions inside a clocking block are with respect to the testbench and not the dut. clocking blocks provide a structured way to handle clock domains and the associated timing constraints. one way of implementing it is as. How To Use Clock In Systemverilog.

From fercow.weebly.com

Clock divider mux verilog fercow How To Use Clock In Systemverilog to specify synchronization scheme and timing requirements for an interface, a clocking block is used. one way of implementing it is as follows (assuming you are using this in a testbench): signal directions inside a clocking block are with respect to the testbench and not the dut. Learn about the use and definition of. clocking blocks. How To Use Clock In Systemverilog.

From electronics.stackexchange.com

verilog posedge clk vs. posedge clk, posedge reset Electrical How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. to specify synchronization scheme and timing requirements for an interface, a clocking block is used. If an input skew is mentioned for a. Learn about the use and definition of. signal directions inside a clocking block are with respect to. How To Use Clock In Systemverilog.

From www.cnblogs.com

systemverilog testbench wudayemen 博客园 How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. signal directions inside a clocking block are with respect to the testbench and not the dut. systemverilog clocking block synchronize dut and testbench, ensuring signal sampling and driving times, preventing race. Learn about the use and definition of. clocking. How To Use Clock In Systemverilog.

From www.youtube.com

SystemVerilog Asynchronous FIFO Timing Analysis, Clock Constraint How To Use Clock In Systemverilog one way of implementing it is as follows (assuming you are using this in a testbench): clocking blocks provide a structured way to handle clock domains and the associated timing constraints. signal directions inside a clocking block are with respect to the testbench and not the dut. Learn about the use and definition of. systemverilog clocking. How To Use Clock In Systemverilog.

From www.youtube.com

How to Enable Clock with Seconds in System Tray in Windows 11 25247 How To Use Clock In Systemverilog clocking blocks allow inputs to be sampled and outputs to be driven at a specified clock event. one way of implementing it is as follows (assuming you are using this in a testbench): to specify synchronization scheme and timing requirements for an interface, a clocking block is used. the following verilog clock generator module has three. How To Use Clock In Systemverilog.