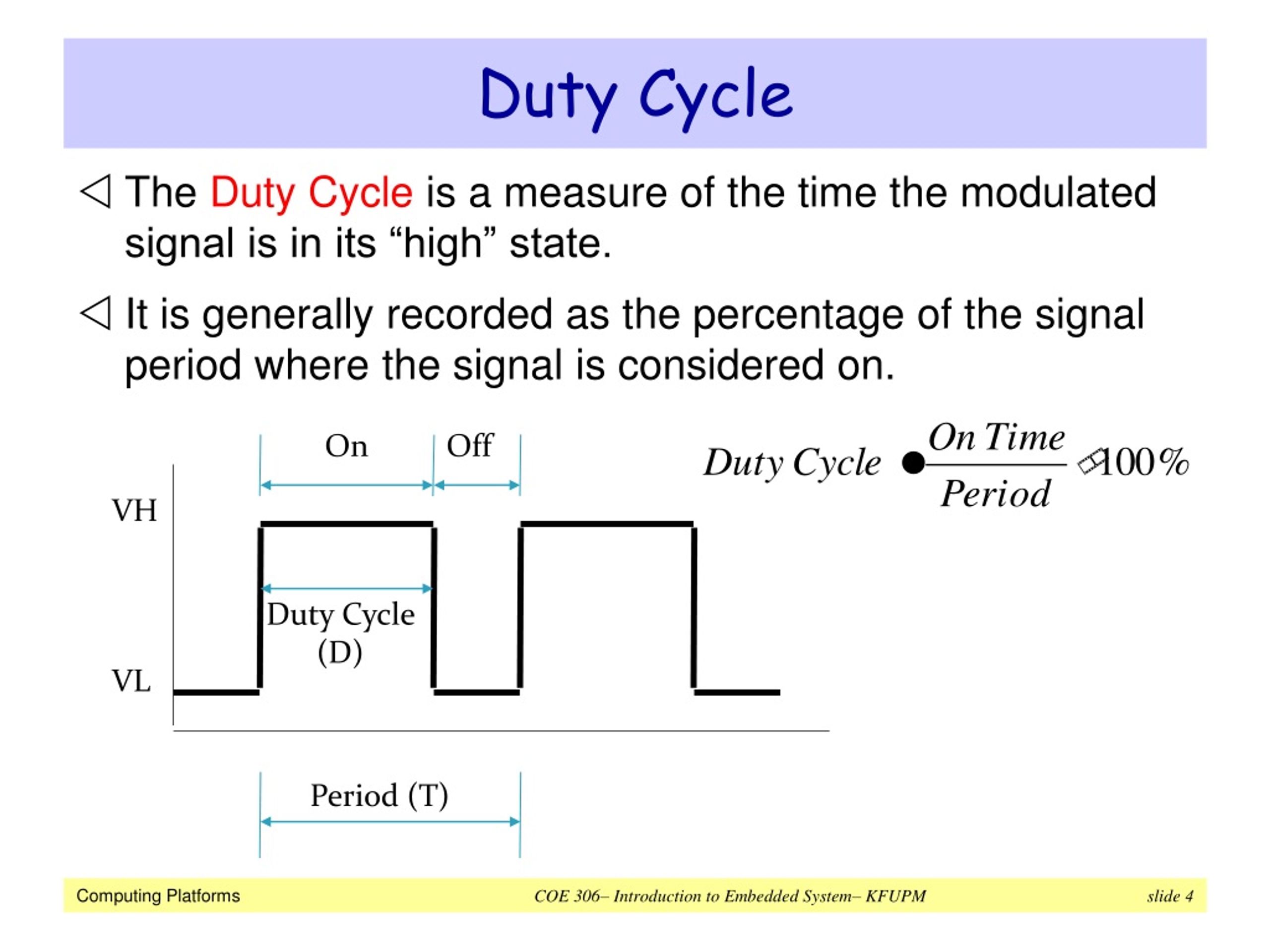

Duty Cycle In Vlsi . Duty cycle = (4μs / 10μs) ×. Phase alignment with the external clock, and duty cycle variation. there are two difficulties with this technique: the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. For instance, figure below shows a clock having an active state of. the basic definition of duty cycle is on_time/(on_time+ off_time). The on time and off time totally depends upon the rise transition. The rise and fall transitions determine the duration of. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: Clock buffer has an equal rise and fall time. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. duty cycle of a clock is normally expressed as a percentage.

from www.slideserve.com

For instance, figure below shows a clock having an active state of. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. the basic definition of duty cycle is on_time/(on_time+ off_time). there are two difficulties with this technique: For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: duty cycle of a clock is normally expressed as a percentage. The on time and off time totally depends upon the rise transition. The rise and fall transitions determine the duration of. Phase alignment with the external clock, and duty cycle variation. Duty cycle = (4μs / 10μs) ×.

PPT Pulse Width Modulation PowerPoint Presentation, free download ID8884145

Duty Cycle In Vlsi the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. Phase alignment with the external clock, and duty cycle variation. the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: Duty cycle = (4μs / 10μs) ×. The on time and off time totally depends upon the rise transition. there are two difficulties with this technique: duty cycle of a clock is normally expressed as a percentage. Clock buffer has an equal rise and fall time. the basic definition of duty cycle is on_time/(on_time+ off_time). The rise and fall transitions determine the duration of. For instance, figure below shows a clock having an active state of. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers.

From vlsiuniverse.blogspot.com

Cycle to cycle jitter VLSI n EDA Duty Cycle In Vlsi there are two difficulties with this technique: Phase alignment with the external clock, and duty cycle variation. The rise and fall transitions determine the duration of. The on time and off time totally depends upon the rise transition. Duty cycle = (4μs / 10μs) ×. duty cycle of a clock is normally expressed as a percentage. the. Duty Cycle In Vlsi.

From www.chegg.com

please help me Project Technical Report Duty Cycle In Vlsi For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: Clock buffer has an equal rise and fall time. there are two difficulties with this technique: The on time and off time totally depends upon the rise transition. The rise and fall transitions determine the duration of. duty cycle of. Duty Cycle In Vlsi.

From www.slideserve.com

PPT PWM Pulse Width Modulation PowerPoint Presentation, free download ID1612858 Duty Cycle In Vlsi For instance, figure below shows a clock having an active state of. Clock buffer has an equal rise and fall time. there are two difficulties with this technique: the basic definition of duty cycle is on_time/(on_time+ off_time). The rise and fall transitions determine the duration of. The on time and off time totally depends upon the rise transition.. Duty Cycle In Vlsi.

From www.slideserve.com

PPT Dr. Eric Bogatin , Signal Integrity Evangelist, Teledyne LeCroy PowerPoint Presentation Duty Cycle In Vlsi Clock buffer has an equal rise and fall time. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. The rise and fall transitions determine the duration of. there are two difficulties with this technique: Duty cycle = (4μs / 10μs) ×. the clock buffers are designed with some. Duty Cycle In Vlsi.

From vlsiuniverse.blogspot.com

Duty cycle degradation Duty Cycle In Vlsi there are two difficulties with this technique: Duty cycle = (4μs / 10μs) ×. For instance, figure below shows a clock having an active state of. Clock buffer has an equal rise and fall time. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: duty cycle of a clock. Duty Cycle In Vlsi.

From siliconvlsi.com

Duty Cycle & Pulse Width Siliconvlsi Duty Cycle In Vlsi The rise and fall transitions determine the duration of. the basic definition of duty cycle is on_time/(on_time+ off_time). For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less. Duty Cycle In Vlsi.

From www.youtube.com

Duty Cycle explained YouTube Duty Cycle In Vlsi The rise and fall transitions determine the duration of. The on time and off time totally depends upon the rise transition. For instance, figure below shows a clock having an active state of. the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt. Duty Cycle In Vlsi.

From 43.204.219.146

SOC Design Life Cycle VLSI Chip 2021 VLSI UNIVERSE Duty Cycle In Vlsi the basic definition of duty cycle is on_time/(on_time+ off_time). The rise and fall transitions determine the duration of. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: Duty cycle = (4μs. Duty Cycle In Vlsi.

From www.scirp.org

Derivation of a Representative Engine Duty Cycle from OnRoad HeavyDuty Vehicle Driving Data Duty Cycle In Vlsi The rise and fall transitions determine the duration of. Clock buffer has an equal rise and fall time. the basic definition of duty cycle is on_time/(on_time+ off_time). there are two difficulties with this technique: Duty cycle = (4μs / 10μs) ×. duty cycle of a clock is normally expressed as a percentage. Phase alignment with the external. Duty Cycle In Vlsi.

From www.youtube.com

What is Duty Cycle? YouTube Duty Cycle In Vlsi The rise and fall transitions determine the duration of. duty cycle of a clock is normally expressed as a percentage. there are two difficulties with this technique: the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. Duty cycle. Duty Cycle In Vlsi.

From ivlsi.com

Duty Cycle & Pulse Width in VLSI Physical Design Duty Cycle In Vlsi For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. Duty cycle = (4μs / 10μs) ×. The rise and fall transitions determine. Duty Cycle In Vlsi.

From vlsiuniverse.blogspot.com

Duty cycle careabouts for clock paths in reset assertion Duty Cycle In Vlsi This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. duty cycle of a clock is normally expressed as a percentage. the basic definition of duty cycle is on_time/(on_time+ off_time). Phase alignment with the external clock, and duty cycle variation. For instance, figure below shows a clock having an. Duty Cycle In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Duty Cycle In Vlsi duty cycle of a clock is normally expressed as a percentage. there are two difficulties with this technique: For instance, figure below shows a clock having an active state of. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: the clock buffers are designed with some special property. Duty Cycle In Vlsi.

From vlsiuniverse.blogspot.com

Duty cycle degradation Duty Cycle In Vlsi Phase alignment with the external clock, and duty cycle variation. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: The on time and off time totally depends upon the rise transition. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. . Duty Cycle In Vlsi.

From vlsiuniverse.blogspot.com

2017 VLSI n EDA Duty Cycle In Vlsi there are two difficulties with this technique: The rise and fall transitions determine the duration of. Duty cycle = (4μs / 10μs) ×. The on time and off time totally depends upon the rise transition. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: Clock buffer has an equal rise. Duty Cycle In Vlsi.

From www.slideserve.com

PPT Pulse Width Modulation PowerPoint Presentation, free download ID8884145 Duty Cycle In Vlsi For instance, figure below shows a clock having an active state of. there are two difficulties with this technique: Duty cycle = (4μs / 10μs) ×. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: Phase alignment with the external clock, and duty cycle variation. the basic definition of. Duty Cycle In Vlsi.

From 3roam.com

Duty Cycle Calculator (with Examples) Duty Cycle In Vlsi The rise and fall transitions determine the duration of. Clock buffer has an equal rise and fall time. the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. This prevents the duty cycle of clock signal from changing when it passes. Duty Cycle In Vlsi.

From www.slideshare.net

Duty Cycle Corrector Using Pulse Width Modulation PDF Duty Cycle In Vlsi Phase alignment with the external clock, and duty cycle variation. The on time and off time totally depends upon the rise transition. Duty cycle = (4μs / 10μs) ×. The rise and fall transitions determine the duration of. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. the clock. Duty Cycle In Vlsi.

From www.themechatronicsblog.com

VLSI Design Flow A Complete Overview The Mechatronics Blog Duty Cycle In Vlsi the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. duty cycle of a clock is normally expressed as a percentage. Clock buffer has an equal rise and fall time. The on time and off time totally depends upon the. Duty Cycle In Vlsi.

From www.mdpi.com

Electronics Free FullText Design and Implementation of Fast Locking AllDigital Duty Cycle Duty Cycle In Vlsi Duty cycle = (4μs / 10μs) ×. Phase alignment with the external clock, and duty cycle variation. The rise and fall transitions determine the duration of. duty cycle of a clock is normally expressed as a percentage. Clock buffer has an equal rise and fall time. For instance, figure below shows a clock having an active state of. . Duty Cycle In Vlsi.

From verificationexcellence.in

VLSI Design Front end vs back end Differences and career opportunities Duty Cycle In Vlsi the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. duty cycle of a clock is normally expressed as a percentage. The rise and fall transitions determine the duration of. there are two difficulties with this technique: For instance,. Duty Cycle In Vlsi.

From www.scribd.com

Technical Proficiency Andtraining1 Vlsi Minor Project1 On PWM Generator With Variable Duty Duty Cycle In Vlsi Phase alignment with the external clock, and duty cycle variation. duty cycle of a clock is normally expressed as a percentage. The rise and fall transitions determine the duration of. The on time and off time totally depends upon the rise transition. This prevents the duty cycle of clock signal from changing when it passes through a chain of. Duty Cycle In Vlsi.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Timing Constraints Duty Cycle In Vlsi For instance, figure below shows a clock having an active state of. there are two difficulties with this technique: Clock buffer has an equal rise and fall time. Phase alignment with the external clock, and duty cycle variation. The on time and off time totally depends upon the rise transition. the clock buffers are designed with some special. Duty Cycle In Vlsi.

From www.researchgate.net

The plot of the rectangular wave's duty cycle when ref V variation. Download Scientific Diagram Duty Cycle In Vlsi For instance, figure below shows a clock having an active state of. The rise and fall transitions determine the duration of. there are two difficulties with this technique: the basic definition of duty cycle is on_time/(on_time+ off_time). Clock buffer has an equal rise and fall time. The on time and off time totally depends upon the rise transition.. Duty Cycle In Vlsi.

From www.slideserve.com

PPT EE 201A/EE298 Modeling and Optimization for VLSI Layout PowerPoint Presentation ID296202 Duty Cycle In Vlsi This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. Phase alignment with the external clock, and duty cycle variation. Clock buffer has an equal rise and fall time. the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and. Duty Cycle In Vlsi.

From www.firgelliauto.com

What is DUTY CYCLE in a linear actuator? FIRGELLI Duty Cycle In Vlsi there are two difficulties with this technique: the basic definition of duty cycle is on_time/(on_time+ off_time). Duty cycle = (4μs / 10μs) ×. For instance, figure below shows a clock having an active state of. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: The rise and fall transitions. Duty Cycle In Vlsi.

From www.ni.com

Digital Timing Clock Signals, Jitter, Hystereisis, and Eye Diagrams National Instruments Duty Cycle In Vlsi the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. For instance, figure below shows a clock having an active state of. Clock buffer has an equal rise and fall time. duty cycle of a clock is normally expressed as. Duty Cycle In Vlsi.

From www.vedantu.com

PWM (Pulse Width Modulation) Learn Important Terms and Concepts Duty Cycle In Vlsi there are two difficulties with this technique: The rise and fall transitions determine the duration of. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: duty cycle of a clock is normally expressed as a percentage. Phase alignment with the external clock, and duty cycle variation. Clock buffer has. Duty Cycle In Vlsi.

From dxogtuehg.blob.core.windows.net

What Is Duty Cycle In Function Generator at Raymond Byrd blog Duty Cycle In Vlsi the basic definition of duty cycle is on_time/(on_time+ off_time). The on time and off time totally depends upon the rise transition. there are two difficulties with this technique: The rise and fall transitions determine the duration of. duty cycle of a clock is normally expressed as a percentage. For instance, figure below shows a clock having an. Duty Cycle In Vlsi.

From 8.136.218.141

Static Timing Analysis Physical Design VLSI BackEnd Adventure Duty Cycle In Vlsi The rise and fall transitions determine the duration of. the basic definition of duty cycle is on_time/(on_time+ off_time). Duty cycle = (4μs / 10μs) ×. For instance, figure below shows a clock having an active state of. Phase alignment with the external clock, and duty cycle variation. there are two difficulties with this technique: Clock buffer has an. Duty Cycle In Vlsi.

From www.researchgate.net

Duty cycle paradigm. The low duty cycle (20) matches the high duty... Download Scientific Diagram Duty Cycle In Vlsi Duty cycle = (4μs / 10μs) ×. Clock buffer has an equal rise and fall time. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. The rise and fall transitions determine the duration of. For a signal with a period of 10μs and a pulse width of 4μs, the duty. Duty Cycle In Vlsi.

From www.researchgate.net

Duty cycle shape chart (a) Each duty cycle, (b) Total duty cycles with... Download Scientific Duty Cycle In Vlsi Clock buffer has an equal rise and fall time. For a signal with a period of 10μs and a pulse width of 4μs, the duty cycle is: duty cycle of a clock is normally expressed as a percentage. The on time and off time totally depends upon the rise transition. Duty cycle = (4μs / 10μs) ×. The rise. Duty Cycle In Vlsi.

From www.researchgate.net

Thiophene degradation (187 W and 20 duty cycle) (a) 15 min; (b) 30... Download Scientific Duty Cycle In Vlsi For instance, figure below shows a clock having an active state of. the clock buffers are designed with some special property like high drive strength, equal rise and fall time, less delay and less delay variation with pvt and ocv. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers.. Duty Cycle In Vlsi.

From slidetodoc.com

VLSI DESIGN FLOW Introduction What is VLSI VLSI Duty Cycle In Vlsi Clock buffer has an equal rise and fall time. The rise and fall transitions determine the duration of. The on time and off time totally depends upon the rise transition. This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. For a signal with a period of 10μs and a pulse. Duty Cycle In Vlsi.

From www.youtube.com

how to check duty cycle distortion & min pulse width VLSI timing YouTube Duty Cycle In Vlsi This prevents the duty cycle of clock signal from changing when it passes through a chain of clock buffers. the basic definition of duty cycle is on_time/(on_time+ off_time). For instance, figure below shows a clock having an active state of. there are two difficulties with this technique: duty cycle of a clock is normally expressed as a. Duty Cycle In Vlsi.