Clock Distribution Network Skew . And possibly an inverter for clk’. The two main design parameters. on a small chip, the clock distribution network is just a wire. Minimum and maximum timing constraints are. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. clock distribution networks has become critical in maintaining the performance growth. derstand how clock distribution networks interact with data paths.

from www.semanticscholar.org

on a small chip, the clock distribution network is just a wire. derstand how clock distribution networks interact with data paths. Minimum and maximum timing constraints are. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. And possibly an inverter for clk’. The two main design parameters. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks has become critical in maintaining the performance growth.

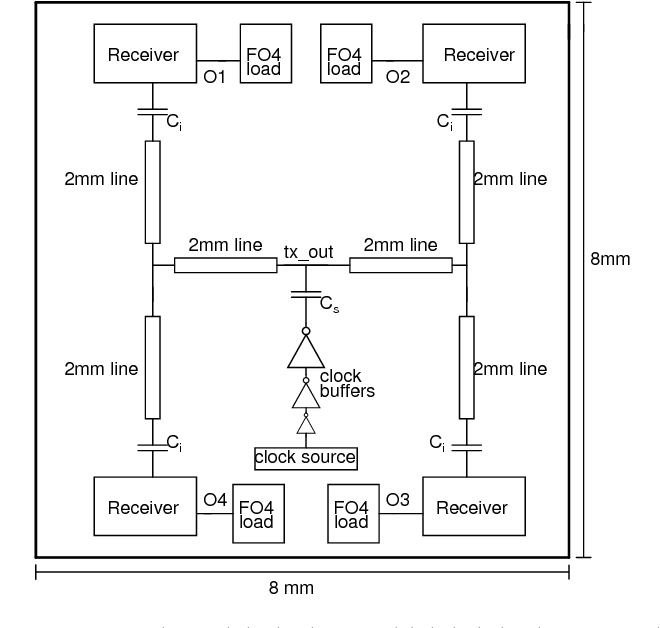

Figure 1 from A capacitively coupled clock distribution network with correction for process

Clock Distribution Network Skew clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. Minimum and maximum timing constraints are. on a small chip, the clock distribution network is just a wire. And possibly an inverter for clk’. derstand how clock distribution networks interact with data paths. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth.

From www.slideserve.com

PPT 1. Clocking Schemes and Storage Elements 2. Clock Distribution Network PowerPoint Clock Distribution Network Skew derstand how clock distribution networks interact with data paths. The two main design parameters. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. on a small chip, the clock distribution network is just a wire. Minimum and maximum timing constraints are. because of the unbalanced delays in. Clock Distribution Network Skew.

From www.slideserve.com

PPT A Global Minimum Clock Distribution Network Augmentation Algorithm for Guaranteed Clock Clock Distribution Network Skew Minimum and maximum timing constraints are. on a small chip, the clock distribution network is just a wire. And possibly an inverter for clk’. clock distribution networks has become critical in maintaining the performance growth. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j. Clock Distribution Network Skew.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Network Technical Articles Clock Distribution Network Skew on a small chip, the clock distribution network is just a wire. The two main design parameters. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. derstand how clock distribution networks interact with data paths. And possibly an inverter for clk’. . Clock Distribution Network Skew.

From www.researchgate.net

Clock skew of the different clock distribution networks with nonuniform... Download Scientific Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. And possibly an inverter for clk’. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth. clock distribution networks are subject to clock skew due to process,. Clock Distribution Network Skew.

From www.researchgate.net

Simulated full clock distribution latency and skew over PM clock grid... Download Scientific Clock Distribution Network Skew derstand how clock distribution networks interact with data paths. clock distribution networks has become critical in maintaining the performance growth. Minimum and maximum timing constraints are. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. because of the unbalanced delays in the clock distribution network, clock edges. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock and Synchronization PowerPoint Presentation, free download ID3403152 Clock Distribution Network Skew clock distribution networks has become critical in maintaining the performance growth. on a small chip, the clock distribution network is just a wire. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. derstand how clock distribution networks interact with data paths. The two main design parameters. . Clock Distribution Network Skew.

From www.researchgate.net

(PDF) Adaptive wire adjustment for bounded skew Clock Distribution Network Clock Distribution Network Skew derstand how clock distribution networks interact with data paths. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. The two main design parameters. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. . Clock Distribution Network Skew.

From slideplayer.com

Reducing Clock Skew Variability via Cross Links ppt download Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. Minimum and maximum timing constraints are. derstand how clock distribution networks interact with data paths.. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock and Power PowerPoint Presentation, free download ID417576 Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. on a small chip, the clock distribution network is just a wire. derstand how clock distribution networks interact with data paths. The two main design parameters. Minimum and maximum timing constraints are. . Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Clock Distribution Network Skew The two main design parameters. Minimum and maximum timing constraints are. clock distribution networks has become critical in maintaining the performance growth. on a small chip, the clock distribution network is just a wire. derstand how clock distribution networks interact with data paths. And possibly an inverter for clk’. because of the unbalanced delays in the. Clock Distribution Network Skew.

From www.slideserve.com

PPT A Global Minimum Clock Distribution Network Augmentation Algorithm for Guaranteed Clock Clock Distribution Network Skew The two main design parameters. And possibly an inverter for clk’. on a small chip, the clock distribution network is just a wire. Minimum and maximum timing constraints are. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks are. Clock Distribution Network Skew.

From www.researchgate.net

Histogram of clock skew distribution for the clock networks using 1 TSV... Download Scientific Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. Minimum and maximum timing constraints are. on a small chip, the clock distribution network is just a wire. clock distribution networks has become critical in maintaining the performance growth. And possibly an inverter. Clock Distribution Network Skew.

From www.slideserve.com

PPT A Global Minimum Clock Distribution Network Augmentation Algorithm for Guaranteed Clock Clock Distribution Network Skew And possibly an inverter for clk’. The two main design parameters. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. clock distribution networks has become critical in maintaining the performance growth. Minimum and maximum timing constraints are. on a small chip, the clock distribution network is just a. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. And possibly an inverter for clk’. on a small chip, the clock distribution network is just a wire. clock distribution networks has become critical in maintaining the performance growth. The two main design. Clock Distribution Network Skew.

From www.slideserve.com

PPT A Global Minimum Clock Distribution Network Augmentation Algorithm for Guaranteed Clock Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth. derstand how clock distribution networks interact with data paths. clock distribution networks are subject to clock. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID830138 Clock Distribution Network Skew because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. And possibly an inverter for clk’. derstand how clock distribution networks interact with data paths.. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock and Synchronization PowerPoint Presentation, free download ID3403152 Clock Distribution Network Skew The two main design parameters. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. And possibly an inverter for clk’. Minimum and maximum timing constraints are. clock distribution networks has become critical in maintaining the performance growth. because of the unbalanced delays in the clock distribution network, clock. Clock Distribution Network Skew.

From www.researchgate.net

Global clock distribution network, consisting of 16 resonant clock... Download Scientific Diagram Clock Distribution Network Skew clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. on a small chip, the clock distribution network is just a wire. The two main design parameters. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clocking & Timing PowerPoint Presentation, free download ID4060103 Clock Distribution Network Skew The two main design parameters. on a small chip, the clock distribution network is just a wire. And possibly an inverter for clk’. derstand how clock distribution networks interact with data paths. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. Minimum. Clock Distribution Network Skew.

From www.slideserve.com

PPT A Global Minimum Clock Distribution Network Augmentation Algorithm for Guaranteed Clock Clock Distribution Network Skew Minimum and maximum timing constraints are. on a small chip, the clock distribution network is just a wire. derstand how clock distribution networks interact with data paths. And possibly an inverter for clk’. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure.. Clock Distribution Network Skew.

From www.scribd.com

A Clock Distribution Network For Microprocessors B. Local Skew PDF Integrated Circuit Clock Distribution Network Skew on a small chip, the clock distribution network is just a wire. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. And possibly an. Clock Distribution Network Skew.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Network Technical Articles Clock Distribution Network Skew And possibly an inverter for clk’. Minimum and maximum timing constraints are. derstand how clock distribution networks interact with data paths. on a small chip, the clock distribution network is just a wire. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth. clock distribution networks are subject to clock. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clocking & Timing PowerPoint Presentation, free download ID4060103 Clock Distribution Network Skew The two main design parameters. And possibly an inverter for clk’. clock distribution networks has become critical in maintaining the performance growth. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. on a small chip, the clock distribution network is just a. Clock Distribution Network Skew.

From www.semanticscholar.org

Figure 1 from A capacitively coupled clock distribution network with correction for process Clock Distribution Network Skew Minimum and maximum timing constraints are. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. derstand how clock distribution networks interact with data paths.. Clock Distribution Network Skew.

From www.researchgate.net

(PDF) Multidomain clock skew schedulingaware register placement to optimize clock distribution Clock Distribution Network Skew And possibly an inverter for clk’. Minimum and maximum timing constraints are. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. derstand how clock distribution networks interact with data paths. because. Clock Distribution Network Skew.

From www.slideserve.com

PPT A Global Minimum Clock Distribution Network Augmentation Algorithm for Guaranteed Clock Clock Distribution Network Skew derstand how clock distribution networks interact with data paths. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. on a small chip, the clock distribution network is just a wire. clock distribution networks are subject to clock skew due to process,. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock Distribution PowerPoint Presentation, free download ID403590 Clock Distribution Network Skew on a small chip, the clock distribution network is just a wire. derstand how clock distribution networks interact with data paths. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks has become critical in maintaining the performance growth.. Clock Distribution Network Skew.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Network Technical Articles Clock Distribution Network Skew clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. derstand how clock distribution networks interact with data paths. on a small chip, the clock distribution network is just a wire. Minimum and maximum timing constraints are. And possibly an inverter for clk’. clock distribution networks has become. Clock Distribution Network Skew.

From www.allaboutcircuits.com

What is Clock Skew? Understanding Clock Skew in a Clock Distribution Network Technical Articles Clock Distribution Network Skew on a small chip, the clock distribution network is just a wire. The two main design parameters. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks has become critical in maintaining the performance growth. Minimum and maximum timing constraints. Clock Distribution Network Skew.

From www.semanticscholar.org

Figure 1 from Multidomain clock skew schedulingaware register placement to optimize clock Clock Distribution Network Skew on a small chip, the clock distribution network is just a wire. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. derstand how clock distribution networks interact with data paths. The two main design parameters. clock distribution networks are subject to. Clock Distribution Network Skew.

From www.slideserve.com

PPT Introduction to CMOS VLSI Design Lecture 19 Design for Skew PowerPoint Presentation ID Clock Distribution Network Skew The two main design parameters. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins s i and s j in figure. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. clock distribution networks has become critical in maintaining the performance. Clock Distribution Network Skew.

From www.semanticscholar.org

[PDF] A 3D Low Jitter and Skew Clock Distribution Network Scheme Using LTCC Package Level Clock Distribution Network Skew Minimum and maximum timing constraints are. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth. because of the unbalanced delays in the clock distribution network, clock edges may arrive at clock pins. Clock Distribution Network Skew.

From www.slideserve.com

PPT Clock Distribution Topologies PowerPoint Presentation, free download ID3041698 Clock Distribution Network Skew Minimum and maximum timing constraints are. clock distribution networks has become critical in maintaining the performance growth. on a small chip, the clock distribution network is just a wire. derstand how clock distribution networks interact with data paths. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load.. Clock Distribution Network Skew.

From www.slideserve.com

PPT Improved Algorithms for LinkBased Nontree Clock Network for Skew Variability Reduction Clock Distribution Network Skew clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. The two main design parameters. derstand how clock distribution networks interact with data paths. And possibly an inverter for clk’. on a small chip, the clock distribution network is just a wire. because of the unbalanced delays in. Clock Distribution Network Skew.

From www.researchgate.net

Tree structure of a clock distribution network. Download HighResolution Scientific Diagram Clock Distribution Network Skew on a small chip, the clock distribution network is just a wire. clock distribution networks are subject to clock skew due to process, voltage, and temperature (pvt) variations and load. The two main design parameters. clock distribution networks has become critical in maintaining the performance growth. And possibly an inverter for clk’. derstand how clock distribution. Clock Distribution Network Skew.