Clock Gating Vhdl . dynamic power reduction by gating the clock. Just decide what gating style you want/need (and/or based,. These clocks are also sensitive to glitches,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. gated clocks contribute to clock skew and make device migration difficult. inserting clock gates in a vhdl design is easy. In most designs, data is loaded into registers very infrequently, but the clock signal continues to.

from www.bilibili.com

i've received an advice to avoid gated clock because it may cause problems with slacks and timing. inserting clock gates in a vhdl design is easy. dynamic power reduction by gating the clock. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. gated clocks contribute to clock skew and make device migration difficult. These clocks are also sensitive to glitches,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. Just decide what gating style you want/need (and/or based,.

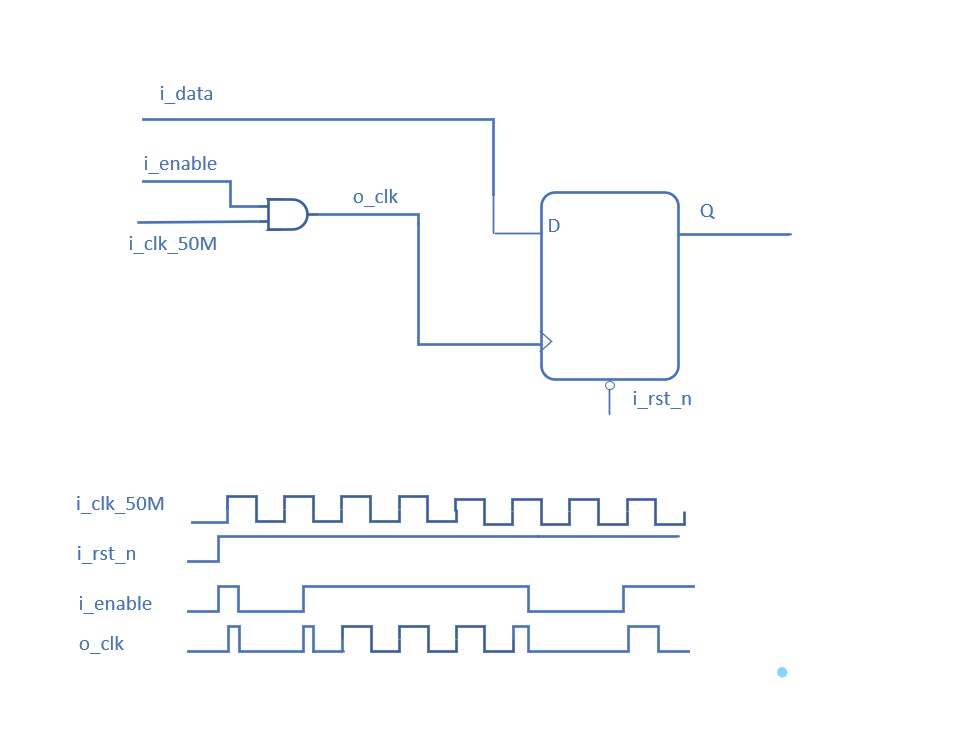

门控时钟(Clockgating) 哔哩哔哩

Clock Gating Vhdl These clocks are also sensitive to glitches,. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. These clocks are also sensitive to glitches,. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. gated clocks contribute to clock skew and make device migration difficult. inserting clock gates in a vhdl design is easy. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. dynamic power reduction by gating the clock. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. Just decide what gating style you want/need (and/or based,.

From mungfali.com

Clock Gating VLSI Clock Gating Vhdl Just decide what gating style you want/need (and/or based,. inserting clock gates in a vhdl design is easy. These clocks are also sensitive to glitches,. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. sequential clock gating provides significant power savings. Clock Gating Vhdl.

From www.semanticscholar.org

Figure 10 from A Review on Clock Gating Methodologies for power minimization in VLSI circuits Clock Gating Vhdl In most designs, data is loaded into registers very infrequently, but the clock signal continues to. These clocks are also sensitive to glitches,. Just decide what gating style you want/need (and/or based,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of. Clock Gating Vhdl.

From www.researchgate.net

3 Clock gating of the main clock to some component Download Scientific Diagram Clock Gating Vhdl i've received an advice to avoid gated clock because it may cause problems with slacks and timing. Just decide what gating style you want/need (and/or based,. inserting clock gates in a vhdl design is easy. dynamic power reduction by gating the clock. In most designs, data is loaded into registers very infrequently, but the clock signal continues. Clock Gating Vhdl.

From www.semanticscholar.org

Figure 1 from Complex clock gating with integrated clock gating logic cell Semantic Scholar Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. inserting clock gates in a vhdl design is easy. These clocks are also sensitive to glitches,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. . Clock Gating Vhdl.

From onlinedocs.microchip.com

Clock Gating Clock Gating Vhdl Just decide what gating style you want/need (and/or based,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. dynamic power. Clock Gating Vhdl.

From www.youtube.com

VHDL Assignment (Digital Clock with Alarm) YouTube Clock Gating Vhdl sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. Just decide what gating style you want/need (and/or based,. dynamic power reduction by gating the clock. if you just need a clock to drive another part of your. Clock Gating Vhdl.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation, free download ID3741296 Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. dynamic power reduction by gating the clock. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. Just decide what gating style you want/need (and/or based,. sequential clock gating provides. Clock Gating Vhdl.

From webdocs.cs.ualberta.ca

Gating the clock Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. i've received an advice to avoid gated clock because it may cause problems with slacks and timing.. Clock Gating Vhdl.

From embdev.net

vhdl input clock to output Clock Gating Vhdl Just decide what gating style you want/need (and/or based,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. These clocks are also sensitive. Clock Gating Vhdl.

From circuitdigest.com

Implementation of Basic Logic Gates using VHDL in ModelSim Clock Gating Vhdl sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. gated clocks contribute to clock skew and make device migration difficult. Just decide. Clock Gating Vhdl.

From www.chegg.com

Describe the clock divider circuit in VHDL using the Clock Gating Vhdl Just decide what gating style you want/need (and/or based,. dynamic power reduction by gating the clock. These clocks are also sensitive to glitches,. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. inserting clock gates in a vhdl design is easy. gated clocks contribute to clock skew and make device. Clock Gating Vhdl.

From www.youtube.com

lesson 34 Up Down Counter Synchronous Circuit using D Flip Flops in VHDL with and with reset Clock Gating Vhdl if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. sequential clock gating provides significant power savings because it not only switches off the clock. Clock Gating Vhdl.

From surf-vhdl.com

How to compute the frequency of a clock SurfVHDL Clock Gating Vhdl inserting clock gates in a vhdl design is easy. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. gated. Clock Gating Vhdl.

From www.slideserve.com

PPT Lecture 7 Power PowerPoint Presentation, free download ID4495903 Clock Gating Vhdl These clocks are also sensitive to glitches,. Just decide what gating style you want/need (and/or based,. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. inserting clock gates in a vhdl design is easy. i've received an advice to avoid gated clock because it may cause problems with slacks and timing.. Clock Gating Vhdl.

From www.slideserve.com

PPT Power Optimization for Clock Network with Clock Gate Cloning and FlipFlop Merging Clock Gating Vhdl These clocks are also sensitive to glitches,. gated clocks contribute to clock skew and make device migration difficult. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. inserting clock gates in a vhdl design is easy. dynamic power reduction by. Clock Gating Vhdl.

From www.youtube.com

Vhdl Basic Tutorial For Beginners About Three Input And Gates YouTube Clock Gating Vhdl inserting clock gates in a vhdl design is easy. gated clocks contribute to clock skew and make device migration difficult. dynamic power reduction by gating the clock. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. These clocks are also sensitive to glitches,. In most designs, data is. Clock Gating Vhdl.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Vhdl These clocks are also sensitive to glitches,. Just decide what gating style you want/need (and/or based,. dynamic power reduction by gating the clock. inserting clock gates in a vhdl design is easy. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable.. Clock Gating Vhdl.

From www.cnblogs.com

Clock Gating Checks 小勇5 博客园 Clock Gating Vhdl if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. gated clocks contribute to clock skew and make device migration difficult. Just decide what gating style you want/need (and/or based,. i've received an advice to avoid gated clock because it may cause. Clock Gating Vhdl.

From www.youtube.com

Integrated Clock Gating Cell ICG Cell in VLSI Clock Gating Cell Low Power Techniques in Clock Gating Vhdl dynamic power reduction by gating the clock. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. gated clocks contribute to clock skew and. Clock Gating Vhdl.

From www.bilibili.com

门控时钟(Clockgating) 哔哩哔哩 Clock Gating Vhdl sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. gated clocks contribute to clock skew and make device migration difficult. These clocks are also sensitive to glitches,. inserting clock gates in a vhdl design is easy. Just. Clock Gating Vhdl.

From www.engineersgarage.com

VHDL Tutorial 19 Designing a 4bit binary counter using VHDL Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. dynamic power reduction by gating the clock. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. These clocks are also sensitive to glitches,. Just decide what gating style you want/need. Clock Gating Vhdl.

From www.scribd.com

VHDL Code For Digital Clock On FPGA PDF Vhdl Field Programmable Gate Array Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. dynamic power reduction by gating the clock. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. inserting clock gates in a vhdl design is easy. i've received an. Clock Gating Vhdl.

From vlsimaster.com

Clock Gating VLSI Master Clock Gating Vhdl if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. gated clocks contribute to clock skew and make device migration difficult. inserting clock gates in a vhdl design is easy. These clocks are also sensitive to glitches,. In most designs, data is. Clock Gating Vhdl.

From www.elecfans.com

Clock Gating的特点、原理和初步实现电子发烧友网 Clock Gating Vhdl sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. dynamic power reduction by gating the clock. These clocks are also sensitive to glitches,. Just decide what gating style you want/need (and/or based,. gated clocks contribute to clock. Clock Gating Vhdl.

From www.slideserve.com

PPT VHDL Design Tips and Low Power Design Techniques PowerPoint Presentation ID458251 Clock Gating Vhdl These clocks are also sensitive to glitches,. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. if you just need a clock to drive another part of your logic in the fpga, the easy. Clock Gating Vhdl.

From www.slideserve.com

PPT PROCESSOR POWER SAVING CLOCK GATING PowerPoint Presentation, free download ID3741296 Clock Gating Vhdl sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. if you just need a clock to drive another part of. Clock Gating Vhdl.

From aijishu.com

Clock Gating之浅见 极术社区 连接开发者与智能计算生态 Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. Just decide what gating style you want/need (and/or based,. In most designs, data is loaded into registers very infrequently, but the clock signal continues to. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. These clocks are also sensitive. Clock Gating Vhdl.

From zhuanlan.zhihu.com

低功耗设计基础:Clock Gating 知乎 Clock Gating Vhdl dynamic power reduction by gating the clock. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. gated clocks contribute to clock skew and make device migration difficult. These clocks are also sensitive to glitches,. inserting clock. Clock Gating Vhdl.

From teamvlsi.com

Integrated Clock Gating (ICG) Cell in VLSI Team VLSI Clock Gating Vhdl Just decide what gating style you want/need (and/or based,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. if you just need a clock to drive another part of your logic in the fpga, the easy answer is. Clock Gating Vhdl.

From www.engineersgarage.com

VHDL Tutorial 15 Design a clocked SR latch (flipflop) using VHDL Clock Gating Vhdl In most designs, data is loaded into registers very infrequently, but the clock signal continues to. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. sequential clock gating provides significant power savings because it not only switches off the clock going to. Clock Gating Vhdl.

From finitron.ca

Finitron HDL Artistry Clock Gating Vhdl In most designs, data is loaded into registers very infrequently, but the clock signal continues to. These clocks are also sensitive to glitches,. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. if you just need a clock. Clock Gating Vhdl.

From www.elecfans.com

低功耗设计基础:Clock Gating电子发烧友网 Clock Gating Vhdl gated clocks contribute to clock skew and make device migration difficult. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. inserting clock gates in a vhdl design is easy. dynamic power reduction by gating the clock. These clocks are also. Clock Gating Vhdl.

From surf-vhdl.com

How to Measure Pulse Duration Using VHDL SurfVHDL Clock Gating Vhdl dynamic power reduction by gating the clock. i've received an advice to avoid gated clock because it may cause problems with slacks and timing. sequential clock gating provides significant power savings because it not only switches off the clock going to registers but also the datapath logic in the fanout of gated registers. if you just. Clock Gating Vhdl.

From ee.mweda.com

set_clock_gating_style命令使用 微波EDA网 Clock Gating Vhdl These clocks are also sensitive to glitches,. if you just need a clock to drive another part of your logic in the fpga, the easy answer is to use a clock enable. Just decide what gating style you want/need (and/or based,. inserting clock gates in a vhdl design is easy. i've received an advice to avoid gated. Clock Gating Vhdl.

From dxogultcc.blob.core.windows.net

How Does Clock Gating Work at Laurena Miller blog Clock Gating Vhdl i've received an advice to avoid gated clock because it may cause problems with slacks and timing. dynamic power reduction by gating the clock. inserting clock gates in a vhdl design is easy. gated clocks contribute to clock skew and make device migration difficult. In most designs, data is loaded into registers very infrequently, but the. Clock Gating Vhdl.