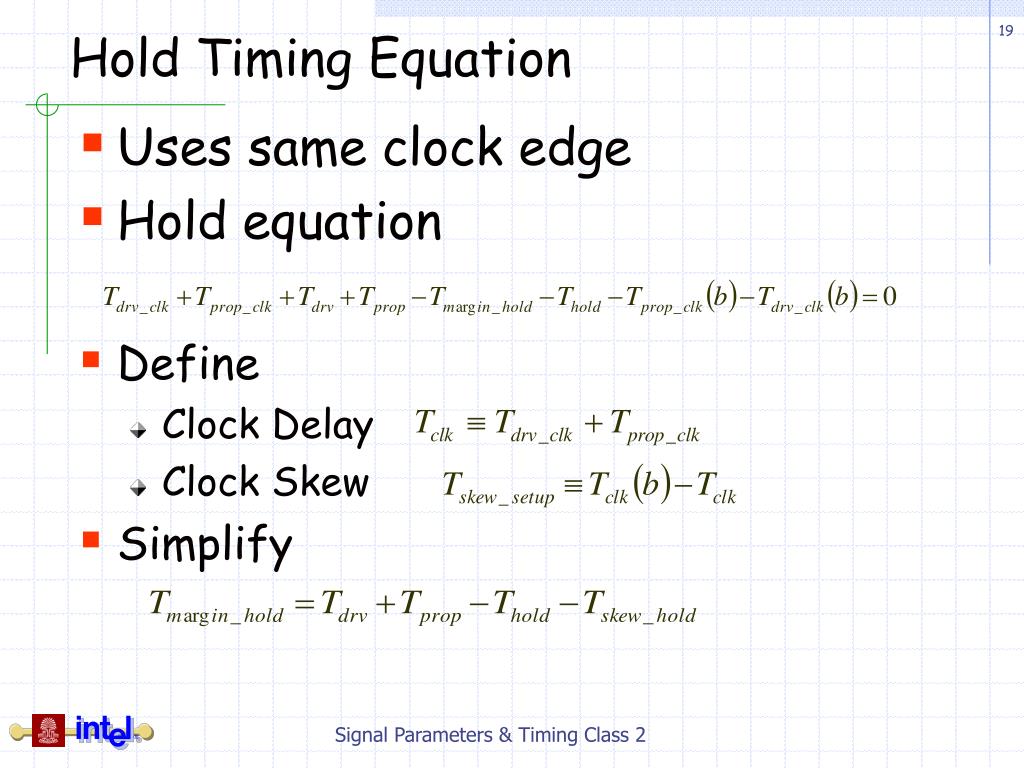

Setup Time Hold Time Clock To-Q Delay . Setup time (tsu) is the time that the data inputs must be valid before. setup and hold time equations. The input signal (into the flip flop) fails to change to a desired value fast enough. A hold time violation is likely to occur when. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. In a positive edge triggered flip. Violation in this case may. Hold time (thold) is the time that the data. timing metrics in sequential circuits. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up;

from www.slideserve.com

The input signal (into the flip flop) fails to change to a desired value fast enough. setup and hold time equations. Setup time (tsu) is the time that the data inputs must be valid before. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Violation in this case may. Hold time (thold) is the time that the data. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; A hold time violation is likely to occur when. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. In a positive edge triggered flip.

PPT Signal and Timing Parameters I Common Clock Class 2 PowerPoint

Setup Time Hold Time Clock To-Q Delay timing metrics in sequential circuits. In a positive edge triggered flip. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. A hold time violation is likely to occur when. Violation in this case may. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; Setup time (tsu) is the time that the data inputs must be valid before. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. timing metrics in sequential circuits. The input signal (into the flip flop) fails to change to a desired value fast enough. setup and hold time equations. Hold time (thold) is the time that the data.

From zhuanlan.zhihu.com

建立时间(setup time)和保持时间(hold time)详析 知乎 Setup Time Hold Time Clock To-Q Delay timing metrics in sequential circuits. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; Hold time (thold) is the time that the data.. Setup Time Hold Time Clock To-Q Delay.

From asic-soc.blogspot.com

ASICSystem on ChipVLSI Design Setup and hold time definition Setup Time Hold Time Clock To-Q Delay Violation in this case may. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. In a positive edge triggered flip. timing metrics in. Setup Time Hold Time Clock To-Q Delay.

From vlsi-soc.blogspot.com

VLSI SoC Design Sample Problem on Setup and Hold Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. setup and hold time equations. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Hold time (thold) is the time that the data. A. Setup Time Hold Time Clock To-Q Delay.

From newbedev.com

Understand the timing of Shift Register Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Setup time (tsu) is the time that the data inputs must be valid before. In a. Setup Time Hold Time Clock To-Q Delay.

From www.slideserve.com

PPT Signal and Timing Parameters I Common Clock Class 2 PowerPoint Setup Time Hold Time Clock To-Q Delay A hold time violation is likely to occur when. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. In a positive edge triggered flip. setup and hold time equations. Setup time (tsu) is the time that the data inputs must be valid before. hold time. Setup Time Hold Time Clock To-Q Delay.

From www.chegg.com

8. (a) Find the setup time, hold time and clocktoQ Setup Time Hold Time Clock To-Q Delay propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; setup and hold time equations. timing metrics in sequential circuits. Setup time (tsu) is the time that the data inputs must be valid before. A hold time violation is likely to occur when. the. Setup Time Hold Time Clock To-Q Delay.

From tech.tdzire.com

What are setup and hold timing checks ? What is setup and hold time Setup Time Hold Time Clock To-Q Delay timing metrics in sequential circuits. Setup time (tsu) is the time that the data inputs must be valid before. The input signal (into the flip flop) fails to change to a desired value fast enough. Violation in this case may. setup and hold time equations. Hold time (thold) is the time that the data. hold time is. Setup Time Hold Time Clock To-Q Delay.

From www.vlsi-expert.com

"Setup and Hold Time" Static Timing Analysis (STA) basic (Part 3a Setup Time Hold Time Clock To-Q Delay Violation in this case may. timing metrics in sequential circuits. Hold time (thold) is the time that the data. In a positive edge triggered flip. setup and hold time equations. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; hold time is defined. Setup Time Hold Time Clock To-Q Delay.

From www.edn.com

16 Ways To Fix Setup and Hold Time Violations EDN Setup Time Hold Time Clock To-Q Delay Violation in this case may. setup and hold time equations. timing metrics in sequential circuits. A hold time violation is likely to occur when. Hold time (thold) is the time that the data. Setup time (tsu) is the time that the data inputs must be valid before. In a positive edge triggered flip. the below series of. Setup Time Hold Time Clock To-Q Delay.

From vdocuments.mx

SETUP AND HOLD TIME DEFINITION · SETUP AND HOLD TIME Setup Time Hold Time Clock To-Q Delay Violation in this case may. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. In a positive edge triggered flip. timing metrics in sequential. Setup Time Hold Time Clock To-Q Delay.

From www.youtube.com

Reason for Setup and hold time in flip flop Setup and hold time Setup Time Hold Time Clock To-Q Delay Violation in this case may. Hold time (thold) is the time that the data. timing metrics in sequential circuits. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. The input signal (into the flip flop) fails to change to a desired value fast enough. the. Setup Time Hold Time Clock To-Q Delay.

From www.chegg.com

Solved In Fig. 7, given the setup time and hold time of a Setup Time Hold Time Clock To-Q Delay Violation in this case may. In a positive edge triggered flip. setup and hold time equations. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Hold time (thold) is the time that the data. propagation delay from rising edge of clock to new value at. Setup Time Hold Time Clock To-Q Delay.

From www.chegg.com

Solved 6. [12 pts] Assume that the setup time, DQ and CLKQ Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. In a positive edge triggered flip. setup and hold time equations. Violation in this case may. timing metrics in sequential circuits. hold time is defined as the minimum amount of time after the clock’s active. Setup Time Hold Time Clock To-Q Delay.

From www.youtube.com

Setup, Hold, Propagation Delay, Timing Errors, Metastability in FPGA Setup Time Hold Time Clock To-Q Delay In a positive edge triggered flip. setup and hold time equations. The input signal (into the flip flop) fails to change to a desired value fast enough. A hold time violation is likely to occur when. Violation in this case may. hold time is defined as the minimum amount of time after the clock’s active edge during which. Setup Time Hold Time Clock To-Q Delay.

From www.mdpi.com

Electronics Free FullText Timing Analysis and Optimization Method Setup Time Hold Time Clock To-Q Delay Violation in this case may. Hold time (thold) is the time that the data. A hold time violation is likely to occur when. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; Setup time (tsu) is the time that the data inputs must be valid before.. Setup Time Hold Time Clock To-Q Delay.

From www.chegg.com

Label setup time, hold time, clocktoQ propagation Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. Violation in this case may. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. The input signal (into the flip flop) fails to change to. Setup Time Hold Time Clock To-Q Delay.

From www.youtube.com

Can you calculate clock to output delay from setup time, hold time and Setup Time Hold Time Clock To-Q Delay Violation in this case may. The input signal (into the flip flop) fails to change to a desired value fast enough. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. propagation delay from rising edge of clock to new value at q time before clock edge. Setup Time Hold Time Clock To-Q Delay.

From zhuanlan.zhihu.com

建立时间(setup time)和保持时间(hold time)详析 知乎 Setup Time Hold Time Clock To-Q Delay Violation in this case may. The input signal (into the flip flop) fails to change to a desired value fast enough. Setup time (tsu) is the time that the data inputs must be valid before. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. A hold time. Setup Time Hold Time Clock To-Q Delay.

From www.slideserve.com

PPT Sequential Circuit Timing PowerPoint Presentation, free download Setup Time Hold Time Clock To-Q Delay timing metrics in sequential circuits. Violation in this case may. In a positive edge triggered flip. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative. Setup Time Hold Time Clock To-Q Delay.

From www.researchgate.net

Dependence of clocktoQ delay and setup time of a register on Setup Time Hold Time Clock To-Q Delay Setup time (tsu) is the time that the data inputs must be valid before. setup and hold time equations. The input signal (into the flip flop) fails to change to a desired value fast enough. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. A hold. Setup Time Hold Time Clock To-Q Delay.

From www.mdpi.com

Electronics Free FullText Timing Analysis and Optimization Method Setup Time Hold Time Clock To-Q Delay propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; In a positive edge triggered flip. A hold time violation is likely to occur when. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and.. Setup Time Hold Time Clock To-Q Delay.

From www.transtutors.com

(Solved) La 1 JO ? Cik • DFF Timing Parameters Setup And Hold Time Setup Time Hold Time Clock To-Q Delay Hold time (thold) is the time that the data. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; The input signal (into the flip flop) fails to change to a desired value fast enough. A hold time violation is likely to occur when. setup and. Setup Time Hold Time Clock To-Q Delay.

From tech.tdzire.com

What are setup and hold timing checks ? What is setup and hold time Setup Time Hold Time Clock To-Q Delay setup and hold time equations. Setup time (tsu) is the time that the data inputs must be valid before. The input signal (into the flip flop) fails to change to a desired value fast enough. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. A hold. Setup Time Hold Time Clock To-Q Delay.

From www.youtube.com

Setup time, Hold time and Metastability What's the origin? Can these Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Violation in this case may. A hold time violation is likely to occur when. Setup time. Setup Time Hold Time Clock To-Q Delay.

From www.bank2home.com

Setup And Hold Time Explained Setup Time Hold Time Clock To-Q Delay In a positive edge triggered flip. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; Violation in this case may. setup and hold time equations. Hold time (thold) is the time that the data. timing metrics in sequential circuits. the below series of. Setup Time Hold Time Clock To-Q Delay.

From mil-spec.tpub.com

Figure 14. Transition time, propagation delay time, data setup time Setup Time Hold Time Clock To-Q Delay In a positive edge triggered flip. Hold time (thold) is the time that the data. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. Setup time (tsu) is the time that the data inputs must be valid before. setup and hold time equations. hold time. Setup Time Hold Time Clock To-Q Delay.

From www.youtube.com

Flip Flop Timing Diagram Setup Time, Hold Time and Propagation Delay Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. In a positive edge triggered flip. Violation in this case may. setup and hold time equations. timing metrics in sequential circuits. hold time is defined as the minimum amount of time after the clock’s active. Setup Time Hold Time Clock To-Q Delay.

From tech.tdzire.com

What are setup and hold timing checks ? What is setup and hold time Setup Time Hold Time Clock To-Q Delay Setup time (tsu) is the time that the data inputs must be valid before. timing metrics in sequential circuits. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. Violation in this case may. In a positive edge triggered flip. The input signal (into the flip flop). Setup Time Hold Time Clock To-Q Delay.

From www.chegg.com

Solved Problem 1 Write down the approximate setup time, Setup Time Hold Time Clock To-Q Delay timing metrics in sequential circuits. setup and hold time equations. the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Setup time (tsu) is. Setup Time Hold Time Clock To-Q Delay.

From www.slideserve.com

PPT COMP541 FlipFlop Timing PowerPoint Presentation, free download Setup Time Hold Time Clock To-Q Delay hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Hold time (thold) is the time that the data. The input signal (into the flip flop) fails to change to a desired value fast enough. Violation in this case may. In a positive edge triggered flip. Setup time. Setup Time Hold Time Clock To-Q Delay.

From www.chegg.com

Solved Problem 3 Calculate the Setup and Hold time at Input Setup Time Hold Time Clock To-Q Delay timing metrics in sequential circuits. Setup time (tsu) is the time that the data inputs must be valid before. propagation delay from rising edge of clock to new value at q time before clock edge that ff needs to set up; The input signal (into the flip flop) fails to change to a desired value fast enough. A. Setup Time Hold Time Clock To-Q Delay.

From www.youtube.com

Setup Time and Hold Time of Flip Flop Explained Digital Electronics Setup Time Hold Time Clock To-Q Delay setup and hold time equations. Violation in this case may. Setup time (tsu) is the time that the data inputs must be valid before. Hold time (thold) is the time that the data. The input signal (into the flip flop) fails to change to a desired value fast enough. the below series of images.hope these set of above. Setup Time Hold Time Clock To-Q Delay.

From tech.tdzire.com

What are setup and hold timing checks ? What is setup and hold time Setup Time Hold Time Clock To-Q Delay Violation in this case may. A hold time violation is likely to occur when. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. In a positive edge triggered flip. Hold time (thold) is the time that the data. timing metrics in sequential circuits. setup and. Setup Time Hold Time Clock To-Q Delay.

From www.slideserve.com

PPT Sequential Ckts, Latches and Timing Issues PowerPoint Setup Time Hold Time Clock To-Q Delay the below series of images.hope these set of above images, clearly distinguishes what’s a positive latch, what’s a negative latch and. Hold time (thold) is the time that the data. Violation in this case may. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Setup time. Setup Time Hold Time Clock To-Q Delay.

From www.semanticscholar.org

Figure 1 from Setup time, hold time and clocktoQ delay computation Setup Time Hold Time Clock To-Q Delay A hold time violation is likely to occur when. hold time is defined as the minimum amount of time after the clock’s active edge during which data must be stable. Setup time (tsu) is the time that the data inputs must be valid before. Hold time (thold) is the time that the data. propagation delay from rising edge. Setup Time Hold Time Clock To-Q Delay.